Способ выполнения машинной команды, компьютерная система и машиночитаемый носитель, обеспечивающие расчет расстояния от положения в основной памяти до границы блока основной памяти

Иллюстрации

Показать всеИзобретение относится к средствам расчета расстояния от положения в основной памяти до границы блока основной памяти. Технический результат заключается в обеспечении обработки данных вблизи границ памяти. Получают машинную команду, которая включает: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию Load Count to Block Boundary, предназначенную для расчета расстояния от положения в основной памяти до границы блока основной памяти; поле регистра, используемое для обозначения регистра, причем регистр включает первый операнд и по меньшей мере одно поле для указания положения второго операнда, причем второй операнд включает по меньшей мере часть указанного блока основной памяти. Выполняют машинную команду для выполнения указанной операции. Определяют расстояние от положения второго операнда до границы блока основной памяти, включающее подсчет процессором количества байт от положения второго операнда до границы блока основной памяти. Размещают значение, представляющее указанное расстояние и являющееся результатом выполнения операции Load Count to Block Boundary, в первом операнде. 3 н. и 17 з.п. ф-лы, 17 ил.

Реферат

Предпосылки создания изобретения

[001] Аспект данного изобретения относится, в общем, к обработке данных, и в частности к обработке, которая предусматривает границы памяти.

[002] Обработка данных включает в себя различные типы обработки, в том числе обработку текста или другие типы обработки. Во время обработки данных часто необходимо выполнять специальное манипулирование, когда обрабатываемые данные находятся вблизи заданной границы памяти. Представленные на сегодняшний день команды и/или техники, связанные с обработкой вблизи границы памяти, зачастую являются неэффективными или проблематичными.

КРАТКОЕ ИЗЛОЖЕНИЕ

[003] Для устранения недостатков уровня техники предложен машиночитаемый носитель данных, в котором хранятся команды, считываемые и выполняемые обрабатывающим устройством в центральном процессорном устройстве для выполнения способа, включающего получение процессором машинной команды для выполнения, причем машинная команда определена для выполнения компьютером согласно архитектуре компьютера и включает: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию Load Count to Block Boundary, предназначенную для расчета расстояния от положения в основной памяти до границы блока основной памяти; поле регистра, используемое для обозначения регистра, причем регистр включает первый операнд; и по меньшей мере одно поле для указания положения второго операнда, причем второй операнд включает по меньшей мере часть указанного блока основной памяти. Кроме того, способ включает выполнение машинной команды для выполнения указанной операции Load Count to Block Boundary, включающее определение расстояния от положения второго операнда до границы блока основной памяти, включающее подсчет процессором количества байт от положения второго операнда до границы блока основной памяти, и размещение значения, представляющего указанное расстояние и являющееся результатом выполнения операции Load Count to Block Boundary, в первом операнде

[004] Также предложены соответствующие способ и компьютерная система.

[005] С помощью методик согласно данному изобретению реализуются и другие особенности и преимущества. Другие варианты воплощения и аспекты изобретения излагаются здесь подробно и считаются частью формулы изобретения.

КРАТКОЕ ОПИСАНИЕ И НЕСКОЛЬКО ПРЕДСТАВЛЕНИЙ ЧЕРТЕЖЕЙ

[006] Один или более аспектов данного изобретения выделены особо и явно заявлены как примеры в формуле изобретения в конце описания. Вышеуказанное и другие цели, признаки и преимущества изобретения понятны из следующего подробного описания с помощью сопровождающих чертежей, в которых:

На ФИГ. 1 изображен один из примеров вычислительной среды, включающей и использующей один или более аспектов данного изобретения;

На ФИГ.2А изображен другой пример вычислительной среды, включающей и использующей один или более аспектов данного изобретения;

На ФИГ.2Б изображены дополнительные подробности памяти ФИГ. 2а в соответствии с аспектом настоящего изобретения;

На ФИГ.3 изображен один из вариантов воплощения формата команды Load Count to Block Boundary в соответствии с аспектом настоящего изобретения;

На ФИГ.4 изображен один из вариантов воплощения логики, связанной с командой Load Count to Block Boundary в соответствии с аспектом данного изобретения;

На ФИГ.5А изображен один из примеров по меньшей мере части блока памяти, для которого обеспечивается счет (расстояние), в соответствии с аспектом данного изобретения;

На ФИГ.5Б изображен один из примеров регистра общего назначения, содержащего расстояние, в соответствии с аспектом данного изобретения;

На ФИГ.6 изображен пример файла регистра в соответствии с аспектом данного изобретения;

На ФИГ.7 изображен один из вариантов воплощения компьютерного программного продукта, включающего один или более аспектов данного изобретения;

На ФИГ.8 изображен один из вариантов воплощения главной (хост) компьютерной системы, включающей и использующей один или более аспектов данного изобретения;

На ФИГ.9 изображен другой пример компьютерной системы, включающей и использующей один или более аспектов данного изобретения;

На ФИГ.10 изображен еще один пример компьютерной системы, содержащей компьютерную сеть, включающую и использующую один или более аспектов данного изобретения;

На ФИГ.11 изображен один из вариантов воплощения различных элементов компьютерной системы, включающей и использующей один или более аспектов данного изобретения;

На ФИГ.12А изображен один из вариантов воплощения исполнительного устройства компьютерной системы согласно ФИГ.11, включающего и использующего один или более аспектов данного изобретения;

На ФИГ.12Б изображен один из вариантов воплощения устройства ветвления компьютерной системы согласно ФИГ.11, включающего и использующего один или более аспектов данного изобретения;

На ФИГ.12В изображен один из вариантов воплощения устройства загрузки/сохранения компьютерной системы согласно ФИГ.11, включающего и использующего один или более аспектов данного изобретения; и

На ФИГ.13 изображен один из вариантов воплощения эмулируемой хост-компьютерной системы, включающей и использующей один или более аспектов данного изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

[007] В соответствии с аспектом настоящего изобретения предоставляется средство для определения расстояния до заданной границы в памяти от заданного положения (например, адреса памяти). Граница в памяти является, например, окончанием блока основной памяти (также называемой здесь основным запоминающим устройством). Блок основной памяти является любым блоком памяти заданного размера. Заданный размер также называют границей блока. Блок основной памяти включает данные, такие как символьные данные, целые данные или другие типы данных.

[008] Символьные данные включают, но не ограничиваются: алфавитные символы на любом языке; числовые цифры; знаки препинания; и/или другие символы. Символьные данные могут быть или не быть строками данных. С символьными данными связаны стандарты, примеры которых включают, но не ограничиваются: ASCII (American Standard Code for Information Interchange, американский стандартный код для информационного обмена); Unicode, включая, но не ограничиваясь, UTF (Unicode Transformation Format, формат трансформации Юникода) 8; UTF 16 и т.п.

[009] В отдельном примере предоставляется команда Load Count to Block Boundary (LCBB), которая предоставляет количество байт данных до заданной границы в памяти от заданного адреса в памяти. Для вычисления количества бит (называемого здесь расстоянием) используется размер границы. Размер границы может быть задан командой явно (напр., значение переменной в тексте команды, фиксированное значение в тексте команды, вкодированное в код операции, граница на основе регистра, заданная в команде, и т.д.); или размер границы может динамически определяться машиной. Например, команда задает тип границы, такой как граница страницы или кэша, и машина определяет размер строки кэша или страницы, либо по предопределенному значению, либо динамически на основе информации (напр., поиска, например, в буфере динамической трансляции адресов для определения размера страницы).

[0010] Как пример, команда Load Count to Block Boundary предоставляет количество байт данных, которые могут быть или были загружены из памяти, например, в регистр без пересечения заданной границы памяти. Регистр может быть векторным регистром или любым другим типом регистра.

[0011] Векторный регистр (также называемый вектором) включает один или более элементов, а каждый элемент векторного регистра (также называемый вектором) имеет длину, например, один, два или четыре байта. Далее, векторный операнд является, к примеру, операндом типа SIMD (Single Instruction, Multiple Data - одна команда, много данных), имеющим множество элементов. В других вариантах реализации элементы могут иметь другие размеры; а векторный операнд не обязательно типа SIMD, и/или может включать один элемент.

[0012] Один из вариантов осуществления вычислительной среды, включающей и использующей один или более аспектов данного изобретения, описаны при помощи ФИГ.1. Вычислительная среда 100 включает, например, процессор 102 (например, центральное процессорное устройство), память 104 (например, главная память) и одно или более устройств ввода-вывода (I/O) и/или интерфейсов 106, соединенных между собой посредством, например, одной или более шин 108 и/или других соединений.

[0013] В одном примере, процессор 102 основан на z/Architecture, предложенной корпорацией International Business Machines, и является частью сервера, такого как сервер System z, который также предложен корпорацией International Business Machines и реализовывает z/Architecture. Один из вариантов воплощения z/Architecture описан в публикации IBM®, озаглавленной "z/Architecture Principles of Operation" ("z/Architecture. Принципы работы"), публикация IBM® номер SA22-7832-08, девятое издание, август 2010 г., которая включается сюда по ссылке во всей ее целостности. В одном примере, процессор реализовывает операционную систему, такую как z/OS, также предложенную корпорацией International Business Machines. IBM®, Z/ARCHITECTURE® и Z/OS® являются зарегистрированными торговыми марками корпорации International Business Machines, Армонк, Нью Йорк, США. Другие названия, используемые в данном описании, могут быть зарегистрированными торговыми марками, торговыми марками, или названиями продуктов корпорации International Business Machines или других компаний.

[0014] В дополнительном варианте воплощения, процессор 102 основан на Power Architecture, предложенной корпорацией International Business Machines. Один вариант воплощения Power Architecture описан в "Power ISA™ Version 2.06 Revision В," корпорации International Business Machines, 23 июля 2010 г., который включается сюда по ссылке во всей его целостности. POWER ARCHITECTURE® является зарегистрированной торговой маркой корпорации International Business Machines.

[0015] В еще одном дополнительном варианте воплощения процессор 102 основан на архитектуре Intel, предложенной корпорацией Intel. Один вариант воплощения Intel архитектуры описан в "Intel 64 and IA-32 Architectures Developer's Manual: Vol.2B, Instructions Set Reference, A-L" ("Архитектуры Intel® 64 и IA-32. Руководство разработчика: т.2B, справочник по набору команд, A-L"), порядковый номер 253666-041US, декабрь 2011 г., и "Intel® 64 and IA-32 Architectures Developer's Manual: Vol.2B, Instructions Set Reference, M-Z" ("Архитектуры Intel® 64 и IA-32. Руководство разработчика: т.2B, справочник по набору команд, M-Z"), порядковый номер 253667-041 US, декабрь 2011 г., каждое из которых включается сюда по ссылке во всей его целостности. Intel® является зарегистрированной торговой маркой корпорации Intel, Санта-Клара, Калифорния.

[0016] Другой вариант воплощения вычислительной среды, включающей и использующей один или более аспектов данного изобретения, описан при помощи ФИГ.2А. В данном примере, вычислительная среда 200 включает, например, собственное центральное процессорное устройство 202, память 204, и одно или более устройств ввода-вывода и/или интерфейсов 206, соединенных между собой посредством, например, одной или более шин 208 и/или других соединений. Например, вычислительная среда 200 может включать процессор PowerPC, сервер pSeries или сервер xSeries, предложенные корпорацией International Business Machines, Армонк, Нью Йорк; HP Superdome с процессорами Intel Itanium II, предложенными Hewlett Packard Co., Пало-Альто, Калифорния; и/или другие машины, основанные на архитектуре, предложенной корпорацией International Business Machines, Hewlett Packard, Intel, Oracle, или другими.

[0017] Собственное центральное процессорное устройство 202 содержит один или более собственных регистров 210, такие как один или более регистров общего назначения и/или один или более регистров специального назначения, использующихся при обработке внутри среды. Эти регистры содержат сведения, которые представляют состояние среды в любой отдельный момент времени.

[0018] Кроме того, собственное центральное процессорное устройство 202 выполняет команды и код, хранящиеся в памяти 204. В отдельном примере центральное процессорное устройство выполняет код эмулятора 212, хранящийся в памяти 204. Этот код задействует вычислительную среду, настроенную на одной архитектуре для эмуляции другой архитектуры. Например, код эмулятора 212 позволяет машинам, основанным на архитектурах, отличных от z/Architecture, таких так процессоры PowerPC, серверы pSeries, серверы xSeries, серверы HP Superdome или другие, эмулировать z/Architecture и выполнять программное обеспечение и команды, разработанные на основе z/Architecture.

[0019] Дальнейшие подробности касательно кода эмулятора 212 описаны при помощи ФИГ. 2Б. Гостевые команды 250 включают программные команды (напр., машинные команды), которые были разработаны для выполнения в архитектуре иной, нежели таковая собственного ЦПУ 202. Например, гостевые команды 250 могли быть разработаны для выполнения на процессоре 102 z/Architecture, но вместо этого эмулируются на собственном ЦПУ 202, которое может быть, например, процессором Intel Itanium II. В одном из примеров код эмулятора 212 включает модуль считывания команд 252 для получения одной или более гостевых команд 250 из памяти 204 и опционального обеспечения локальной буферизации полученных команд. Он включает также программу трансляции команд 254 для определения типа гостевой команды, которая была получена, и для трансляции гостевой команды в одну или более соответствующих собственных команд 256. Эта трансляция включает, например, идентификацию функции для выполнения гостевой командой и выбор собственной команды (команд), выполняющих эту функцию.

[0020] Далее, эмулятор 212 включает программу управления эмуляцией 260, заставляющую собственные команды выполняться. Программа управления эмуляцией 260 может заставить собственное ЦПУ 202 выполнить программу собственных команд, которые эмулируют одну или более ранее полученных гостевых команд, и, по завершению этого выполнения, вернуть управление программе считывания команд для эмуляции получения следующей гостевой команды или группы гостевых команд. Выполнение собственных команд 256 может включать загрузку данных в регистр из памяти 204; запись данных обратно в память из регистра; или выполнение некоторого типа арифметической или логической операции, как определено программой трансляции.

[0021] Каждая программа, например, реализована в программном обеспечении, которое хранится в памяти и выполняется собственным центральным процессорным устройством 202. В других примерах одна или более программ или операций могут быть реализованы в микропрограммном, аппаратном, программном обеспечении или в некоторой их комбинации. Регистры эмулируемого процессора могут эмулироваться с помощью регистров 210 собственного ЦПУ или с помощью ячеек в памяти 204. В вариантах реализации гостевые команды 250, собственные команды 256 и код эмулятора 212 могут находиться в одной памяти или могут быть рассредоточены по различным запоминающим устройствам.

[0022] В данном контексте, микропрограмма включает, напр., микрокод, милликод и/или макрокод процессора. Она включает, например, команды аппаратного уровня и/или структуры данных, используемые в реализации машинного кода высокого уровня. В одном варианте реализации она включает, например, проприетарный код, который обычно поставляется как микрокод, который включает достоверное программное обеспечение или микрокод, специфичный для нижележащего аппаратного обеспечения, и управляет доступом операционной системы к системному аппаратному обеспечению.

[0023] В одном примере гостевая команда 250, которая считывается, транслируется и выполняется, является командой, описываемой здесь. Команда одной архитектуры (напр., для z/Architecture) считывается из памяти, транслируется и представляется в виде последовательности собственных команд 256 другой архитектуры (напр., PowerPC, pSeries, xSeries, Intel и т.п.). Затем эти собственные команды выполняются.

[0024] Как описано здесь, команды Load Count to Block Boundary могут быть реализованы как часть различных архитектур, включая, но не ограничиваясь, z/Architecture, Power, Intel и т.д. Хотя здесь описывается реализация для z/Architecture, команда и один или более аспектов данного изобретения могут основываться на многих других архитектурах. z/Architecture является только одним из примеров.

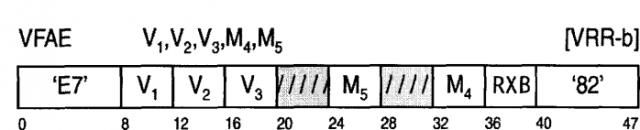

[0025] Один вариант воплощения команды Load Count to Block Boundary показан на ФИГ.3. В одном примере, команда Load Count to Block Boundary 300 содержит поля кода операции 302а (например, биты 0-7), 302b (например, биты 40-47), обозначающие операцию Load Count to Block Boundary; поле регистра 304 (например, биты 8-11), использующееся для задания регистра общего назначения (R1); индексное поле (Х2) 306 (например, биты 12-15); базовое поле (В2) 308 (например, биты 16-19); поле смещения (D2) 310 (например, биты 20-31); и поле маски (М3) 312 (например, биты 32-35). Каждое из полей 304-312 в одном примере отделено и независимо от поля (полей) кода операции. Далее, в одном варианте реализации они отделены и независимы друг от друга; однако в других вариантах более чем одно поле могут комбинироваться. Дальнейшие сведения об использовании этих полей описываются ниже.

[0026] В одном из примеров выбранные биты (напр., первые два бита) кода операции, заданные полем кода операции 302а, определяют длину и формат команды. В этом частном примере длина равна трем полусловам, а формат является регистрово-индексной операцией сохранения с расширенным полем кода операции.

[0027] Нижний индекс, связанный с полем команды, обозначает операнд, к которому применяется поле. Например, нижний индекс 1, связанный с R1, обозначает первый операнд и так далее. Регистровый операнд равен одному регистру по длине, которая составляет, например, 128 бит.

[0028] В одном примере, в команде операции регистро-индексного сохранения, содержимое регистров общего назначения, определенное полями Х2 и B2, прибавляется к содержимому поля D2 для получения адреса второго операнда. Смещение D2 для команды Load Count to Block Boundary рассматривается как 12-битное целое без знака, в одном примере. Адрес второго операнда используется для указания положения в главной памяти; однако, он не используется для адресации данных, в данном варианте воплощения.

[0029] Поле М3 в одном из вариантов осуществления определяет код, который используется для сообщения ЦПУ о размере границы блока для вычисления количества возможных байт для загрузки, без пересечения границы памяти. Если определено зарезервированное значение, обнаруживается исключение определения. Примерные коды и соответствующие значения следующие:

[0030]

| Код | Граница |

| 0 | 64 байта |

| 1 | 128 байт |

| 2 | 256 байт |

| 3 | 512 байта |

| 4 | 1 кбайт |

| 5 | 2 кбайта |

| 6 | 4 кбайта |

[0031] В другом примере размер границы не включен в команду, а вместо этого динамически определяется процессором, выполняющим команду. Например, поле М3 определяет тип границы (напр., строка кэша, страница и т.п.), и на основе типа и одной или более характеристик процессора (напр., размер строки кэша для процессора; размер страницы для процессора; и т.п.), процессор определяет границу. К примеру, на основе типа, процессор использует постоянный размер для границы (напр., предопределенный постоянный размер строки кэша или страницы для процессора), или, на основе типа, процессор определяет границу. Например, если тип - граница страницы, процессор ищет начальный адрес в буфере динамической трансляции адресов (Translation Look-Aside Buffer, TLB) и определяет границу страницы из него. Другие примеры также существуют. Например, тип может предоставляться другим полем команды или из директивы вне команды.

[0032] При выполнении одной из реализации команды Load Count to Block Boundary, двоичное беззнаковое целое (напр., 64-битное), содержащее число бит, которое возможно загрузить от положения второго операнда без пересечения заданной границы блока, ограниченное, например, размером вектора для загрузки (напр., 16), помещается в регистр общего назначения, определенный в первом операнде.

[0033] В результате выполнения команды опциональный код состояния устанавливается, например, таким:

[0034] 0 - Операнд один равен шестнадцати

[0035] 1 -

[0036] 2 -

[0037] 3 - Операнд один меньше шестнадцати

[0038] В приведенном выше примере команды, адрес второго операнда определяется значением индексного регистра (Х2)+значение базового регистра (В2)+смещение (D2); однако в других реализациях он предоставляется значением регистра; адресом команды+отступ, заданный в тексте команды; значением регистра+смещение; или значением регистра+значение индексного регистра; это лишь некоторые примеры.

[0039] Дальнейшие подробности воплощения обработки команды Vector Count to Block Boundary описаны при помощи ФИГ. 4. В одном примере процессор вычислительной среды следует данной логике.

[0040] В одном из вариантов воплощения вначале создается маска границы (BdyMask), которая используется для определения близости к заданной границе, ШАГ 400. Чтобы создать маску, в одном примере берется двоичное дополнительное отрицание от размера границы (BdySize) 402, создающее маску границы 404 (напр., BdyMask=0-BdySize). Размер границы предоставляется, в одном примере, командой (напр., полем М3); а в другом примере он определяется машиной согласно данной заявке.

[0041] После этого вычисляется начальный адрес, который обозначает ячейку в памяти, из которой должен начинаться счет, ШАГ 410. К примеру, начальный адрес 412 может быть предоставлен значением регистра; адресом команды плюс отступ, заданный в тексте команды; значением регистра плюс смещение; значением регистра плюс значение индексного регистра; или значением регистра плюс значение индексного регистра плюс смещение. В предоставленной здесь команде начальный адрес предоставляется полем Х2, полем В2 и полем D2. То есть, содержимое регистров, заданных полями Х2 и В2, прибавляется к смещению, указанному D2 для получения начального адреса. Вышеуказанные способы вычисления начального адреса являются лишь примерами; другие примеры также возможны.

[0042] Далее, вычисляется конечный адрес, указывающий положение, на котором остановить счет, ШАГ 420. Вводными для этого вычисления являются, например, размер границы 402, начальный адрес 412, размер вектора (vec_size) 414 и маска границы 404. Размер вектора представляет собой размер выбранного векторного регистра или другого регистра (например, в байтах; например, 16). Регистр представляет собой, например, регистр, в который данные могут быть загружены. В одном из примеров конечный адрес 422 вычисляется следующим образом:

[0043] EndAddress=min(StartAddress+(BdySize - (StartAddress & ¬BdyMask)), StartAddress+vec_size).

[0044] Затем, вычисляется расстояние, ШАГ 430. Например, расстояние=EndAddress 422 - StartAddress 412. В дополнительном примере, расстояние может быть вычислено с начального адреса и без использования конечного адреса. В этом примере, расстояние=min(16, BdySize - (StartAddress И ¬BdyMask)), где 16 представляет собой размер векторного регистра (или другого регистра) в байтах. В другом примере, могут использоваться другие размеры вектора.

[0045] Один из примеров по меньшей мере части блока 500 памяти изображен на ФИГ. 5А. Блок 500 памяти включает данные от выбранного адреса 502 до заданной границы 504. Как показано, никакие данные не считаются или не загружаются после границы, обозначенной пунктирной вертикальной линией 504. Ячейки после границы недоступны, и не делается никаких исключений. Далее, счет расстояния от выбранного адреса до заданной границы, определенный в соответствии с аспектом данного изобретения, сохраняется в регистре общего назначения 510, пример которого изображен на ФИГ.5Б. Как показано в этом примере, расстояние представляет собой 13 шестнадцатеричное, и поэтому OD сохраняется в регистре общего назначения 510, указывая, что 13 байт данных были подсчитаны и могут быть сохранены в векторном регистре.

[0046] Описанное выше представляет собой один из примеров команды счета, используемой для определения расстояния от заданного адреса до заданной границы. Может быть представлено предупреждение, если заданный адрес находится недалеко от границы, что, возможно, потребует специальной обработки.

[0047] Как один пример, команда Load Count to Block Boundary используется для определения того, как много байтов данных было загружено в регистр, такой как векторный регистр. Этот подсчет (расстояние) может быть использован в другой обработке.

[0048] В одном из вариантов воплощения, регистр, который загружен и для которого получен счет, представляет собой векторный регистр, являющийся частью векторного средства. Векторное средство предоставляет, например, векторы постоянного размера в пределах от одного до шестнадцати элементов. Каждый вектор содержит данные, которые обрабатываются векторными командами, определенными этим средством. В одном из вариантов реализации, если вектор составлен из нескольких элементов, то каждый элемент обрабатывается параллельно с другими элементами. Завершения команды не происходит, пока не будет завершена обработка всех элементов.

[0049] Как один из примеров, есть 32 векторных регистра, а другие типы регистров могут быть отображены на квадрант векторных регистров. К примеру, как изображено на ФИГ. 6, если есть файл регистра 600, который содержит 32 векторных регистра 602, и каждый регистр имеет 128 бит в длину, то 16 регистров с плавающей точкой 604, которые имеют 64 бит в длину, могут быть наложены на векторные регистры. Таким образом, к примеру, когда регистр с плавающей точкой 2 изменяется, то векторный регистр 2 также изменяется. Другие отображения для других типов регистров также возможны.

[0050] В данном контексте, термины "память", "главная память", "запоминающее устройство" и "главное запоминающее устройство" используются как взаимозаменяемые, если не указано иное, явным образом или неявно по контексту.

[0051] Дополнительные детали, касающиеся векторного средства, включая примеры команд, представлены ниже как часть этого Подробного описания.

[0052] Как оценят специалисты в данной области техники, один или больше аспектов настоящего изобретения могут быть воплощены в виде системы, способа или компьютерного программного продукта. Соответственно, один или больше аспектов настоящего изобретения могут принимать форму целиком аппаратного варианта осуществления, целиком программного варианта осуществления (содержащего аппаратно-программное обеспечение, резидентное программное обеспечение, микрокод и т.д.) или варианта осуществления, сочетающего программные и аппаратные особенности, которые все могут в целом именоваться в описании "схемой", "модулем" или "системой". Кроме того, один или больше аспектов настоящего изобретения могут принимать форму компьютерного программного продукта, воплощенного в одной или нескольких машиночитаемых средах, в которых записан машиночитаемый программный код.

[0053] Может использоваться любое сочетание одной или нескольких машиночитаемых сред. Машиночитаемой средой может являться машиночитаемая запоминающая среда (носитель данных). Машиночитаемой запоминающей средой может являться, например, без ограничения электронная, магнитная, оптическая, электромагнитная, инфракрасная или полупроводниковая система, аппаратура или устройство или любое применимое сочетание перечисленного. Более конкретные примеры (неисчерпывающий список) машиночитаемой запоминающей среды включают: электрическое соединение, содержащее один или несколько проводов, портативный компьютерный диск, жесткий диск, оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ), стираемое программируемое постоянное запоминающее устройство (СППЗУ или флэш-память), оптическое волокно, портативное постоянное запоминающее устройство на компакт-диске (CD-ROM), оптическое запоминающее устройство, магнитное запоминающее устройство или любое применимое сочетание перечисленного. В контексте настоящего документа машиночитаемой запоминающей средой может являться любая материальная среда, в которой содержится или хранится программа для использования системой, аппаратурой или устройством выполнения команд или применительно к ним.

[0054] Как показано на ФИГ.7, в одном из примеров компьютерный программный продукт 700 содержит, например, одну или несколько не-временных машиночитаемых запоминающих сред 702 для хранения в них машиночитаемого программного кода или логики 704 для обеспечения и реализации одного или нескольких аспектов настоящего изобретения.

[0055] Программный код, воплощенный в машиночитаемой среде, может передаваться с использованием соответствующей среды, включая без ограничения беспроводную, проводную среду, оптоволоконный кабель, ВЧ-среду и т.д. или любое применимое сочетание перечисленного.

[0056] Компьютерный программный код для выполнения операций, для одного или более аспектов настоящего изобретения, может быть записан на одном или нескольких языках программирования в любом сочетании, включая объектно-ориентированный язык программирования, такой как Java, Smalltalk, C++ и т.п., и традиционных процедурных языках программирования, таких как "С" и языки ассемблера или аналогичные языки программирования. Программный код может целиком выполняться в пользовательском компьютере, частично в пользовательском компьютере, в качестве автономного пакета программного обеспечения, частично в пользовательском компьютере и частично в удаленном компьютере или целиком в удаленном компьютере или сервере. В случае последнего сценария удаленный компьютер может быть соединен с пользовательским компьютером посредством сети любого типа, включая локальную вычислительную сеть (ЛВС) или глобальную вычислительную сеть (ГВС), или может быть установлено соединение с внешним компьютером (например, по сети Интернет с использованием поставщика услуг Интернет).

[0057] Один или более аспектов настоящего изобретения описаны со ссылкой на структурные схемы и/или блок-схемы способов, оборудования (систем) и компьютерных программных продуктов в соответствии с воплощениями настоящего изобретения. Подразумевается, что каждый блок на структурных схемах и/или блок-схемах и сочетания блоков на структурных схемах и/или блок-схемах могут быть реализованы посредством команд управления компьютерной программой. Эти команды управления компьютерной программой могут передаваться процессору универсального компьютера, специализированного компьютера или другой программируемого аппаратуры для обработки данных с целью формирования механизма, в котором команды, выполняемые посредством процессора компьютера или другого программируемого оборудования обработки данных, создают средство реализации функций/действий, обозначенных блоком или блоками на структурных схемах и/или блок-схемах.

[0058] Эти команды управления компьютерной программой также могут храниться в машиночитаемой среде, которая способна предписывать компьютеру, другому программируемому оборудованию обработки данных или другим устройствам действовать конкретным способом, в результате чего команды, хранящиеся в машиночитаемой среде, формируют продукт, содержащий команды, в которых реализуется функция/действие, обозначенное блоком или блоками на структурных схемах и/или блок-схемах.

[0059] Команды управления компьютерной программой также могут загружаться в компьютер, другое программируемое оборудование обработки данных или другие устройства, чтобы инициировать выполнение последовательности оперативных шагов компьютером, другим программируемым оборудованием или другими устройствами с целью формирования реализованного в компьютере процесса, при этом команды, выполняемые компьютером или другим программируемым оборудованием, обеспечивают процессы реализации функций/действий, обозначенных блоком или блоками на структурных схемах и/или блок-схемах.

[0060] Приведенные на чертежах структурные схемы и блок-схемы иллюстрируют архитектуру, функциональные возможности и действие возможных вариантов реализации систем, способов и компьютерных программных продуктов согласно различным вариантам осуществления одного или более аспектов настоящего изобретения. В связи с этим каждым блоком на структурных схемах или блок-схемах может быть представлен определенный модуль, сегмент или часть кода, которая содержит одну или несколько выполняемых команд для реализации заданной логической функции(-й). Следует также отметить, что в некоторых альтернативных вариантах реализации указанные в блоке функции могут выполняться не в том порядке, в котором они представлены на чертежах. Например, функции, указанные двумя последовательно показанными блоками, в действительности, могут выполняться преимущественно одновременно, или функции иногда могут выполняться в обратном порядке в зависимости от соответствующих функциональных возможностей. Следует также отметить, что каждый блок на блок-схемах и/или структурных схемах и сочетания блоков на блок-схемах и/или структурных схемах могут быть реализованы посредством специализированных аппаратных систем, выполняющих заданные функции или действия, или посредством сочетаний специализированных аппаратных систем и компьютерных команд.

[0061] Помимо вышесказанного, одна или несколько особенностей настоящего изобретения может обеспечиваться, предлагаться, применяться, координироваться, обслуживаться и т.д. поставщиком услуг, который предлагает управление пользовательскими средами. Например, поставщик услуг способен создавать, вести, поддерживать и т.д. для одного или нескольких пользователей машинный код и/или вычислительную инфраструктуру, в которой выполняется одна или несколько особенностей настоящего изобретения. В ответ поставщик услуг может получать оплату от пользователя на основании соглашения о подписке и/или абонентской плате в качестве примеров. Дополнительно или в качестве альтернативы, поставщик услуг может получать плату за рекламное содержание, продаваемое одному или нескольким третьим лицам.

[0062] Согласно одному аспекту настоящего изобретения для выполнения одного или нескольких аспектов настоящего изобретения может быть развернуто приложение. В качестве одного из примеров, развертывание приложения включает использование вычислительной инфраструктуры, способной выполнять один или несколько аспектов настоящего изобретения.

[0063] В качестве одного из дополнительных аспектов настоящего изобретения, развертывание вычислительной инфраструктуры может включать интегрирование машиночитаемого кода в вычислительную систему, при этом код в сочетании с вычислительной системой способен выполнять один или несколько аспектов настоящего изобретения.

[0064] В качестве еще одного из дополнительных аспектов настоящего изобретения может быть предложен способ интегрирования вычислительной инфраструктуры, включающий интегрирование машиночитаемого кода в компьютерную систему. Компьютерная система содержит машиночитаемую среду, содержащую один или несколько аспектов настоящего изобретения. Код в сочетании с компьютерной системой способен выполнять один или несколько аспектов настоящего изобретения.

[0065] Хотя различные варианты осуществления описаны выше, они являются лишь примерами. Например, вычислительные среды других архитектур могут содержать или использовать один или несколько аспектов настоящего изобретения. Далее, могут быть использованы векторы других размеров и другие регистры, и изменения в командах могут быть сделаны, не отступая от сути настоящего изобретения.

Дополнительно, могут быть использованы другие технологии для расчета расстояния от заданного адреса до определенной границы.

[0066] Кроме того, другие типы вычислительных сред могут выгодно применяться из одного или нескольких аспектов настоящего изобретения. В качестве примера, может использоваться система обработки данных, применимая для хранения и/или выполнения программного кода и содержащая по меньшей мере два процессора, прямо или косвенно связанных со средствами памяти посредством системной шины. Элементы памяти включают, например, локальную память, применяемую во время фактического выполнения программного кода, массовую память и кэш-память, которая обеспечивает временное хранение по меньшей мере части программного кода для уменьшения необходимого числа случаев извлечения кода из массовой памяти во время выполнения.

[0067] С системой прямой или косвенно посредством промежуточных контроллеров ввода-вывод