Управляющий модуль

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат изобретения заключается в повышении сбоеустойчивости начальной загрузки и повышении производительности для каждого микропроцессора управляющего модуля в условиях разрушающего воздействия радиационных факторов при сохранении массогабаритных показателей и ограничении на потребляемую мощность. В управляющем модуле содержатся микропроцессоры, сбоеустойчивые резервируемые параллельные каналы RapidIO, выполненные на основе многоканального коммутатора, микросхемы для хранения информации и электрические линии связи, согласно изобретению он дополнительно снабжен последовательными каналами RapidIO LP-Serial, выполненными на основе двуканального коммутатора, встроенного внутрь каждого микропроцессора. Кроме того, управляющий модуль содержит устройства самодиагностики, распределенную систему управления восстановлением «Реаниматор», состоящую из постоянно запоминающих устройств и однотипных блоков, каждый из которых содержит контроллер аварийного маршрутизатора, сторожевой таймер и таймер общего назначения, связанных между собой посредством ядра процессора, и содержит два дополнительных электронных мезонинных модуля в конструктиве стандарта PMC/RMC, связанных с одним из микропроцессоров. 6 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано при создании высокопроизводительных высоконадежных мультипроцессорных управляющих комплексов и систем цифровой обработки сигналов.

Разработанные управляющие модули на основе микропроцессоров обеспечивают возможность построения цифровых вычислительных комплексов (ЦВК), выполняющих в реальном масштабе времени прием по высокоскоростным каналам потоков данных, первичную обработку сигналов (пространственно-временной спектральный анализ, формирование частотных диапазонов, фильтрацию, пороговое обнаружение), вторичную, третичную и общекомплексную обработку информации, включая решение задач отображения, консервации, документирования и управления на рабочих местах операторов, а также обмен данными с другими приборами и системами как в области научного применения, так и другого специального назначения.

Перспективным направлением развития и применения электроники является разработка высокопроизводительных многопроцессорных модулей с повышенной сбоеустойчивостью к внешнему воздействию и экстремальным тепловым режимам эксплуатации.

Известен управляющий модуль, в состав которого входит: одна двухъядерная система на кристалле - СНК (далее СНК), оперативно запоминающее устройство (далее ОЗУ) с коррекцией ошибок, постоянно запоминающее устройство (далее ПЗУ), системное и перепрограммируемое ППЗУ (перепрограммируемое постоянно запоминающее устройство - ППЗУ) пользователя типа флеш, несколько каналов Ethernet с различной скоростью передачи, один канал параллельного RapidIO, один канал интерфейса PCI, два канала RS-232C и один канал I2C (PM854 Module, Dynatem, Inc. 23263 Madero, Suite C, Mission Viejo, CA (949) 855-3235).

Недостатком описанного модуля является то, что он выполнен в виде мезонина. При выполнении программы начальной загрузки модуля из системного ПЗУ с низкой помехозащищенностью возможны сбои в СНК при получении данных, т.к. ПЗУ является флеш-памятью.

Изобретение управляющий модуль - это отдельный модуль, предназначенный для построения систем цифровой обработки сигналов и высокопроизводительных однородных мультипроцессорных вычислительных комплексов широкого применения с коммутационной средой стандарта RapidIO в конструктиве Евромеханика 6U, существует в нескольких исполнениях, отличающихся стойкостью к внешним воздействующим факторам, количеством микропроцессоров и тактовой частотой.

Задачей изобретения является повышение сбоеустойчивости модуля в момент загрузки управляющих программ из репрограммируемого постоянно запоминающего устройства - РПЗУ пользователя.

Технический результат изобретения заключается в повышении сбоеустойчивости начальной загрузки и повышении производительности для каждого микропроцессора управляющего модуля в условиях разрушающего воздействия радиационных факторов при сохранении массогабаритных показателей и ограничении на потребляемую мощность.

Указанный технический результат достигается тем, что в управляющем модуле, содержащем микропроцессоры, сбоеустойчивые резервируемые параллельные каналы RapidIO, выполненные на основе многоканального коммутатора, микросхемы для хранения информации и электрические линии связи, согласно изобретению он дополнительно снабжен последовательными каналами RapidIO LP-Serial, выполненными на основе двуканального коммутатора, встроенного внутрь каждого микропроцессора, при этом управляющий модуль имеет устройства самодиагностики, распределенную систему управления восстановлением «Реаниматор», состоящую из постоянно запоминающих устройств и однотипных блоков, каждый из которых содержит контроллер аварийного маршрутизатора, сторожевой таймер и таймер общего назначения, связанных между собой посредством ядра процессора, и содержит два дополнительных электронных мезонинных модуля в конструктиве стандарта PMC/RMC, связанных с одним из микропроцессоров.

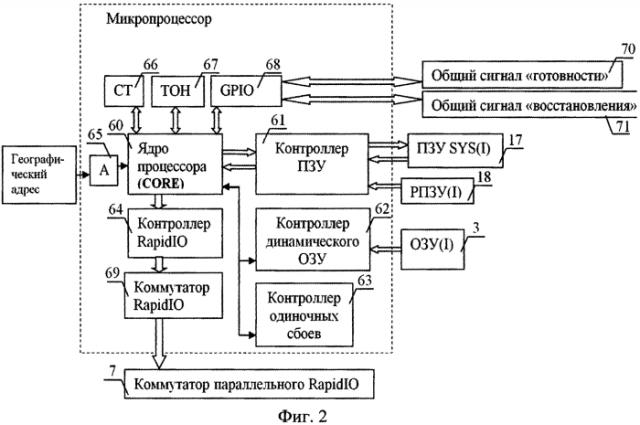

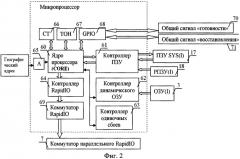

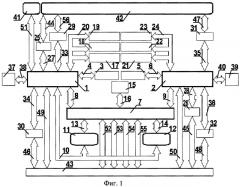

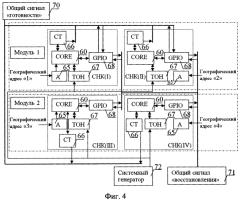

Изобретение поясняется чертежами, где на фиг. 1 представлена функциональная схема управляющего модуля на основе микропроцессоров, на фиг. 2 - структура микропроцессора, на фиг. 3 - структурная схема распределенной системы управления восстановлением, на фиг. 4 - блок-схема подключения двух управляющих модулей и реализации функции восстановления, на фиг. 5 - алгоритм работы системы «Реаниматор», на фиг. 6 - временная диаграмма выработки общего сигнала «готовности».

Управляющий модуль, предназначенный для построения мультипроцессорных вычислительных комплексов широкого применения с коммутационной средой стандарта RapidIO, содержит: два одинаковых микропроцессора 1 и 2 (системы на кристалле - СНК(I) и СНК(II)), ОЗУ(I) динамического типа 3 с возможностью коррекции ошибок по шине связи 4 для микропроцессора 1; ОЗУ(II) динамического типа 5 с возможностью коррекции ошибок по шине связи 6 для микропроцессора 2; многоканальный коммутатор параллельного RapidIO 7, связанный с микропроцессором 1 по каналу RapidIO 8 и с микропроцессором 2 по каналу RapidIO 9; внутреннюю шину PCI 10 для подключения двух мезонинных модулей 11 и 12 в стандарте РМС или RMC; внутренние шины 13 и 14 параллельного RapidIO для подключения двух мезонинных модулей 11 и 12 к коммутатору параллельного RapidIO 7; перепрограммируемое ППЗУ(I) конфигурации 15, связанное с коммутатором параллельного RapidIO 7 посредством интерфейса I2C(I) 16; системное ПЗУ SYS(I) 17 для микропроцессора 1, репрограммируемое постоянно запоминающее устройство - РПЗУ(I) пользователя 18 для микропроцессора 1, NAND-Flash(I) пользователя 19 для микропроцессора 1, функциональные блоки 17, 18, 19 обмениваются данными с микропроцессором 1 по шине ПЗУ(I) 20; системное ПЗУ SYS(II) 21 для микропроцессора 2, РПЗУ(II) пользователя 22 для микропроцессора 2, NAND-Flash(II) пользователя 23 для микропроцессора 2, функциональные блоки 21, 22, 23 обмениваются информацией с микропроцессором 2 по шине ПЗУ(II) 24; ПП ΕΤΗ приемопередатчики 25 и 26 Ethernet с интерфейсом МП для двух микропроцессоров 1 и 2, шины интерфейса МП 27 и 28; приемопередатчики - ПП RS-232C 29, 30, 31, 32 для каждого микропроцессора, шины связи 33 и 34 с микропроцессором 1, шины связи 35 и 36 с микропроцессором 2; перепрограммируемое ППЗУ(II) 37 для хранения переменных окружения и связанное с микропроцессором 1 посредством интерфейса I2C(II) 38; перепрограммируемое ППЗУ(III) 39, связанное с микропроцессором 2 посредством интерфейса I2C(III) 40; соединители 41, 42 и 43 для связи с другими однородными мультипроцессорными модулями; каналы передачи сигналов JTAG, GPIO, интерфейса RS-232C, параллельного RapidIO и последовательного RapidIO LP-Serial (4x SRIO) 44, 45, 46, 47, 48, 49, 50, 51, 52, 53, 54, 55, 56 на соединители 41, 42, 43. Последовательный RapidIO (SRIO) выведен на внешний соединитель 41, служебные и диагностические сигналы выведены на внешний соединитель 42.

Управляющий модуль в составе каждого микропроцессора 1 и 2 содержит: ядро процессора (CORE) 60; контроллер ПЗУ 61; контроллер динамического ОЗУ 62; контроллер одиночных сбоев 63; контроллер RapidIO 64; контроллер аварийного маршрутизатора А 65, входы которого в управляющем модуле соединены с линиями «географического адреса»; сторожевой таймер - СТ 66; таймер общего назначения - ТОН 67 для подключения внешнего синхросигнала; контроллер портов дискретных сигналов GPIO 68. Контроллер ПЗУ 61 соединен с системным ПЗУ SYS(I) 17, РПЗУ(I) 18, NAND-Flash(I) 19; контроллер динамического ОЗУ 62 соединен с ОЗУ(1) 3; контроллер одиночных сбоев 63 соединен с контроллером динамического ОЗУ 62 и ядром процессора (CORE) 60. Контроллер RapidIO 64 через коммутатор RapidIO 69 подключен к многоканальному коммутатору параллельного RapidIO 7. Контроллер RapidIO 64 и коммутатор RapidIO 69 одного микропроцессора служат для передачи данных через коммутатор параллельного RapidIO 7 в другие микропроцессоры.

Структурная схема распределенной системы управления восстановлением «Реаниматор», состоит из: ПЗУ SYS(I,II) 17, 21, РПЗУ(I,II) 18, 22, NAND-Flash(I,II) 19, 23, CHK(I) и СНК(II) (микропроцессоры 1 и 2), соединенные через коммутатор параллельного RapidIO 7. Система также включает в себя: программируемый сторожевой таймер - СТ 66 в составе каждой CHK(I) 1, СНК(II) 2 и контроллер аварийного маршрутизатора А 65. Выход СТ 66 в управляющем модуле подключен к общему сигналу «готовности» 70, один выход контроллера дискретных сигналов GPIO 68 также подключен к общему сигналу «готовности» 70, при этом второй выход GPIO 68 к общему сигналу «восстановления» 71; ТОН 67 подключен к внешнему синхросигналу от системного генератора 72 (фиг. 4). В каждую СНК управляющего модуля заводится географический адрес, который идентифицирует микропроцессор в многомодульной конструкции. Значение географического адреса одной СНК по каналам RapidIO доступно другим СНК.

В управляющем модуле CHK(I) 1 и СНК(II) 2 соединяются между собой по каналам параллельного RapidIO 8 и 9, через объединительную плату и с помощью внешнего кабеля по каналу последовательного RapidIO (SRJO).

При построении ЦВК из нескольких управляющих модулей и соответственно из нескольких СНК для реализаций функции восстановления после сбоя используются: система единого времени, включающая в себя один системный генератор 72, к которому подключены все входы таймеров общего назначения - ТОН 67 и система извещений, объединяющая выходные дискретные сигналы каждой СНК в общий сигнал «восстановления» 71.

В управляющем модуле применяется несколько микросхем для хранения, ввода информации и определения задач мультипроцессорных комплексов: сбоеустойчивые ПЗУ SYS(I) 17 и ПЗУ SYS(II) 21 малого объема, предназначенные для размещения программного обеспечения, содержащие систему «Реаниматор», которая проверяет правильность считываемой информации из флеш-памяти РПЗУ(I) 18 и РПЗУ(II) 22. Если бы ЦВК обработки сигналов был бы ориентирован на решение одной задачи, то было бы достаточной одной РПЗУ и программы ПЗУ SYS(I) 17 и ПЗУ SYS(II) 21 оставались бы также без изменений. Для обеспечения многофункциональности и универсальности ЦВК в РПЗУ(I) 18 (РПЗУ(II) 22) необходимо менять переменные окружения (сколько микропроцессоров включить в задачу, сколько модулей в системе, состав системы, какие идентификаторы) при аппаратной загрузке параметров окружения системы «Реаниматор».

Распределенная система управления восстановлением «Реаниматор» в управляющем модуле работает следующим образом: все СНК модуля начинают выполнять загрузку управляющих программ из ПЗУ SYS и каждая из СНК способна вырабатывать сигнал «готовности» по окончании загрузки; каждая из СНК имеет вход для приема от соседних СНК объединенного сигнала «готовности» 70; если все СНК были загружены без сбоев, то продолжается функционирование модуля в нормальном рабочем режиме; если в какой-либо СНК произошел сбой, срабатывает сторожевой таймер - СТ данной СНК и общий сигнал «готовности» 70 не выдается, то требуется аварийная загрузка. Выходы таймеров СТ 66 каждой СНК объединены с общим сигналом «готовности» 70. Статус о срабатывании СТ доступен управляющей СНК через служебные пакеты, передаваемые по каналам RapidIO. Система на кристалле, в которой произошел сбой, сигнализирует другой СНК об ошибке при загрузке и сама инициирует восстановление. Нормально работающая СЕК при настройке системы опрашивает все соседние СНК и по идентификатору RapidIO определяет, где произошел сбой и выполняет аварийную загрузку в нее управляющих программ, после чего «сбойная» СНК функционирует нормально, а «сбойная» микросхема РПЗУ исключается из работы управляющего модуля и ЦБК. Распределенная система управления восстановлением «Реаниматор» определяет равнозначность СНК и позволяет каждой управляющей CHK(I) 1 или СНК(II) 2 взять на себя функцию восстановления после сбоя.

После прохождения сигнала «сброс» выполняется программа инициализации и проверки каждой СНК. После снятия сигнала «сброс» ядро процессора (CORE) 60 выставляет на одном выходе адрес, по которому контроллер ПЗУ 61 в составе микропроцессора запрашивает у ПЗУ SYS(I) 17 данные. ПЗУ SYS(I) 17 передает запрошенную информацию на вход контроллера ПЗУ 61. Далее контроллер ПЗУ 61 передает данные на вход ядра процессора (CORE) 60. Таким образом, микропроцессор выполняет программу инициализации, содержащуюся в ПЗУ SYS(I) 17, тестирование ОЗУ(I) 3 и конфигурирование устройств.

В тоже время по сбоеустойчивому интерфейсу I2C(I) 16 из ППЗУ(I) конфигурации 15 в коммутатор RapidIO 7 автоматически загружаются таблицы маршрутизации. После выполнения программы инициализации начинается загрузка управляющих программ в каждую CHK(I) 1 и СНК(II) 2 из РПЗУ(I) 18 и РПЗУ(II) 22 соответственно. Если загрузка выполнена успешно, то контроллер дискретных сигналов GPIO 68 устанавливает на своем выходе сигнал «готовности». При успешном выполнении загрузки всех СНК устанавливается общий сигнал «готовности» 70.

Если при загрузке произошел сбой хотя бы в одной из СНК, то срабатывает сторожевой таймер - СТ данной СНК и общий сигнал «готовности» 70 не вырабатывается. При загрузке управляющих программ осуществляется копирование области данных из РПЗУ(I) 18 в ОЗУ(I) 3, используя контроллер динамического ОЗУ 62. При возникновении ошибки в ОЗУ(I) 3 контроллер одиночных сбоев 63 вычисляет ошибочный бит данных и подставляет правильный бит. После выполнения сбоеустойчивого копирования процессор вычисляет контрольную сумму области данных в ОЗУ(I) 3. Если при возникновении сбоя в РПЗУ(I) 18 вычисленная контрольная сумма соответствует эталонной контрольной сумме, хранящейся в ПЗУ SYS(I) 17, то загрузка управляющей программы выполняется из ОЗУ(I) 3. Если сравнения с эталоном не произошло, то дальнейшая загрузка происходит под управлением системы «Реаниматор», алгоритм работы которой представлен на фиг. 5.

Задача системы «Реаниматор» загрузить управляющую программу в ОЗУ, используя дополнительные области данных из РПЗУ и NAND-Flash, а также достоверную копию управляющей программы, размещенную в сбоеустойчивом ОЗУ соседней СНК.

Основные этапами работы системы «Реаниматор» являются: аварийная загрузка из РПЗУ(I) 18; аварийная загрузка из NAND-Flash(I) 19 при неуспешной загрузке из РПЗУ(I) 18; аварийная загрузка с использованием каналов параллельного RapidIO при неуспешной загрузке из NAND-Flash(I) 19 и аварийная загрузка с использованием каналов последовательного RapidIO при неуспешной загрузке с использованием параллельного RapidIO.

При возникновении одиночного сбоя во время загрузки управляющих программ, например в CHK(I) 1, «Реаниматор» сначала выполняет аварийную загрузку из микросхемы РПЗУ(I) 18 (фиг. 3). Копируется резервный блок №1 данных из микросхемы РПЗУ(I) 18 в сбоеустойчивое ОЗУ(I) 3 управляющего модуля. Вычисляется контрольная сумма скопированной области и сравнивается с эталонной, которая располагается в ПЗУ SYS(I) 17. При успешном сравнении система «Реаниматор» заканчивает свою работу и управление дальнейшей загрузкой осуществляется из достоверной скопированной области ОЗУ(I) 3. Если сравнения с эталонным значением не произошло, то подсистема аварийной загрузки задействует следующий резервный блок №2 данных из микросхемы РПЗУ(I) 18. Количество резервных блоков в микросхеме РПЗУ(I) 18 хранится в микросхеме перепрограммируемого ППЗУ(II) 37. Алгоритм определения достоверности резервного блока №2 аналогичен описанному алгоритму для блока №1. Если достоверных блоков из числа используемых блоков в РПЗУ(I) 18 не найдено, то «Реаниматор» начинает этап аварийной загрузки из NAND-Flash(I) 19. Алгоритм аварийной загрузки из NAND-Flash(I) 19 с использованием резервных блоков аналогичен алгоритму аварийной загрузки из РПЗУ(I) 18. При неудачной загрузке из всех доступных и определенных в ППЗУ(I) 15 резервных блоков NAND-Flash(I) 19 система «Реаниматор» начинает этап аварийной загрузки с использованием параллельного RapidIO, основные функции которого: определение управляющей СНК; определение СНК, в которых произошел сбой; сбоеустойчивое копирование по каналам параллельного RapidIO; резервная маршрутизация каналов параллельного RapidIO.

Если при загрузке произошел сбой хотя бы в одной из СНК, то общий сигнал «готовности» 70 не вырабатывается, а нормально работающие СНК (например, СНК(II)) начинают выполнять алгоритм определения, какая из них будет осуществлять функцию восстановления (определения управляющей СНК). ТОН 67 в составе каждой СНК ведут отсчеты времени от начала загрузки. Так как все ТОН подключены к одному системному генератору 72, то временные интервалы отсчитываются для каждой СНК синхронно.

На временной диаграмме (фиг. 6) показаны сигналы «готовности» и «восстановления»: к запланированному и задаваемому программно времени t0 окончания загрузки контроллер GPIO 68 в составе СНК(II) 2 проверят наличие общего сигнала «готовности» 70. Каждая нормально работающая СНК в определенный для нее временной интервал (t1=t0+Δt, t2, t3 и т.д…) согласно количеству модулей в ЦБК и количеству СНК проверяет состояние своего входа контроллера GPIO 68 на наличие общего сигнала «восстановления» 71. Временной интервал для каждой СНК зависит от географического адреса («1», «2», «3» и т.д.), чем меньше значение географического адреса, тем раньше временной интервал определения управляющей системы на кристалле. Например, в момент времени t1=t0+Δt контроллер GPIO 68 анализирует состояние CHK(I) 1 и выясняется, что при загрузке произошел сбой, т.е. CHK(I) 1 не может выполнять функцию восстановления, тогда нормально работающая СНК(II) 2, не обнаруживая на своем входе сигнал «восстановления», становится управляющей.

Посылка сообщений с использованием параллельного RapidIO функционирует следующим образом: контроллер RapidIO 64 в составе СНК(II) 2 формирует сообщения и через коммутатор RapidIO 69 по каналу RapidIO 9 отправляет в коммутатор параллельного RapidIO 7. Коммутатор параллельного RapidIO 7 доставляет сообщение со входа на один из своих выходов. Номер выхода определяется из сообщения и внутренних таблиц маршрутизации. Сообщение через коммутатор параллельного RapidIO 7 по каналу 8 доставляется на вход контроллера RapidIO 64 в составе CHK(I) 1. Далее CHK(I) 1 передает принятое сообщение в ОЗУ(I) 3, извещает ядро процессора (CORE) 60 о приходе сообщения в ОЗУ(I) 3 и отправляет ответное сообщение контроллеру RapidIO управляющей СНК(II) 2 об успешном получении данных.

Сбоеустойчивое копирование по каналам параллельного RapidIO осуществляется следующим образом: контроллер RapidIO 64 в управляющей СНК(II) 2 посылает CHK(I) 1 сообщение о начале загрузки копии управляющей программы в ОЗУ(I) 3. После приема сообщения система «Реаниматор» CHK(I) 1, в которой при загрузке произошла ошибка, активирует сбоеустойчивое копирование по каналам параллельного RapidIO в собственное ОЗУ(I) 3. CHK(I) 1 отправляет ответ управляющей СНК(II) 2 о получении данных. Данные из приемного буфера CHK(I) 1 копируются в область ОЗУ(I) 3, которая будет являться достоверной копией управляющей программы. Контроллер RapidIO 64 управляющей СНК(II) 2 после окончании передачи всего объема программы посылает CHK(I) 1 сообщений об окончании загрузки.

После приема сообщения об окончании загрузки «Реаниматор» СНК(I) заканчивает копирование по каналам параллельного RapidIO и передает управление достоверной копии управляющей программы в ОЗУ(I) 3. После успешной загрузки управляющей программы контроллер GPIO 68 в восстановленной CHK(I) 1 выставляет свой сигнал «готовности» в активное состояние. Далее управляющая СНК(II) 2 продолжит загружать копию управляющей программы в ОЗУ следующей СНК, где произошел сбой, если таковая имеется. После загрузки копий всем аварийным СНК управляющая СНК(II) 2 завершает сбоеустойчивое копирование и переводит свой сигнал «восстановление» в неактивное состояние. Управляющая СНК(II) 2 во временной интервал t2+Δt извещает другие СНК о том, что алгоритм и реализации функции восстановления завершены. Извещение производится путем выставления на своем выходе сигнала «восстановления», при этом устанавливается общий сигнал «восстановления» 71. Во временной интервал t3+Δt анализа состояния СНК(III) не производится, считая, т.к. сбоя при ее загрузке не произошло. После успешной загрузки управляющей программы во всех СНК устанавливается общий сигнал «готовности» 70, что является индикацией успешного функционирования модулей.

При сбое доставки сообщения по каналам параллельного RapidIO система «Реаниматор», исполняемая в управляющей СНК(II) 2, активизирует алгоритм резервной аварийной маршрутизации. Автоматическая маршрутизация пакетов RapidIO достигается через конфигурационное перепрограммируемое ППЗУ(I) 15.

Коммутаторы RapidIO 69 в составе каждой СНК содержат таблицы маршрутизации. Контроллер RapidIO 64 в составе управляющей СНК(II) изменяет маршрут доставки сообщений от СНК(II) 2 до CHK(I) 1. Для этого контроллер аварийного маршрутизатора А 65 в составе управляющей СНК(II) вычисляет географический адрес получателя и изменяет ячейки таблицы маршрутизации коммутатора RapidIO 69 таким образом, что все исходящие сообщения перенаправляются с одного выхода коммутатора RapidIO 69 в составе СНК(II) на другой выход. Далее все исходящие сообщения от управляющей СНК(II) 2 доставляются по резервному маршруту с использованием каналов последовательного RapidIO: через канал 51 до внешнего соединителя 41, далее через внешний кабель до соединителя 43 и затем через канал 50 на вход коммутатора RapidIO 69 в составе СНК(I). Также все ответные сообщения от СНК(II) 2 к CHK(I) 1 доставляются по резервному маршруту. После окончании успешной передачи всего объема копии управляющей программы СНК(I) посылает сообщение об окончании загрузки. После приема сообщения об окончании загрузки система «Реаниматор» управляющей СНК(II) заканчивает копирование по каналам последовательного RapidIO и передает управление достоверной копии управляющей программы в перепрограммируемой ППЗУ(II) 37, начинается исполнение загруженных управляющих программ.

Управляющие модули могут быть использованы при создании высокопроизводительной высоконадежной мультипроцессорной системы цифровой обработки сигналов. Распределенная система управления восстановлением «Реаниматор», которая может быть использована в конструкции управляющего модуля, испытана в модуле ЦП-РИО-64 для использования в мультипроцессорной системе цифровой обработки сигналов для гидроакустического комплекса морского базирования.

Литература

1. RapidIO specification Revision 2.1, Complete Spec. Stack, 2009. URL: http://www.rapidio.org

2. Dynatem, Inc. 23263 Madero, Suite C, Mission Viejo, CA (949) 855-3235), Computers on Module PM854 http://www.dynatem.com/products/pm854.php

3. MPC8540 PowerQUICC III Integrated Host Processor Reference Manual MPC8540RM Rev. 1 07/2004

4. PCI Express Specification and White Papers. URL: http://www.pcisig.com/URL: http://www.pci-sig.com

Управляющий модуль, содержащий микропроцессоры, сбоеустойчивые резервируемые параллельные каналы RapidIO, выполненные на основе многоканального коммутатора, микросхемы для хранения информации и электрические линии связи, отличающийся тем, что он дополнительно снабжен последовательными каналами RapidIO LP-Serial, выполненными на основе двуканального коммутатора, встроенного внутрь каждого микропроцессора, при этом управляющий модуль имеет устройства самодиагностики, распределенную систему управления восстановлением «Реаниматор», состоящую из постоянно запоминающих устройств и однотипных блоков, каждый из которых содержит контроллер аварийного маршрутизатора, сторожевой таймер и таймер общего назначения, связанных между собой посредством ядра процессора, и содержит два дополнительных электронных мезонинных модуля в конструктиве стандарта PMC/RMC, связанных с одним из микропроцессоров.