Виртуальная архитектура неоднородной памяти для виртуальных машин

Иллюстрации

Показать всеИзобретение относится к области технологии виртуализации. Техническим результатом является повышение эффективности управления памятью для виртуальных машин. Способ управления памятью для виртуальных машин содержит этапы, на которых принимают запрос создания экземпляра виртуальной машины, причем запрос включает в себя характеристику виртуальной машины; выбирают топологию виртуальных узлов архитектуры неоднородной памяти (NUMA) для виртуальной машины на основе этой характеристики, причем топология виртуальных NUMA узлов включает в себя множество виртуальных NUMA узлов; создают экземпляр виртуальной машины в вычислительной системе, причем виртуальная машина включает в себя множество виртуальных NUMA узлов; и регулируют, на основе, по меньшей мере частично, нагрузки на память в конкретном виртуальном NUMA узле из множества виртуальных NUMA узлов, объем гостевой памяти, назначенной этому конкретному виртуальному NUMA узлу, на величину, равную второму объему гостевой памяти, причем вторым объемом гостевой памяти осуществляется обмен между упомянутым конкретным виртуальным NUMA узлом и вторым виртуальным NUMA узлом из множества виртуальных NUMA узлов на основе, по меньшей мере частично, нагрузки на память во втором виртуальном NUMA узле. 3 н. и 16 з.п. ф-лы, 17 ил.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Технология виртуализации предусматривает разделение аппаратных ресурсов между многими разделами, каждый из которых может осуществлять хостинг для гостевой операционной системы. В целом, технология виртуальной машины может использоваться для объединения серверов и повышения их переносимости. Поскольку виртуальные машины становятся крупнее, и их рабочие нагрузки увеличиваются, способность легко осуществлять их объединение и/или перемещение с одной вычислительной системы на другую становится более трудной. Соответственно, являются желательными способы, предназначенные для повышения способности осуществлять объединение и/или перемещение более крупных виртуальных машин.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Примерный вариант осуществления настоящего раскрытия описывает способ. В этом примере способ включает в себя, но не ограничивается указанным, прием запроса на создание экземпляра виртуальной машины, запрос включает в себя характеристику виртуальной машины; выбор для виртуальной машины топологии виртуального NUMA узла на основании характеристики, причем топология виртуального NUMA узла включает в себя множество виртуальных NUMA узлов; создание экземпляра виртуальной машины на вычислительной системе, причем виртуальная машина включает в себя множество виртуальных NUMA узлов; и подстройку, на основании нагрузки на память в конкретном виртуальном NUMA узле из множества, объема гостевой памяти, назначенной конкретному виртуальному NUMA узлу. В дополнение к вышеизложенному, другие аспекты описываются в пунктах формулы изобретения, на чертежах и тексте, образующем часть настоящего раскрытия.

Примерный вариант осуществления настоящего раскрытия описывает способ. В этом примере, способ включает в себя, но без ограничения указанным, исполнение виртуальной машины, причем виртуальная машина имеет топологию, которая включает в себя множество виртуальных NUMA узлов, при этом топология виртуальной машины формируется независимо от физической топологии вычислительной системы; определение нагрузки на память в каждом виртуальном NUMA узле из множества; и подстройку, на основании нагрузки на память в каждом виртуальном NUMA узле множества, гостевой памяти, назначенной, по меньшей мере, одному виртуальному NUMA узлу множества. В дополнение к вышеизложенному, другие аспекты описываются в пунктах формулы изобретения, на чертежах и в тексте, образующем часть настоящего раскрытия.

Примерный вариант осуществления настоящего раскрытия описывает способ. В этом примере, способ включает в себя, но без ограничения указанным, исполнение первой виртуальной машины, причем виртуальная машина имеет топологию, которая включает в себя множество виртуальных NUMA узлов, каждый виртуальный NUMA узел множества включает в себя виртуальный процессор и гостевые физические адреса, при этом топология виртуальной машины формируется независимо от физической топологии вычислительной системы; и добавление дополнительного виртуального процессора к виртуальному NUMA узлу множества. В дополнение к вышеизложенному, другие аспекты описаны в пунктах формулы изобретения, на чертежах и в тексте, образующем часть настоящего раскрытия.

Специалист в данной области техники может оценить, что один или несколько различных аспектов раскрытия могут включать в себя, без ограничения указанным, схемное и/или программное решение для осуществления упомянутых в документе аспектов настоящего раскрытия; схемное и/или программное решение могут быть фактически любой комбинацией аппаратных средств, программного обеспечения и/или микропрограммного обеспечения, конфигурированной для осуществления упомянутых в документе аспектов в зависимости от проектных решений разработчика системы.

Вышеизложенное является кратким описанием и таким образом содержит, по необходимости, упрощения, обобщения и опущения подробностей. Специалисты в данной области техники оценят, что краткое описание является лишь иллюстративным и не подразумевается, что является ограничительным каким-либо образом.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - изображение примерной вычислительной системы, в которой могут быть реализованы аспекты настоящего раскрытия.

Фиг.2 - изображение операционной среды для применения на практике аспектов настоящего раскрытия.

Фиг.3 - изображение операционной среды для применения аспектов настоящего раскрытия.

Фиг.4 - изображение организации памяти в вариантах осуществления настоящего раскрытия.

Фиг.5 - изображение примерной операционной среды, применяющей аспекты настоящего раскрытия.

Фиг.6 - изображение примерной операционной среды, применяющей аспекты настоящего раскрытия.

Фиг.7 - изображение примерной операционной среды, применяющей аспекты настоящего раскрытия.

Фиг.8 - изображение примерной блок-схемы, иллюстрирующей аспекты настоящего раскрытия.

Фиг.9 - изображение последовательности операций для применения аспектов настоящего раскрытия.

Фиг.10 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.9.

Фиг.11 - изображение последовательности операций для применения аспектов настоящего раскрытия.

Фиг.12 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.11.

Фиг.13 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.12.

Фиг.14 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.12.

Фиг.15 - изображение последовательности операций для применения аспектов настоящего раскрытия.

Фиг.16 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.15.

Фиг.17 - изображение альтернативного варианта осуществления для последовательности операций по Фиг.16.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Варианты осуществления могут исполняться на одном или нескольких компьютерах. Фиг.1 и последующее обсуждение предназначены для обеспечения краткого общего описания подходящей вычислительной среды, в которой может быть реализовано раскрытие. Специалист в данной области техники может оценить, что вычислительная система по Фиг.1 может в некоторых исполнениях реализовывать вычислительные системы 200, 300, 600, и 700. В этих примерных вариантах осуществления вычислительные системы могут включать в себя некоторые или все компоненты, описанные на Фиг.1, и схему в конфигурации с возможностью реализации аспектов настоящего раскрытия.

Термин «схема», используемый по всему раскрытию, может заключать в себе аппаратные компоненты, такие как контроллеры аппаратных прерываний, накопители на жестких дисках, сетевые адаптеры, графические процессоры, аппаратно реализованные кодеки видео/аудио, и микропрограммное/программное обеспечение, используемое для оперирования такими аппаратными средствами. В тех же или других вариантах осуществления термин «схема» может заключать в себе микропроцессоры, конфигурированные для выполнения функции(й) посредством микропрограммного обеспечения или коммутаторов, установленных некоторым образом. В тех же или других примерных вариантах осуществления термин «схема» может заключать в себе один или несколько логических процессоров, например, одно или несколько процессорных ядер (базовых средств) многоядерного универсального устройства обработки. Логический процессор(ы) в этом примере может быть конфигурирован посредством программных команд, реализующих логику, выполненную с возможностью выполнять функцию(и), которые загружаются из машинной памяти, например, оперативного запоминающего устройства (ОЗУ, RAM), постоянного запоминающего устройства (ПЗУ, ROM), микропрограммного обеспечения и/или виртуальной памяти. В примерных вариантах осуществления, где схема включает в себя комбинацию аппаратных средств и программного обеспечения, разработчик может записать реализующий логику исходный код, который впоследствии компилируется в машиночитаемый код, который может обрабатываться логическим процессором. Поскольку специалист в данной области техники может оценить, что уровень техники эволюционировал к позиции, где существует небольшое различие между аппаратными средствами, программным обеспечением или комбинацией аппаратного/программного обеспечения, выбор «аппаратные средства против программного обеспечения», чтобы осуществлять функции, является лишь выбором проектного решения. Таким образом, поскольку специалист в данной области техники может оценить, что программно реализованный процесс может быть преобразован в эквивалентную аппаратную структуру, и аппаратная структура может быть непосредственно преобразована в эквивалентный программно реализованный процесс, выбор «аппаратная реализация против программной реализации» является одной из альтернатив проектного решения и оставляется разработчику.

Теперь с обращением на Фиг.1, на ней изображена иллюстративная универсальная вычислительная система. Универсальная вычислительная система может включать в себя обычный компьютер 20 или подобный, включающий в состав логический процессор 21, системную память 22 и системную шину 23, которая связывает различные компоненты системы, включая системную память, с логическим процессором 21. Системная шина 23 может быть любой из нескольких типов шинных архитектур, включая шину памяти или контроллер памяти, периферийную шину, и локальную шину, использующую любую из разнообразия шинных архитектур. Системная память может включать в себя постоянное ЗУ (ПЗУ) 24 и оперативное ЗУ (ОЗУ) 25. Базовая система 26 ввода/вывода (БИОС, BIOS), содержащая основные программы, которые содействует передаче информации между компонентами внутри компьютера 20, например, в течение запуска, хранится в ПЗУ 24. Компьютер 20 может дополнительно включать в состав накопитель 27 на жестком диске для считывания с жесткого диска и записи на него (не показано), накопитель 28 на магнитном диске для считывания со съемного магнитного диска 29 или записи на него, и накопитель 30 на оптическом диске для считывания со съемного оптического диска 31, такого как ПЗУ на компакт-диске (CD ROM), или записи на таковой, или другой оптический носитель. Накопитель 27 на жестком диске, накопитель 28 на магнитном диске и накопитель 30 на оптическом диске показаны соединенными с системной шиной 23 интерфейсом 32 накопителя на жестком диске, интерфейсом 33 накопителя на магнитном диске и интерфейсом 34 накопителя на оптическом диске, соответственно. Накопители и связанные с ними читаемые компьютером носители информации обеспечивают энергонезависимое ЗУ для читаемых компьютером команд, структур данных, программных модулей и других данных для компьютера 20. Хотя иллюстративная среда, описанная в документе, использует накопитель на жестком диске, съемный магнитный диск 29 и съемный оптический диск 31, специалисты в данной области техники должны оценить, что другие типы читаемых компьютером носителей информации, которые могут хранить данные, являющиеся доступными посредством компьютера, такие как магнитные кассеты, карты флэш-памяти, цифровые видеодиски, картриджи Бернулли, оперативные ЗУ (ОЗУ), постоянные ЗУ (ПЗУ) и т.п., также могут использоваться в иллюстративной среде. В целом, в некоторых вариантах осуществления, такие читаемые компьютером носители информации могут использоваться, чтобы хранить исполнимые процессором команды, реализующие аспекты настоящего раскрытия.

Ряд программных модулей может храниться на накопителе на жестком диске, магнитном диске 29, оптическом диске 31, в ПЗУ 24 или ОЗУ 25, включая операционную систему 35, одну или несколько прикладных программ 36, другие программные модули 37 и программные данные 38. Пользователь может вводить команды и информацию в компьютер 20 через устройства ввода данных, такие как клавиатура 40 и указательное устройство 42. Другие устройства ввода данных (не показано) могут включать в себя микрофон, джойстик, игровую панель, спутниковую антенну, сканер или подобное. Эти и другие устройства ввода данных обычно соединяются с логическим процессором 21 через интерфейс 46 последовательного порта, который связан с системной шиной, но могут соединяться посредством других интерфейсов, таких как параллельный порт, игровой порт или универсальная последовательная шина (USB). Дисплей 47 или другой тип устройства отображения также может соединяться с системной шиной 23 через интерфейс, такой как видеоадаптер 48. В дополнение к дисплею 47, компьютеры обычно включают в состав другие периферийные устройства вывода (не показано), такие как динамики и принтеры. Иллюстративная система по Фиг.1 также включает в состав контроллер 55, шину 56 интерфейса малых вычислительных систем (SCSI) и внешнее запоминающее устройство 62, подсоединенное к шине 56 SCSI.

Компьютер 20 может действовать в сетевой среде, используя логические соединения с одним или несколькими удаленными компьютерами, например, удаленным компьютером 49. Удаленный компьютер 49 может быть другим компьютером, сервером, маршрутизатором, сетевым ПК, одноранговым устройством или другим обычным сетевым узлом, и обычно может включать в себя многие или все компоненты, описанные выше относительно компьютера 20, хотя на Фиг.1 было показано только запоминающее устройство 50. Логические соединения, изображенные на Фиг.1, могут включать в себя локальную вычислительную сеть (LAN) 51 и глобальную вычислительную сеть (WAN) 52. Такие сетевые среды являются обычными в учреждениях, вычислительных сетях масштаба предприятия, внутрикорпоративных локальных сетях и сети Интернет.

При использовании в сетевой среде LAN компьютер 20 может быть соединен с локальной сетью 51 через сетевой интерфейс или адаптер 53. При использовании в сетевой среде WAN компьютер 20 обычно может включать в состав модем 54 или другое средство для установления связи по сети WAN 52, такой как сеть Интернет. Модем 54, который может быть внутренним или внешним, может быть соединен с системной шиной 23 через интерфейс 46 последовательного порта. В сетевой среде программные модули, изображенные относящимися к персональному компьютеру 20, или их части, могут храниться на удаленном запоминающем устройстве. Будет оценено, что показанные сетевые соединения являются иллюстративными и могут использоваться другие средства установления линии связи между компьютерами. Кроме того, хотя предполагается, что многочисленные варианты осуществления настоящего раскрытия являются особенно хорошо подходящими для компьютеризированных систем, в этом документе отсутствует что-либо, предназначенное для ограничения раскрытия такими вариантами осуществления.

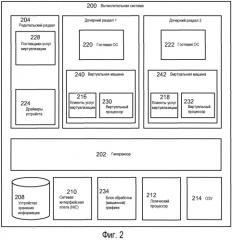

Теперь, что касается Фиг.2 и 3, на них изображены высокоуровневые блок-схемы вычислительных систем. Как показано фигурой чертежа, вычислительная система 200 может включать в состав физические аппаратные устройства, такие как устройства 208 хранения информации, например, накопитель на жестком диске, сетевую интерфейсную плату (NIC) 210, графическую плату 234, по меньшей мере, один логический процессор 212, и оперативную память (ОЗУ) 214. Вычислительная система 200 может также включать в состав компоненты такие же, как компьютер 20 по Фиг.1. Хотя проиллюстрирован один логический процессор, в других вариантах осуществления компьютерная система 200 может иметь множество логических процессоров, например, множество исполнительных ядер (процессора) на один процессор и/или множество процессоров, каждый из которых может иметь множество исполнительных ядер. Продолжая описание Фиг.2, изображен гипервизор 202, который в области техники может также называться «монитор виртуальной машины». Гипервизор 202 в изображенном варианте осуществления включает в себя исполнимые команды, предназначенные для управления и арбитража доступа к аппаратным средствам вычислительной системы 200. В общих чертах, гипервизор 202 может формировать среды исполнения (программ), называемые разделами, такие как дочерний раздел 1 - дочерний раздел N (где N - целое число больше 1). В вариантах осуществления дочерний раздел может рассматриваться базовой единицей изолированности, поддерживаемой гипервизором 202, то есть, каждый дочерний раздел может быть отображен на множество аппаратных ресурсов, например, память, устройства, такты логического процессора, и т.д., который находится под управлением гипервизора 202 и/или родительского раздела. В вариантах осуществления гипервизором 202 может быть автономный программный продукт, часть операционной системы, встроенной в микропрограммное обеспечение системной («материнской») платы, специализированные интегральные схемы или комбинация такового.

В изображенном примере вычислительная система 200 включает в себя родительский раздел 204, который также можно рассматривать как домен 0 в сообществе (разработчиков) систем с открытым исходным кодом. Родительский раздел 204 может конфигурироваться для предоставления ресурсов гостевым операционным системам, исполняющимся в дочерних разделах 1-N, путем использования поставщиков 228 услуг виртуализации (VSP), которые также известны как драйверы серверной части в сообществе использующих открытый исходный код. В этой примерной архитектуре родительский раздел 204 может управлять пропуском (являться шлюзом) доступа к базовому аппаратному обеспечению. В общих чертах, VSP 228 могут использоваться, чтобы мультиплексировать интерфейсы к аппаратным ресурсам при посредстве клиентов услуг виртуализации (VSC), которые также известны как драйверы клиентской (передней) части в сообществе использующих открытый исходный код. Каждый дочерний раздел может включать в себя один или несколько виртуальных процессоров, например, виртуальные процессоры 230-232, так что гостевые операционные системы 220-222 могут управлять и планировать потоки для исполнения на них. В целом, виртуальные процессоры 230-232 являются исполнимыми командами и связанной с ними информацией состояния, которые обеспечивают представление физического процессора с конкретной архитектурой. Например, одна виртуальная машина может содержать виртуальный процессор, имеющий характеристики процессора Intel x86, тогда как другой виртуальный процессор может иметь характеристики процессора PowerPC. Виртуальные процессоры в этом примере могут отображаться на логические процессоры вычислительной системы так, что команды, которые выполняют виртуальные процессоры, будут поддержаны логическими процессорами. Таким образом, в этих примерных вариантах осуществления, многие виртуальные процессоры могут быть исполняющимися одновременно в то время, как, например, другой логический процессор исполняет команды гипервизора. В сущности говоря, и как проиллюстрировано фигурой чертежа, комбинацию виртуальных процессоров, различных VSC и памяти в разделе может рассматривать виртуальной машиной, такой как виртуальная машина 240 или 242.

В целом, гостевые операционные системы 220-222 могут включать в себя любую операционную систему, такую как, например, операционные системы от компаний Microsoft®, Apple®, сообщество использующих открытый исходный код, и т.д. Гостевые операционные системы могут включать в себя пользовательский/привилегированный режимы работы и могут иметь ядра операционной системы, которые могут включать в себя планировщики, диспетчеры памяти, и т.д. Каждая гостевая операционная система 220-222 может содержать связанные с ней файловые системы, которые могут содержать хранимые на них приложения, такие как серверы электронной коммерции, серверы электронной почты, и т.д., и гостевые операционные системы непосредственно. Гостевые операционные системы 220-222 могут планировать потоки для исполнения на виртуальных процессорах 230-232, и экземпляры таких приложений могут приводиться в исполнение.

Теперь с обращением на Фиг.3 иллюстрируется альтернативная архитектура, которая может использоваться. На Фиг.3 изображены компоненты, подобные таковым на Фиг.2, однако в этом примерном варианте осуществления, гипервизор 202 может включать в себя поставщики 228 услуг виртуализации и драйверы 224 устройств, и родительский раздел 204 может содержать вспомогательные программы 236 задания конфигурации. В этой архитектуре гипервизор 202 может выполнять такие же или сходные функции, как гипервизор 202 по Фиг.2. Гипервизор 202 по Фиг.3 может быть автономным программным продуктом, частью операционной системы, встроенной в микропрограммное обеспечение системной платы, или блок гипервизора 202 может быть реализован специализированными интегральными схемами. В этом примере родительский раздел 204 может содержать команды, которые могут использоваться, чтобы задавать конфигурацию гипервизора 202, однако запросы доступа к аппаратному обеспечению могут обрабатываться гипервизором 202 вместо того, чтобы пересылаться на родительский раздел 204.

Теперь с обращением к Фиг.4 иллюстрируется организация памяти в вариантах осуществления, которые включают в себя виртуальные машины. Например, вычислительная система, такая как вычислительная система 200, может иметь ОЗУ 214, имеющее адреса памяти. Вместо предоставления отчета о системных физических адресах памяти на виртуальные машины, гипервизор 202 может представлять различные адреса для системных физических адресов, например, гостевые физические адреса (GPA), на диспетчеры памяти гостевых операционных систем. Гостевые операционные системы затем могут манипулировать гостевыми физическими адресами, и гипервизор 202 поддерживает взаимосвязи согласно адресам GPA и SPA. Как показано фигурой чертежа, в варианте осуществления адресы GPA и SPA могут быть организованы в виде блоков (данных) в памяти. В общих чертах, блок памяти может включать в себя одну или несколько страниц памяти. Взаимосвязи между адресами GPA и SPA могут поддерживаться таблицей теневых страниц, например, таковой, описанной в принадлежащей тому же правообладателю заявке на патент США за номером № 11/128665, озаглавленной "Enhanced Shadow Page Table Algorithms" (Усовершенствованные алгоритмы таблицы теневых страниц), содержание которой тем самым во всей полноте включено в документ путем ссылки. В действии, если гостевая операционная система хранит данные в виде адреса GPA в блоке 1, данные фактически могут храниться в другом SPA, таком как блок 6, в системе.

Вкратце на Фиг.5 изображена операционная среда для применения аспектов настоящего раскрытия. Например, некоторое число вычислительных систем 504-510 могут быть связаны вместе в центр 500 хранения и обработки данных 500 (дата-центр) (хотя изображены четыре вычислительные системы, специалист в данной области техники может оценить, что дата-центр 500 может включать в себя больше или меньше вычислительных систем). Изображенные вычислительные системы могут иметь различные топологии, и, кроме того, они могут иметь различные характеристики, например, различные объемы ОЗУ, различное быстродействие ОЗУ, различное количество логических процессоров и/или логические процессоры с различным быстродействием.

Система 502 управления может содержать компоненты, подобные таковым вычислительной системы 20 по Фиг.1, и/или вычислительных систем 200, 300, 600 или 700. То есть, в одном варианте осуществления система 502 управления может быть вычислительной системой, которая заключает в себе объект изобретения, описанный ниже по отношению к Фиг.6 или 7.

Продолжая общий краткий обзор чертежей, на Фиг.6 изображена вычислительная система 600, имеющая топологию симметричной многопроцессорной системы (SMP) или 'плоскую' топологию. В целом, SMP является архитектурой вычислительной системы, которая включает в состав множество процессоров, которые соединены с одной совместно используемой памятью. В этой организации, контроллер 602 памяти может управлять потоком данных в память и из нее. Доступ к памяти может быть однородным по отношению к каждому логическому процессору 212A-F, и каждый логический процессор может осуществлять доступ к полному диапазону (адресов) памяти, то есть, системным физическим адресам 622-632. Эта топология работает хорошо для вычислительных систем с относительно небольшим числом процессоров, но если вычислительная система включает много процессоров, все конкурирующие за доступ к шине совместно используемой памяти, рабочая характеристика системы может снижаться. Кроме того, сложность вычислительной системы значительно увеличивается, каковое в свою очередь повышает стоимость на один процессор.

Вкратце, вычислительная система 600 может включать в состав такие же или подобные компоненты, как компьютер 200 или 300. Как показано фигурой чертежа, вычислительная система 600 может содержать множество логических процессоров 212A-212F (хотя изображены шесть логических процессоров, вычислительная система может иметь больше или меньше), связанных вместе через контроллер 602 памяти, который управляет пропуском доступа к ОЗУ 214. Подобно описанному выше, каждый логический процессор 212A-212F может иметь различные характеристики, например, тактовые частоты, размер кэша, и т.д. В этой организации контроллер 602 памяти может управлять потоком данных в ОЗУ 214 и из него.

Может быть создан экземпляр гипервизора 202, и он может управлять аппаратными средствами вычислительной системы 600. Гипервизор 202 может управлять одной или несколькими виртуальными машинами 240-242, каждая из которых может содержать виртуальные NUMA узлы, такие как виртуальные NUMA узлы 606-612. Виртуальные NUMA узлы 606-612 могут использоваться для определения организации ресурсов виртуальной машины путем предоставления отчета о виртуальных топологиях на гостевые приложения или гостевые операционные системы, такие как гостевые операционные системы 220 и 222. Как показано фигурой чертежа, каждый виртуальный NUMA узел 606-612 может содержать один или несколько виртуальных процессоров 230A-D, 232A-D и гостевые физические адреса 614-616 и 618-620. В целом, гипервизор 202 может поддержать каждый виртуальный NUMA узел 606-612 с помощью одного или нескольких логических процессоров и системных физических адресов из ОЗУ 214. То есть, гипервизор 202 может задавать один или несколько логических процессоров в качестве «идеальных» процессоров, которые могут использоваться, чтобы исполнять потоки виртуальных процессоров.

Вкратце, на Фиг.7 изображена вычислительная система 700 с топологией, включающей в себя NUMA узлы 702-706. Вычислительные системы с NUMA узлами в целом могут рассматриваться как компьютеры, которые составлены из меньших вычислительных систем. В этом примере, каждый NUMA узел 606-612 может включать в себя один или несколько логических процессоров и локальную память. Память внутри NUMA узла считается локальной памятью, и память в других NUMA узлах считается удаленной памятью, поскольку только процессоры внутри узла соединены с одной и той же шиной памяти. NUMA узлы внутренне соединяются кэш-когерентными на уровне домена межсоединениями, которые дают возможность процессорам в одном NUMA узле осуществлять доступ к памяти в других NUMA узлах когерентным образом. Тем самым, системные физические адреса 622-632 являются однородными по отношению к каждому процессору. Или другими словами, системный физический адрес 20000 является одинаковым для каждого процессора в вычислительной системе. Различие состоит в том, что для некоторых процессоров адрес памяти, соответствующий 20000, является адресом локальной памяти, например, внутри их NUMA узла, а для других процессоров адрес памяти 20000 является удаленным, например, вне их NUMA узла. В целом, к локальной памяти можно осуществлять доступ быстрее, чем к удаленной памяти, и соотношение между временем «локальный против удаленного» доступа называется отношением NUMA. Отношение NUMA от 1 до 2 означает, что требуется в два раза больше тактов процессора, чтобы осуществить доступ к конкретному удаленному системному физическому адресу, чем к локальному системному физическому адресу. NUMA смягчает узкие места, обусловленные системами SMP, путем ограничения числа процессоров на одну любую шину памяти, и в целом является менее дорогим, чем вычислительная система SMP с тем же количеством логических процессоров.

Вычислительная система 700 может включать в себя такие же или подобные компоненты, что и компьютер 200 или 300. Как показано фигурой чертежа, в этой операционной среде вычислительная система 700 включает в себя три NUMA узла 702-706 (хотя компьютер может иметь больше или меньше), соединенных межсоединениями 708. Как проиллюстрировано фигурой чертежа, число процессоров в рамках каждого NUMA узла может быть переменным, и каждый узел может иметь свое собственное ОЗУ.

Подобно Фиг.7, гипервизор 202 может управлять аппаратным обеспечением вычислительной системы 700. Когда загружаются гостевые операционные системы или цельные приложения, они могут выявлять топологии виртуальных машин 240 и 242, подобных описанным выше. Каждому виртуальному NUMA узлу 606-612 может быть назначен один или несколько идеальных процессоров и системные физические адреса из того же NUMA узла, который может использоваться для исполнения потоков виртуального процессора.

Хотя вычислительные системы 600 и 700 изображены включающими в состав две виртуальные машины 240 и 242, в других вариантах осуществления они могут исполнять больше или меньше виртуальных машин. Кроме того, хотя каждая виртуальная машина изображена с наличием двух виртуальных NUMA узлов, в других вариантах осуществления, виртуальные машины могут иметь больше или меньше виртуальных NUMA узлов. Также, хотя виртуальные NUMA узлы изображены имеющими два виртуальных процессора, в других вариантах осуществления виртуальные NUMA узлы могут содержать больше или меньше виртуальных процессоров. Кроме того, каждый виртуальный NUMA узел может иметь топологию, отличную от других виртуальных NUMA узлов, например, один виртуальный NUMA узел может содержать 4 виртуальных процессора и ОЗУ в 8 гигабайтов, тогда как другой виртуальный NUMA узел может содержать 2 виртуальных процессора и ОЗУ в 4 гигабайта.

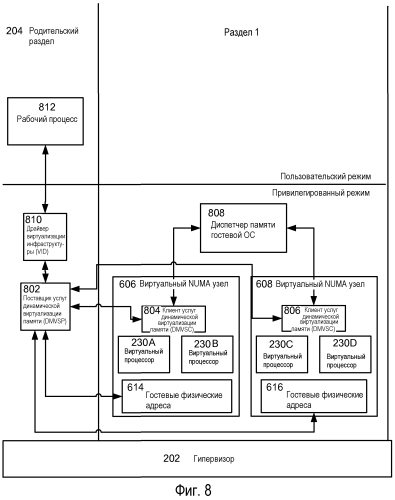

На Фиг.8 изображена блок-схема среды, которая может использоваться в аспектах настоящего раскрытия. Как показано фигурой чертежа, иллюстрируется компонент, управляющий памятью, назначенной виртуальной машине, который может быть известным как поставщик 802 услуг динамической виртуализации памяти (DMVSP), и может использоваться, чтобы подстраивать объем памяти, доступной для виртуального NUMA узла. Как показано фигурой чертежа, DMVSP 802 может связываться с одним или несколькими драйверами динамического изменения выделяемой памяти (ballooning), которые могут быть известны как клиенты услуг виртуализации, а с клиентами 804 и/или 806 услуг динамической виртуализации памяти (DMVSC) (хотя изображен один DMVSC на каждый виртуальный NUMA узел, в других вариантах осуществления может использоваться один DMVSC на один раздел). В общих чертах, клиенты DMVSC 804 и/или 806 могут обеспечивать информацию, которая может использоваться DMVSP 802, чтобы подстраивать память виртуальных NUMA узлов, и каждый DMVSC может также помогать осуществлять передачу и возврат памяти от виртуального NUMA узла, с которым он связан. Клиенты DMVSC 804, 806, и DMVSP 802 могут обмениваться информацией посредством шины виртуализации, описанной в заявке на патент США за номером №11/128647, озаглавленной "Partition Bus" (Шина раздела), содержание которой включено в документ путем ссылки во всей полноте. Кроме того, дополнительные аспекты DMVSC-клиентов и DMVSP-поставщиков описаны в заявке на патент США за номером № 12/345469, озаглавленной "Dynamic Virtual Machine Memory Management" (Динамическое управление памятью виртуальной машины), содержание которой включено в документ путем ссылки во всей полноте.

Продолжая описание Фиг.8, система может включать в себя изображенный рабочий процесс 812 («исполнитель»), который может управлять дочерним разделом(ами). Рабочий процесс 812 может работать вместе с драйвером 810 виртуализации инфраструктуры (VID), который может распределять память дочернего раздела. Например, VID 810 может устанавливать и удалять взаимосвязи между гостевыми физическими адресами и системными физическими адресами. На Фиг.8 также изображен раздел, которая может включать в себя гостевую операционную систему, такую как гостевая операционная система 220, которая может включать в себя диспетчер 808 памяти. В целом, диспетчер 808 памяти может распределять память приложениям по их запросу и освобождать память, когда она больше не требуется приложениям.

Нижеследующее является рядом блок-схем, изображающих реализации процессов. Для простоты понимания блок-схемы организованы так, что начальные блок-схемы представляют реализацию с точки зрения полной "общей картины", и последующие блок-схемы обеспечивают дальнейшие дополнения и/или подробности. Кроме того, специалист в данной области техники может оценить, что последовательность операций, изображенная пунктирными линиями, рассматривается необязательной.

Возвращаясь теперь к Фиг.9, на ней изображена последовательность операций для применения аспектов настоящего раскрытия, включающая операции 900-910. Последовательность операций начинается операцией 900, и операция 902 иллюстрирует прием запроса на создание экземпляра виртуальной машины, запрос включает характеристику виртуальной машины. Например, и со ссылкой на Фиг.6 или 7, гипервизор 202 может принимать запрос на создание виртуальной машины, такой как виртуальная машина 240. Например, запрос может приниматься от системы 502 управления, родительского раздела 204 по Фиг.2 или 3, и т.д. Запрос может быть запросом на новую виртуальную машину, или он может быть запросом на экземпляр предварительно сохраненной виртуальной машины. Если виртуальной машиной 240 является новая виртуальная машина, характеристики виртуальной машины, например, объем оперативной памяти, назначенной виртуальной машине, число виртуальных процессоров, или какой тип устройств ввода/вывода должна иметь виртуальная машина, могут быть заданы, например, администратором.

Продолжая описание Фиг.9, операция 904 показывает выбор топологии виртуального NUMA узла для виртуальной машины на основании характеристики, топология виртуального NUMA узла включает в себя множество виртуальных NUMA узлов. Например, процесс в родительском разделе 204 (и/или гипервизоре 202) может определять топологию для виртуальной машины 240 на основании принятой характеристики. Например, родительский раздел 204 может включать информацию, которая идентифицирует заданный по умолчанию размер для виртуального NUMA узла, такого как виртуальный NUMA узел 606. Процесс в родительском разделе 204 может использовать информацию, которая описывает заданный по умолчанию размер и требуемую характеристику, чтобы определить число виртуальных NUMA узлов для виртуальной машины 240. В конкретном примере, требуемой характеристикой может быть 6-процессорная виртуальная машина с ОЗУ в 10 гигабайтов. Если заданный по умолчанию размер виртуального NUMA узла включает 2 виртуальных процессора и ОЗУ в 4 гигабайта, то система 502 управления может сформировать конфигурационный файл, который указывает, что виртуальная машина 240 будет включать в себя 3 виртуальных NUMA узла.

В варианте осуществления заданный по умолчанию размер виртуального NUMA узла может задаваться администратором или системой 502 управления. Возвращаясь к Фиг.5, система 502 управления может исполнять одну или несколько программ, которые могут получать информацию, которая идентифицирует физическую топологию вычислительных систем 504-510, в дата-центре 500, например, информацию, которая идентифицирует, сколько NUMA узлов (если таковые есть) содержит каждая вычислительная система 504-510, насколько велико ОЗУ, которое содержит каждая вычислительная система 504-510, быстродействие ОЗУ, как организовано ОЗУ, быстродействие процессоров, сколько процессорных ядер содержит каждый процессор, и т.д.

В целом, размер виртуального NUMA узла влияет на работу виртуальных машин в дата-центре 500. Например, если размер виртуального NUMA узла увеличивается, например, по памяти и/или процессорам, переносимость виртуального NUMA узла снижается. Или другими словами, «большие» виртуальные NUMA узлы могут затруднять перемещение виртуальной машины. Это происходит потому, что виртуальный NUMA узел должен назначаться или NUMA узлу, или вычислительной системе, которая имеет достаточно 'плоских' ресурсов, чтобы осуществлять виртуальный NUMA узел. Если, например, виртуальный NUMA узел является слишком большим, например, он содержит слиш