Управление дислокациями и напряжениями в безмасковых процессах с использованием паттернирования субстратов и способы изготовления устройств

Иллюстрации

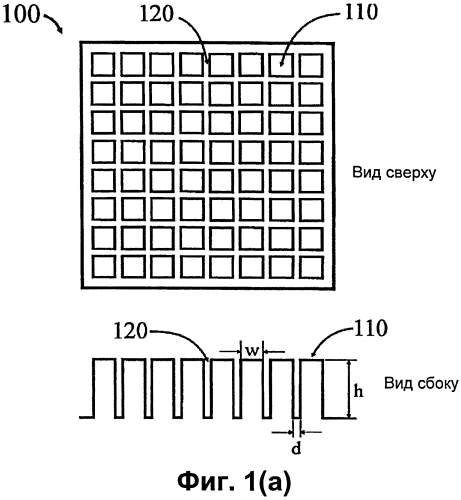

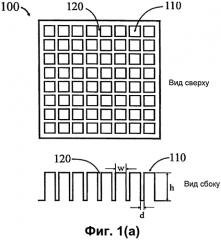

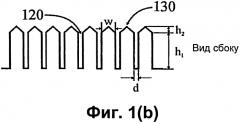

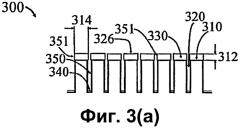

Показать всеИзобретение относится к структурам и способам изготовления стопок активных слоев полупроводниковых материалов. Изобретение обеспечивает получение стопок активных слоев полупроводниковых материалов с согласованными параметрами кристаллических решеток, рассогласованными параметрами кристаллических решеток и рассогласованными коэффициентами термического расширения с низкой плотностью винтовых дислокаций, отсутствием растрескивания слоев и минимизированным прогибом подложки с использованием эпитаксиального наращивания на приподнятых участках подложки в безмасковом процессе. Структура содержит паттернированную кристаллическую полупроводниковую основу с приподнятыми областями, ограниченными бороздками, глубина которых по меньшей мере равна их ширине, и эпитаксиальный полупроводниковый материал, осажденный на приподнятых областях основы в форме изолированных пятен, причем основа изготовлена из первого кристаллического полупроводникового материала, а эпитаксиальный полупроводниковый материал содержит по меньшей мере один второй кристаллический полупроводниковый материал, обладающий рассогласованием кристаллической решетки или рассогласованием коэффициента термического расширения относительно основы, а скорость вертикального роста эпитаксиально наращиваемого материала значительно выше, чем скорость латерального роста. 2 н. и 11 з.п. ф-лы, 41 ил.

Реферат

ПЕРЕКРЕСТНЫЕ ССЫЛКИ НА РОДСТВЕННЫЕ ЗАЯВКИ

Данная заявка претендует на приоритет и эффект изобретения в соответствии с предварительной заявкой на патент США с регистрационным номером 61328203, поданной 27 апреля 2010 г., содержание которой полностью включено в настоящее описание посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к структурам и способам устранения винтовых дислокации (изменений в пространственной решетке кристалла), растрескивания слоев и прогиба подложки при эпитаксиальном наращивании слоев с рассогласованием кристаллических решеток или рассогласованием коэффициентов термического расширения с использованием паттернированных подложек. Поскольку выбор материалов и толщины слоев являются практически неограниченными, то изобретение может также быть использовано для изготовления устройств, требующих для правильного функционирования толстых эпислоев, таких как многопереходные солнечные элементы, светоизлучающие диоды, полупроводниковые лазеры, радиационные видеодетекторы и термоэлектрические устройства. Изобретение также может быть использовано для изготовления интегральных, оптоэлектронных и фотонных микросхем, требующих меньшей толщины слоев с рассогласованием кристаллических решеток.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Все попытки расширить сферу действия закона Мура посредством внедрения в КМОП-платформу (микросхемы на комплементарных транзисторах металл-оксид-полупроводник) новых оптических и электрических функциональных средств, реализации высокоэффективных твердотельных осветительных устройств, производства концентраторных фотоэлектрических модулей, изготовления видеодетекторов, в частности - детекторов высокоэнергетических электромагнитных и корпускулярных излучений, и изготовления термоэлектрических устройств требуют - в той или иной форме - интеграции кристаллических материалов с различными параметрами кристаллических решеток при расположении их друг над другом. Принципиально это может быть осуществлено двумя различными способами - либо посредством сращивания пластин, либо посредством «гетероэпитаксиального наращивания». Настоящая работа относится ко второму способу соединения материалов, в частности - материалов, параметры кристаллических решеток которых отличаются более чем на несколько десятых процента, и которые могут очень сильно различаться по их коэффициентам термического расширения.

Проблемы, связанные с рассогласованием кристаллических решеток

Если два материала с рассогласованными кристаллическими решетками эпитаксиально наращивают друг на друга, то различие постоянных кристаллических решеток (несоответствие) приводит к механическому напряжению, которое при превышении определенного предела снимается за счет упругой или пластической релаксации. В нормальных условиях, если осажденный слой с достаточно большим несоответствием получают на единственной кристаллической подложке, релаксация напряжения может быть упругой - посредством изменения конфигурации поверхности, например - в форме островков. Тем не менее, упругая релаксация не может происходить на плоской пленке. В противоположность этому, при меньшем несоответствии эпитаксиальная пленка может оставаться плоской, тогда как напряжение снимается пластически за счет так называемых дислокации несоответствия, если превышена определенная критическая толщина пленки. В конечном счете, независимо от того, насколько большим является несоответствие, пластическая релаксация за счет дислокации несоответствия на межфазных границах происходит всегда. Если межфазная граница со значительной плотностью дислокации несоответствия находится в активной зоне устройства, например - транзистора, то его рабочие характеристики могут в значительной степени снижаться. Поэтому межфазные границы, содержащие дислокации несоответствия, обычно необходимо пространственно отделять от активной зоны устройства. Однако, к сожалению, удержание межфазных границ с дислокациями несоответствия на расстоянии от активной зоны устройства часто не гарантирует надлежащие рабочие характеристики устройства. На самом деле, редко случается, что дислокации локализованы исключительно на межфазной границе между двумя материалами в форме дислокации несоответствия. Дислокации несоответствия обычно сопровождаются винтовыми ветвями, идущими к поверхности наращиваемой пленки. Эти винтовые дисклокации также могут быть очень вредными для функционирования устройства, если они пересекают активную зону стопки гетероэпитаксиально наращиваемых слоев. Поэтому плотность винтовых дислокации обычно следует поддерживать на как можно более низком уровне.

Проблемы, связанные с рассогласованием коэффициентов термического расширения

Проблема дислокации, возникающая из-за несоответствия кристаллических решеток, является не единственным препятствием, которое необходимо преодолеть при эпитаксиальном наращивании разнородных материалов друг на друга. Во многих случаях столь же серьезной проблемой является несоответствие коэффициентов термического расширения, в частности - если необходимы слои с относительно большими толщинами, например - в устройствах типа высокоярких светодиодов, концентраторных фотоэлектрических модулей, детекторов радиации, термоэлектрических генераторов и т.п.

Несоответствие коэффициентов термического расширения может привести к прогибу подложки при охлаждении до комнатной температуры после эпитаксиального наращивания, к серьезному затруднению последующих стадий обработки, таких как фотолитография и паттернирование, или дальнейшего эпитаксиального наращивания. Различное термическое расширение эпитаксиальных слоев и подложки может даже привести к растрескиванию первых, либо непосредственно после эпитаксиального наращивания, либо во время последующего термоциклирования (циклического воздействия температуры), которое обязательно происходит, например, во время работы концентраторных фотоэлектрических модулей (см., например, публикацию V.K. Yang et al., Journal of Applied Physics 93, 3859 (2003), содержание которой полностью включено в настоящее описание посредством ссылки).

Проблему прогиба подложки в прошлом пытались решить различными способами. Один из подходов состоит во внедрении промежуточных слоев со сниженной кристалличностью, функционирующих в качестве слоев, снимающих напряжения (см., например, заявку на патент США под номером US 2008/0308909, авторы - Masahiro Sakai et al., содержание которой полностью включено в настоящее описание посредством ссылки). Другой подход включает в себя нанесение покрытия на обратную сторону подложки из субстрата, создающего противоположное напряжение при охлаждении подложки (см., например, заявку на патент США под номером US 2003/0033974, автор - Tetsuzo Ueda, содержание которой полностью включено в настоящее описание посредством ссылки). Однако, к сожалению, снижение прогиба подложки может даже увеличивать тенденцию нанесенных на нее слоев к растрескиванию, поскольку прогиб подложки сопровождается частичной упругой релаксацией напряжения.

Альтернативный способ снижения прогиба подложки был описан, например, в заявке на патент США под номером US 2008/0233716, автор - Kazuhide Abe, содержание которой полностью включено в настоящее описание посредством ссылки. В этом способе глубокие прорезы формировали в пленке из карбида кремния перпендикулярно направлению, вдоль которого возникал прогиб полупроводниковой пластины-носителя, за счет чего прогиб снижался.

В родственном подходе была разработана система, поглощавшая механическое напряжение, в которой прорезы глубиной около 10 мкм и шириной 1 мкм формировали в опорной подложке, на которую с транспортной подложки переносили нуклеационный слой с использованием способов сращивания пластин (см., например, заявку на патент США под номером US 2006/0216849, авторы - Letertre et al., содержание которой полностью включено в настоящее описание посредством ссылки). Для эффективного снятия напряжения во время колебаний температуры в толстых эпитаксиальных слоях, наращиваемых на нуклеационный слой, под нуклеационным слоем необходим дополнительный буферный слой, поглощающий напряжение и сходный с промежуточным слоем, описанным в заявке на патент США под номером US 2008/0308909, авторы - Masahiro Sakai et al., содержание которой полностью включено в настоящее описание посредством ссылки. Предполагается, что напряжения поглощаются за счет образования дефектов, локального смещения или сползания материала, в зависимости от природы буферного слоя. Требуется, чтобы эти механизмы снятия напряжения были очень эффективными, если необходимо исключить растрескивание слоев и прогиб подложки в случае толстых эпитаксиальных слоев с большими латеральными размерами, то есть распространяющихся по существу на всю подложку. Поэтому может происходить смещение или сползание материала на макроскопические расстояния, что очень нежелательно на практике.

То же самое относится к родственному подходу, в котором релаксацию напряжений несоответствия в эпитаксиальных слоях SiGe/Si(001) считают возникающей за счет процесса смещения; при этом эпислой SiGe остается кубическим. В этом случае используют тонкую SOI-основу вместо объемной кремниевой основы (см., например, патент США номер US 5759898, авторы - Ek et al., содержание которого полностью включено в настоящее описание посредством ссылки). Несмотря на сравнительно низкую вязкость при достаточно высоких температурах, представляется очень маловероятным то, что этот процесс смещения может когда-либо происходить в макроскопическом масштабе.

Несмотря на то, что прогиб подложки и растрескивание слоев являются серьезными практическими проблемами, обычно возникающими при толщинах слоев более 1 мкм, винтовые дислокации, тесно связанные с пластической релаксацией напряжений, обычно присутствуют и при меньших толщинах слоев вследствие значительных несоответствий кристаллических решеток, и их доля равна одному проценту и более.

Предпринималось много попыток снизить плотность винтовых дислокации (TDD, от англ. "threading dislocation densities") в поверхностных пленках, таких как изменение состава буферных слоев (см., например, патент US 5221413, авторы - Brasen et al., содержание которого полностью включено в настоящее описание посредством ссылки). Альтернативно, буферные слои с высокой плотностью дефектов могут способствовать образованию и аннигиляции дислокации (см., например, работу Н. Chen et al., Journal of Applied Physics 79, 1167 (1996), содержание которой полностью включено в настоящее описание посредством ссылки).

Другие способы включают в себя эпитаксиальный рост частей слоев при различных температурах подложки; одним из примеров является осаждение основного слоя Ge при низкой температуре подложки с последующим осаждением второго слоя Ge при более высокой температуре (см., например, патент США US 6,537,370, авторы - Hernandez et al., содержание которого полностью включено в настоящее описание посредством ссылки). Идея в данном случае состояла в том, чтобы по меньшей мере снизить образование островков по механизму Странски-Крастанова на ранней стадии роста, поскольку объединение островков и шероховатость поверхностей приводят к большей плотности винтовых дислокации (TDD).

Кроме того, показано, что термический отжиг после наращивания усиливает скольжение и аннигиляцию дислокации. Особенно эффективным, по-видимому, является циклический термический отжиг. В данном случае температура циклически изменяется между первым значением, превышающим температуру перехода от хрупкости к пластичности (т.е. близким к температуре плавления эпитаксиального слоя), и вторым значением, которое ниже первого. Значительное снижение плотности винтовых дислокации наблюдали, например, в Ge-пленках, эпитаксиально выращенных на Si(001) подложках с использованием такой процедуры (см., например, патент US 6635110, авторы Luan et al., содержание которого полностью включено в настоящее описание посредством ссылки). Однако этот способ не решает проблему с прогибом подложки и трещинообразованием, если Ge в форме поверхностных пленок наращивают до значительных толщин, равных нескольким микрометрам, и плотность винтовых дислокации остается очень высокой - обычно порядка 2·107 см-2 в пленках толщиной 1 мкм.

Решение проблем за счет ограничения площади эпитаксии с помощью диэлектрических масок

Если эпитаксиальные слои наращивают в форме непрерывных пленок на подложку, характеризующуюся значительным несоответствием кристаллической решетки и коэффициента термического расширения, то сталкиваются с проблемами избыточной плотности винтовых дислокации, как только напряжение несоответствия начинает пластически релаксировать, а также прогиба подложки и образования трещин при больших толщинах.

Уже давно стало понятно, что значительного снижения плотности винтовых дислокации можно достичь только за счет сокращения площади эпитаксиального роста, то есть за счет уменьшения эпитаксиальных структур. Этого можно добиться за счет получения подложки с диэлектрической маской, оставляющей поверхность подложки открытой только внутри отверстий, предварительно полученных посредством литографии и травления. Идея состоит в том, что при достаточной толщине слоя винтовые ветви, отходящие от межфазной границы, выходят из боковых сторон эпитаксиальной структуры и не достигают верхней поверхности.

Эта концепция была применена к различным комбинациям полупроводников, таким как Si, Ge, III-V материалы, II-VI материалы (см., например, заявку на патент Соединенного Королевства GB 215 514, авторы Goodfellow et al.). Сходным образом, концепция была применена к GaAs мезаструктурам, прорастающим в оксидные отверстия на Si(001) за счет молекулярно-пучковой эпитаксии (МВЕ, от англ. "molecular beam epitaxy") или химического осаждения из паровой (газовой) фазы (CVD, от англ. "chemical vapor deposition"), причем материал, осажденный на оксидную маску, удаляют на стадии химического травления (см., например, патент US 5158907, автор - Fitzgerald, содержание которого полностью включено в настоящее описание посредством ссылки). Показано, что этот способ, который также называют «эпитаксиальным утонением», не только эффективно снижает плотность винтовых дислокации в GaAs мезаструктурах, выращиваемых на Si посредством молекулярно-пучковой эпитаксии, но и устраняет трещины (см., например, работу Fitzgerald et al., Journal of Electronic Materials 20, 839 (1991), содержание которой полностью включено в настоящее описание посредством ссылки).

Идея создания дефектов, заканчивающихся на некристаллических боковых стенках известна не только под названием «эпитаксиального утонения», но и под названием «захвата за счет форматного соотношения» (ART, от англ. "aspect ratio trapping") (см., например, международную заявку на патент WO 2008/030574, авторы Bai et al., содержание которой полностью включено в настоящее описание посредством ссылки). Также было показано, что ограничение площади эпитаксиального роста, в сочетании с циклическим термическим отжигом, указанным выше, приводит к резкому снижению плотности винтовых дислокации в Ge мезаструктурах, эпитаксиально выращиваемых на Si(001) (см., например, патент US 6635110, авторы Luan et al., содержание которого полностью включено в настоящее описание посредством ссылки).

Однако ограничения площади эпитаксии, даже в сочетании с термическим отжигом, недостаточно для полного устранения винтовых дислокации, даже если топологические размеры поддерживаются очень малыми. Чтобы понять это, необходимо проанализировать природу дислокации. В кубических полупроводниках наиболее распространенными дислокациями являются так называемые 60-градусные дислокации, в которых векторы Бюргерса и линии дислокации образуют между собой угол, равный 60 градусам, и расположены в плоскостях скольжения {111} (см., например, работу Blakeslee, Mat. Res. Soc. Symp.Proc. 148, 217 (1989), содержание которой полностью включено в настоящее описание посредством ссылки). Такие дислокации могут достигать края эпитаксиальных областей за счет скольжения под действием напряжения или просто достигать межфазной границы с диэлектриком, когда эпитаксиальная структура становится достаточно высокой, так что их плоскость скольжения больше не пересекает фронт роста. Однако существуют также так называемые сидячие дислокации с линиями дислокации, перпендикулярными межфазной границе. На них не влияют напряжения, и отклонение от вертикальной ориентации может быть вызвано только взаимодействием с наклонными поверхностными гранями. Действительно, было показано, что механизм отклонения дислокации существует в ограненных GaN островках и может привести к значительному снижению плотности винтовых дислокации (см., например, работу Knoke et al., J. Cryst. Growth 310, 3351 (2008), содержание которой полностью включено в настоящее описание посредством ссылки). Ожидается, что поверхностная огранка оказывает такой же эффект на полупроводники IV группы и составные полупроводники (см., например, международную заявку на патент WO 2008/030574, авторы - Bai et al., содержание которой полностью включено в настоящее описание посредством ссылки).

Вместо формирования ограниченных эпитаксиальных областей в форме мезаструктур было показано, что большие области гетероэпитаксии материалов с рассогласованными кристаллическими решетками с низкой плотностью винтовых дислокации можно получить посредством внедрения дислокационных стоков в форме ямок в подложке. Это обеспечивает дополнительное преимущество по существу плоских поверхностей (см., например, заявку на Европейский патент ЕР 0505093, авторы - Bean et al., содержание которой полностью включено в настоящее описание посредством ссылки).

Дальнейшее расширение технологии снижения плотности винтовых дислокации включает в себя сочетание описанного паттернирования с помощью диэлектрических масок с селективной эпитаксией с последующим эпитаксиальным латеральным наращиванием (ELO, от англ. "epitaxial lateral overgrowth"). Например, для Ge на Si(001) было высказано предположение, что за счет продолжения процесса до коалесценции можно получить по существу не содержащие дефектов поверхностные пленки (см., например, работу Langdo et al., Applied Physics Letters 76, 3700 (2000), содержание которой полностью включено в настоящее описание посредством ссылки). Однако очевидно, что проблемы с прогибом подложки и растрескиванием слоев могут возникнуть при дальнейшем увеличении толщины слоя.

Кроме того, для того чтобы эпитаксиальное утонение было эффективным, форматное соотношение между высотой и шириной отверстий маски должно быть примерно равно единице. Поэтому для пленок с толщинами менее примерно 1 мкм необходимо использовать субмикронную литографию для определения размера отверстий маски. Еще меньшие размеры отверстий необходимы в том случае, если упругая релаксация может вносить значительный вклад в релаксацию напряжений несоответствия (см., например, заявку на патент США US2008001169, авторы Lochtefeld et al., содержание которой полностью включено в настоящее описание посредством ссылки).

Все способы, основанные на эпитаксиальном врастании в отверстия в диэлектрике, дополнительно ограничены высотами боковых стенок отверстия, так как невозможно изготовить маску произвольной толщины. Это также ограничивает высоты областей, где может происходить захват дислокации.

Еще один альтернативный подход включает в себя использование селективного эпитаксиального роста на выступах кристаллического материала основы, окруженных диэлектрической маской, а не врастание в ямки, сформированные в такой маске. В этом подходе на Si основе формируют буферный слой из Si нанопроволок, причем нанопроволоки расположены перпендикулярно поверхности основы и окружены диэлектрическим материалом, из которого они выступают. Составной полупроводник селективно осаждают на концы нанопроволок, после чего выполняют эпитаксиальное латеральное наращивание (ELO) до образования сплошного слоя составного полупроводника (см., например, заявку на патент US 2008149941, авторы Li et al., содержание которой полностью включено в настоящее описание посредством ссылки). Хотя этот подход также может быть эффективным в отношении снижения плотности винтовых дислокации в слое составного полупроводника, он не может устранить проблемы, связанные с несоответствием коэффициентов термического расширения, когда слой составного полупроводника занимает всю поверхность подложки. Как описано выше, слой составного полупроводника может проскальзывать по основе на макроскопические расстояния во время охлаждения от температуры наращивания. Это не может произойти на практике, так как слой диэлектрика не является сколь угодно мягким, а Si нанопроволоки способны выдерживать сдвиговые усилия, возникающие во время охлаждения.

Технология, описанная выше, а именно - паттернирование основы, предусматривающее «эпитаксиальное утонение» или ART, была использована для изготовления электронных и оптоэлектронных устройств, изготовленных из материалов с рассогласованными кристаллическими решетками (см., например, заявку на патент US 2009039361, авторы Li et al., содержание которой полностью включено в настоящее описание посредством ссылки).

Возможность замены Ge-подложек Si-подложками в качестве основ для многопереходных солнечных элементов была признана еще одним важным применением ART. Это применение предполагает эпитаксиальное наращивание относительно толстых стопок слоев, если элементы не наращивают на обеих сторонах основы. В этом втором подходе, примером которого являются трехпереходные солнечные элементы, субэлемент с наибольшей шириной запрещенной зоны обычно изготовлен из InGaP посредством ART-процесса на нижней поверхности основы (см., например, заявку на патент US 2009065047, авторы Fiorenza et al., содержание которой полностью включено в настоящее описание посредством ссылки). Подход с изготовлением субэлементов на обеих сторонах Si-подложки минимизирует проблему термического растрескивания слоев из-за относительно тонких эпислоев. Узкие канавки шириной 300-500 нм, обычно используемые в ART-способе, кроме того, могут обеспечивать некоторую упругую релаксацию, как и несколько податливая природа SiO2 маски. Однако, с учетом частого термоциклирования (циклического воздействия температуры) во время работы солнечных элементов, структура, обладающая латерально варьирующимися термическими свойствами, может быть недостатком. Кроме того, концепция требует использования «смачивающих» слоев, которые, в дополнение к областям, захватывающим дислокации, поглощают часть солнечного излучения, снижая за счет этого эффективность солнечных элементов.

Проблемы с несоответствием коэффициентов термического расширения становятся более значительными, если многопереходные солнечные элементы наращивают на одной стороне Si-основы с использованием ART и ELO процессов. Было предложено заменить стандартные трехпереходные элементы с нижним субэлементом, изготовленным из Ge, трехпереходным элементом, в котором все субэлементы изготовлены исключительно из III-V материалов (см., например, международную заявку на патент WO 2010/033813, авторы Fiorenza et al., содержание которой полностью включено в настоящее описание посредством ссылки). Хотя Ge в этом типе элементов больше не является активным материалом, тем не менее, было предложено формировать первый сплошной Ge слой с использованием ART+ELO процесса перед наращиванием стопки активных III-V слоев. Однако сращивание сопровождается образованием высокой плотности винтовых дислокации в тех областях, где встречаются фронты роста от соседних отверстий. Эта серьезная проблема, возникающая при формировании непрерывного слоя ART+ELO способом, до настоящего времени не решена (см., например, работу Fiorenza et al., ECS Transactions 33, 963 (2010), содержание которой полностью включено в настоящее описание посредством ссылки). Кроме того, общая толщина объединенного Ge-слоя и активных III-V слоев должна быть не менее 5 мкм, так что можно ожидать, что прогиб подложки и растрескивание слоев станут серьезными препятствиями во время дальнейшей обработки устройства и во время работы солнечного элемента.

Наращивание на безмасковых паттернированных поверхностях

Подходы, ведущие к получению сплошных слоев

В альтернативном классе процедур паттернирования материал диэлектрической маски удаляют с пластины-подложки до начала эпитаксиального наращивания" или, альтернативно, выполняют паттернирование вообще без использования маски. Для Si-основ это возможно при использовании электрохимического процесса, называемого анодизацией, за счет которого образуется пористый Si. Такие пористые Si-основы использовали для получения слоев нитридов III группы, причем слой Ge осаждали на пористую Si-основу до слоев составных полупроводников (см., например, заявку на патент US 2005199883, авторы Borghs et al., содержание которой полностью включено в настоящее описание посредством ссылки). Предполагается, что этот промежуточный слой Ge снижает термическое напряжение, возникающее из-за разницы в параметрах термического расширения Si-основы и материала, являющегося нитридом III группы. С другой стороны, пористый слой Si должен согласовывать большое несоответствие кристаллических решеток Si-основы и слоя нитрида. В результате в нитридной пленке должно присутствовать меньше дислокации, и можно избежать растрескивания слоев и прогиба основы. Хотя эти аргументы являются значимыми в малом масштабе, они в значительной степени теряют значимость на уровне подложки, так как непрерывный слой нитрида III Группы может соскальзывать по основе на макроскопические расстояния во время охлаждения от температуры наращивания.

Альтернативно, эпитаксиальный слой можно вначале нарастить на плоской основе. После этого в слое протравливают полосы таким образом, что удаляют часть основы между оставшимися полосами. В ходе последующего процесса селективного роста материал наращивается латерально от оставшихся полос, образуя подвешенную пленку над вытравленными областями основы. Этот процесс, называемый «кантилеверной эпитаксией» или «пендеоэпитаксией» (англ. - "pendeo-epitaxy"), был вначале использован для получения эпитаксиальных GaN слоев на SiC основах (см., например, работу Т. Ярудумф ye al., Journal of Electronic Materials 28, L5 (1999), содержание которой полностью включено в настоящее описание посредством ссылки). Хотя в процессе пендеоэпитаксии может резко снижаться плотность винтовых дислокации, все же проблемы, связанные с несоответствием коэффициентов термического расширения, сохраняются по тем же причинам, что и в других подходах, в которых на термически несоответствующей основе в конечном итоге формируют непрерывные слои.

В следующем подходе основу паттернируют таким образом, что формируют совокупность непрочных столбиков субмикронного размера с форматным соотношением больше 0,5. Затем на верхней стороне столбиков выращивают непрерывный слой GaN с использованием пендеоэпитаксиальных способов (см., например, патент US 6380108, авторы Linthicum et al., содержание которого полностью включено в настоящее описание посредством ссылки). Непрочные столбики имеют такую конфигурацию, чтобы они растрескивались из-за несоответствия коэффициентов термического расширения основы и слоя GaN. Поэтому при охлаждении от температуры наращивания по меньшей мере некоторые из непрочных столбиков должны растрескиваться, снимая таким образом напряжение в слое GaN. Проблема здесь снова состоит в том, что для того чтобы обеспечить эффективность в масштабе подложки, должно растрескаться большинство столбиков, что приводит к отделению слоя от основы. Хотя это может быть желательным в некоторых прикладных задачах, невозможно избежать отделения слоя и одновременно снять напряжения в масштабе подложки, опять-таки по тем же причинам, которые указаны выше.

Подходы с использованием наностержней

Как указано выше, независимо от особенностей процедуры изготовления, на предшествующем уровне техники почти невозможно значительно снизить плотность винтовых дислокации и избежать растрескивания слоев и прогиба подложки в случае непрерывных слоев, кроме тех случаев, когда общую толщину слоя поддерживают сравнительно малой. Если исключить сдерживающий фактор, связанный с ограниченной толщиной пленки, то единственная возможность решить все эти проблемы состоит в том, чтобы одновременно исключить формирование непрерывного слоя. Кроме решения практических проблем, связанных с растрескиванием слоев, прогибом подложки и снижением плотности дислокации, использование прерывистых пленок может обеспечить и другие преимущества. Одним из таких преимуществ является возможность увеличить содержание In в активном слое светодиодов на основе нитридов III группы без снижения внутренней квантовой эффективности и с одновременным обеспечением большей эффективности светоизлучения, как показано для квантово-размерных активных областей InGaN, включенных в наностержни GaN (см., например, заявку на патент US 2007077670, авторы Kim et al., содержание которой полностью включено в настоящее описание посредством ссылки).

В последнем примере на плоские сапфировые подложки вначале наращивают буферный слой GaN с использованием MOCVD процесса (сокр. от англ. "metal organic chemical vapor deposition" - химическое осаждение из паровой (газовой) фазы металлоорганических соединений), известного специалистам в данной области техники. Затем формируют наностержни за счет использования низких температур основы, способствующих превышению вертикального роста над латеральным.

Вместо того чтобы сохранить спонтанную нуклеацию наностержней, был обеспечен прецизионный контроль их положения в наносветодиодах за счет паттернирования основы перед наращиванием нитридного полупроводника. Это было продемонстрировано, например, на Si(111)-основах, паттернированных в форме совокупности столбиков субмикронного размера с высотой порядка 5 мкм. В этой работе, соответствующей предшествующему уровню техники, высота эпитаксиальных структур, сформированных на безмасковых основах, была относительно малой (менее 2 микрометров), и MOCVD-осаждение происходило равномерно между Si-столбиками (см., например, работу Fundling et al., Physica Status Solidi A 206, 1194 (2009), содержание которой полностью включено в настоящее описание посредством ссылки). Для системы материалов AlGaN/InGaN необходимы условия роста с обогащением азотом и молекулярно-пучковая эпитаксия (МВЕ, от англ. "molecular beam epitaxy") с плазменной активацией, которые способствуют превышению вертикального роста над латеральным в той степени, которая необходима для выращивания нанопроволок (см., например, работу Stoica et al., Small 4, 751 (2008), содержание которой полностью включено в настоящее описание посредством ссылки). Однако для многих устройств желательно получить высоты структур, превышающие один микрометр. Некоторые устройства требуют заметно большей высоты (или толщины слоя); это многопереходные солнечные элементы, в частности, например, трехпереходные солнечные элементы стандартного типа, в которых нижний субэлемент сформирован из Ge. Еще более высокие структуры, высота которых составляет несколько дюжин микрометров, необходимы, например, для детекторов рентгеновского излучения.

Обнаружено, что привлекательным способом обеспечения столбчатого роста в системе материалов AlGaN/InGaN является эпитаксия из паровой фазы с активацией низкоэнергетической плазмой (LEPEVPE, от англ. " low-energy plasma-enhanced vapour phase epitaxy") (см., например, WO 2006/097804, автор - Kanel, содержание которой полностью включено в настоящее описание посредством ссылки).

Задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором слои полупроводников с согласованными и рассогласованными кристаллическими решетками можно было бы наращивать эпитаксиально в безмасковом процессе на предварительно паттернированные основы.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором слои полупроводников можно было бы наращивать эпитаксиально в безмасковом процессе на. предварительно паттернированные основы с другими коэффициентами термического расширения.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором слои полупроводников с рассогласованными кристаллическими решетками и низкой плотностью винтовых дислокации можно было бы наращивать эпитаксиально в безмасковом процессе на предварительно паттернированные основы.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором слои полупроводников с рассогласованными коэффициентами термического расширения и не содержащие трещин можно было бы наращивать эпитаксиально в безмасковом процессе на предварительно паттернированные основы.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором слои полупроводников с рассогласованными коэффициентами термического расширения можно было бы наращивать эпитаксиально в безмасковом процессе на предварительно паттернированные основы без возникновения прогиба основы.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ, в котором наращивание слоев полупроводников с рассогласованными кристаллическими решетками и рассогласованными коэффициентами термического расширения ограничены приподнятыми участками предварительно паттернированных основ.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления полупроводниковых светоизлучающих диодных структур, монолитно наращенных на основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления микроэлектронных схем, монолитно наращенных на предварительно паттернированные основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления полупроводниковых лазерных структур, монолитно наращенных на предварительно паттернированные основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления видеодетекторов, таких как инфракрасные и рентгеновские пиксельные детекторы, монолитно наращенных на предварительно паттернированные основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления термоэлектрических структур, монолитно наращенных на предварительно паттернированные основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления многопереходных солнечных элементов, монолитно наращенных на предварительно паттернированные основы с рассогласованными коэффициентами термического расширения и кристаллическими решетками в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления монолитно наращенных устройств, требующих полупроводниковых слоев с рассогласованными кристаллическими решетками и/или коэффициентами термического расширения на предварительно паттернированных основах, обработанных с использованием КМОП-технологии, в безмасковом процессе.

Следующая задача настоящего изобретения состоит в том, чтобы обеспечить способ изготовления монолитно наращенных устройств, требующих полупроводниковых слоев с рассогласованными кристаллическими решетками и/или коэффициентами термического расширения, с использованием специальной КМОП-технологии.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение обеспечивает способ изготовления стопок активных слоев полупроводниковых материалов с согласованными параметрами кристаллических решеток, рассогласованными параметрами кристаллических решеток и рассогласованными коэффициентами термического расширения в бе