Способ и устройство для декодирования турбокода

Иллюстрации

Показать всеИзобретение относится к технике связи и предназначено для декодирования турбокода. Технический результат - сокращение задержки декодирования и повышение скорости декодирования. В каждой процедуре итерации при выполнении многопутевого параллельного декодирования декодируемых кодовых блоков способ включает: для декодируемых кодовых блоков в текущем пути, получение модулем декодирования всех первых промежуточных переменных текущего пути посредством рекуррентного вычисления от начала к концу и в то же самое время получение всех вторых промежуточных переменных текущего пути посредством рекуррентного вычисления от конца к началу; получение модулем декодирования всех логарифмических отношений правдоподобия текущего пути (LLR) согласно всем полученным первым промежуточным переменным и вторым промежуточным переменным, а также всем метрикам ветвей декодируемых кодовых блоков; и получение модулем декодирования априорной информации и результата декодирования, выводимого текущим путем, согласно всем логарифмическим отношениям правдоподобия. В каждом параллельном пути модулей декодирования два вида промежуточных переменных вычисляют одновременно посредством рекуррентного вычисления от начала к концу и рекуррентного вычисления от конца к началу. 2 н. и 11 з.п. ф-лы, 9 ил.

Реферат

Область техники

Данное изобретение относится к области связи, в частности к способу и устройству для декодирования турбокода.

Предпосылки создания изобретения

Турбокоды стали широко применяться в системах радиосвязи с тех пор, как были предложены в 1993 г., из-за их превосходных рабочих характеристик, приближающихся к шенноновскому пределу, и были определены в качестве одной из схем канального кодирования/декодирования системы подвижной связи по стандартам Проекта сотрудничества по созданию системы подвижной связи третьего поколения (Third Generation Partnership Project, сокращенно 3GPP). В системе по стандарту долгосрочной эволюции (Long Term Evolution, сокращенно LTE) требуются более высокая скорость передачи и лучшая характеристика кода в отношении вероятности ошибки, и поэтому соответственно возрастают требования к канальному кодированию/декодированию. Однако из-за итеративного характера алгоритма декодирования турбокода его может быть проблематично реализовать аппаратными средствами, в которых наиболее важна скорость декодирования. Поэтому уменьшение сложности декодирования и задержки декодирования становится важной проблемой в случае аппаратной реализации, и рассмотрение компромисса между рабочими характеристиками и требуемыми ресурсами является ключом к внедрению турбокодов.

В соответствующей области техники для декодирования турбокода обычно используют алгоритм на основе максимума апостериорной вероятности (Maximum of A-posteriori Probability, MAP), такой как log-MAP или MAX-log-MAP. Важными особенностями этого алгоритма является то, что при аппаратной реализации он требует непрерывно выполнять итерации множество раз и также требует выполнять рекуррентную итерацию промежуточных переменных alpha (альфа) и beta (бета) во время каждой итерации. Эти особенности увеличивают системную задержку декодирования турбокода, что является неудобным для применения турбокода в высокоскоростных системах подвижной связи третьего поколения (Third Generation Mobile System, 3G) и LTE. В отношении этой проблемы предложенным решением в соответствующей области техники в настоящее время является использование многопутевого параллельного способа декодирования; в этом способе принимаемые данные разделяют на множество блоков согласно ограниченной длине кода и фактической длине входных данных, принимаемые данные декодируют одновременно и посылают соответствующим контроллерам коэффициента ошибок после того, как одно декодирование закончено, чтобы вычислить его коэффициенты ошибок. В этом способе во время обработки каждым параллельным модулем декодирования соответственно вычисляют промежуточные переменные (alpha и beta), и поэтому время декодирования является относительно длительным.

Другим решением, используемым в соответствующей области техники, является способ декодирования турбокода на основании управления скользящим окном, при этом целью выполнения управления на основании скользящего окна является экономия объема памяти для промежуточных переменных (alpha и beta), но проблема аппаратной реализации, вызванная рекуррентным вычислением промежуточных переменных, не решается.

Сущность изобретения

Данное изобретение предлагает способ и устройство для декодирования турбокода, которые могут решить, по меньшей мере, проблему соответствующей области техники, состоящую в том, что задержка декодирования является слишком длительной и скорость декодирования невысока из-за того, что промежуточные переменные являются рекуррентными и вычисляются соответствующим образом.

Согласно одному аспекту данного изобретения предлагается способ декодирования турбокода, в котором в каждой процедуре итерации при выполнении многопутевого параллельного декодирования декодируемых кодовых блоков, когда модуль декодирования каждого пути выполняет декодирование, способ включает: для декодируемых кодовых блоков в текущем пути получение модулем декодирования всех первых промежуточных переменных текущего пути посредством рекуррентного вычисления от начала к концу и в то же самое время получение всех вторых промежуточных переменных текущего пути посредством рекуррентного вычисления от конца к началу; получение модулем декодирования всех логарифмических отношений правдоподобия текущего пути согласно всем полученным первым промежуточным переменным, вторым промежуточным переменным и всем метрикам ветвей декодируемых кодовых блоков; и получение модулем декодирования априорной информации и вывод результата декодирования текущего пути согласно всем логарифмическим отношениям правдоподобия.

Предпочтительно получение модулем декодирования всех первых промежуточных переменных текущего пути посредством рекуррентного вычисления от начала к концу и в то же самое время получение всех вторых промежуточных переменных текущего пути посредством рекуррентного вычисления от конца к началу включает: получение модулем декодирования всех метрик ветвей текущего пути посредством рекуррентного вычисления от начала к концу и получение всех первых промежуточных переменных текущего пути посредством рекуррентного вычисления от начала к концу согласно всем полученным метрикам ветвей; и в то же самое время получение модулем декодирования всех метрик ветвей текущего пути посредством рекуррентного вычисления от конца к началу и получение всех вторых промежуточных переменных текущего пути посредством рекуррентного вычисления от конца к началу согласно всем метрикам ветвей, полученным в этот раз.

Предпочтительно получение модулем декодирования всех первых промежуточных переменных текущего пути посредством рекуррентного вычисления от начала к концу согласно всем полученным метрикам ветвей включает: при рекуррентном вычислении первой, считая от начала к концу, из первых промежуточных переменных передней половины декодируемых кодовых блоков текущего пути, после выполнения операции суммирования, во время выполнения операции нормализации выполнение модулем декодирования операции суммирования для рекуррентного вычисления первой, считая от начала к концу, из первых промежуточных переменных задней половины декодируемых кодовых блоков; и выполнение модулем декодирования операции суммирования для рекуррентного вычисления второй, считая от начала к концу, из первых промежуточных переменных передней половины и в то же самое время выполнение операции нормализации первой, считая от начала к концу, из первых промежуточных переменных задней половины, затем выполнение операции суммирования для второй, считая от начала к концу, из первых промежуточных переменных задней половины, в то же время выполнение операции нормализации второй, считая от начала к концу, из первых промежуточных переменных передней половины и так далее, чтобы получить все первые промежуточные переменные текущего пути посредством рекуррентного вычисления.

Предпочтительно получение модулем декодирования всех вторых промежуточных переменных текущего пути посредством рекуррентного вычисления от конца к началу согласно всем полученным метрикам ветвей включает: при рекуррентном вычислении первой, считая от конца к началу, из вторых промежуточных переменных задней половины декодируемых кодовых блоков текущего пути, после выполнения операции суммирования, во время выполнения операции нормализации, выполнение модулем декодирования операции суммирования для рекуррентного вычисления первой, считая от конца к началу, из вторых промежуточных переменных передней половины текущего пути декодируемых кодовых блоков; и выполнение модулем декодирования операции суммирования для рекуррентного вычисления второй, считая от конца к началу, из вторых промежуточных переменных задней половины, и в то же самое время выполнение операции нормализации первой, считая от конца к началу, из вторых промежуточных переменных передней половины, и выполнение операции суммирования для второй, считая от конца к началу, из вторых промежуточных переменных передней половины, и в то же время выполнение операции нормализации второй, считая от конца к началу, из вторых промежуточных переменных задней половины, и так далее, чтобы получить все вторые промежуточные переменные текущего пути посредством рекуррентного вычисления.

Предпочтительно способ дополнительно включает: сохранение в памяти модулем декодирования первых промежуточных переменных, соответствующих передней половине кодовых блоков передней половины, и первых промежуточных переменных, соответствующих передней половине кодовых блоков задней половины; и сохранение в памяти модулем декодирования вторых промежуточных переменных, соответствующих задней половине кодовых блоков задней половины, и вторых промежуточных переменных, соответствующих задней половине кодовых блоков передней половины.

Предпочтительно получение модулем декодирования всех логарифмических отношений правдоподобия текущего пути согласно всем полученным первым промежуточным переменным и вторым промежуточным переменным и всем метрикам ветвей декодируемых кодовых блоков, включает:

при рекуррентном вычислении первых промежуточных переменных, соответствующих задней половине кодовых блоков передней половины, и первых промежуточных переменных, соответствующих задней половине кодовых блоков задней половины, каждый раз при получении одной из первых промежуточных переменных посредством рекуррентного вычисления, считывание модулем декодирования хранящейся второй промежуточной переменной, соответствующей этой позиции, и получение одного логарифмического отношения правдоподобия, соответствующего этой позиции, согласно первой промежуточной переменной, второй промежуточной переменной и метрике ветви, соответствующих этой позиции; и

при рекуррентном вычислении вторых промежуточных переменных, соответствующих передней половине кодовых блоков задней половины, и вторых промежуточных переменных, соответствующих передней половине кодовых блоков передней половины, каждый раз при получении одной из вторых промежуточных переменных посредством рекуррентного вычисления, считывание модулем декодирования хранящейся первой промежуточной переменной, соответствующей этой позиции, и получение одного логарифмического отношения правдоподобия, соответствующего этой позиции, согласно второй промежуточной переменной, первой промежуточной переменной и метрике ветви, соответствующих этой позиции.

Предпочтительно после получения результата декодирования каждого пути способ дополнительно включает: выполнение проверки при помощи циклического кода (cyclic redundancy check, CRC) согласно результату декодирования каждого пути и коду CRC декодируемых кодовых блоков, и если результат проверки удовлетворительный, то остановка итерации и завершение процесса декодирования, а в противном случае - выполнение следующего итерационного процесса с использованием априорной информации, выводимой каждым путем.

Согласно другому аспекту данного изобретения предлагается устройство для турбокода, содержащее модули декодирования многочисленных путей, причем модуль декодирования каждого пути содержит: модуль рекуррентного вычисления, сконфигурированный так, чтобы для декодируемых кодовых блоков в текущем пути получать все первые промежуточные переменные текущего пути посредством рекуррентного вычисления от начала к концу и в то же самое время получать все вторые промежуточные переменные текущего пути посредством рекуррентного вычисления от конца к началу; модуль вычисления логарифмического отношения правдоподобия (LLR), сконфигурированный так, чтобы получать все отношения LLR текущего пути согласно всем полученным первым промежуточным переменным и вторым промежуточным переменным и всем метрикам ветвей декодируемых кодовых блоков; и модуль жесткого решения, сконфигурированный так, чтобы принимать жесткое решение относительно всех отношений LLR, полученных модулем вычисления LLR, и выводить результат жесткого решения в качестве результата декодирования.

Предпочтительно модуль рекуррентного вычисления содержит: первый модуль вычисления метрик ветвей, сконфигурированный, чтобы получать все метрики ветвей текущего пути посредством рекуррентного вычисления от начала к концу; первый модуль вычисления промежуточной переменной, сконфигурированный, чтобы получать все первые промежуточные переменные текущего пути посредством рекуррентного вычисления от начала к концу согласно всем метрикам ветвей, полученным первым модулем вычисления метрик ветвей; второй модуль вычисления метрик ветвей, сконфигурированный, чтобы получать все метрики ветвей текущего пути посредством рекуррентного вычисления от конца к началу; и второй модуль вычисления промежуточной переменной, сконфигурированный, чтобы получать все вторые промежуточные переменные текущего пути посредством рекуррентного вычисления от конца к началу согласно всем метрикам ветвей, полученным вторым модулем вычисления метрик ветвей.

Предпочтительно первый модуль вычисления промежуточной переменной содержит: первый блок суммирования и первый блок нормализации, причем первый блок суммирования сконфигурирован, чтобы выполнять операцию суммирования в процессе рекуррентного вычисления каждой из первых промежуточных переменных; а первый блок нормализации сконфигурирован, чтобы выполнять операцию нормализации в процессе рекуррентного вычисления каждой из первых промежуточных переменных.

Предпочтительно второй модуль вычисления промежуточной переменной содержит: второй блок суммирования и второй блок нормализации, причем второй блок суммирования сконфигурирован, чтобы выполнять операцию суммирования в процессе рекуррентного вычисления каждой из вторых промежуточных переменных; а второй блок нормализации сконфигурирован, чтобы выполнять операцию нормализации в процессе рекуррентного вычисления каждой из вторых промежуточных переменных.

Предпочтительно модуль декодирования дополнительно содержит: модуль памяти, сконфигурированный для хранения первых промежуточных переменных, соответствующих передней половине кодовых блоков передней половины, и первых промежуточных переменных, соответствующих первой половине кодовых блоков задней половины, а также вторых промежуточных переменных, соответствующих задней половине кодовых блоков задней половины, и вторых промежуточных переменных, соответствующих задней половине кодовых блоков передней половины.

Предпочтительно устройство дополнительно содержит: выходной модуль управления, сконфигурированный, чтобы выполнять проверку при помощи циклического кода (CRC) согласно результату декодирования каждого пути и коду CRC декодируемых кодовых блоков, и если результат проверки удовлетворительный, то останавливать итерацию и завершать процесс декодирования, а иначе выполнять следующий итерационный процесс, используя априорную информацию, выводимую каждым путем.

Посредством данного изобретения в каждом параллельном пути модулей декодирования две промежуточные переменные вычисляют одновременно посредством рекуррентного вычисления от начала к концу и посредством рекуррентного вычисления от конца к началу, соответственно, решая проблему существующего способа параллельного декодирования, состоящую в том, что время каждой итерации слишком длительное, и, таким образом, значительно сокращая задержку декодирования и улучшая скорость декодирования.

Краткое описание чертежей

Чертежи, приводимые для дальнейшего пояснения данного изобретения и составляющие часть описания, используются, чтобы объяснить данное изобретение вместе с формами его осуществления, а не ограничивать данное изобретение. На чертежах:

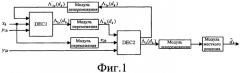

Фиг.1 - основная схема декодирования турбокода.

Фиг.2 - схема аппаратной структуры декодера турбокода.

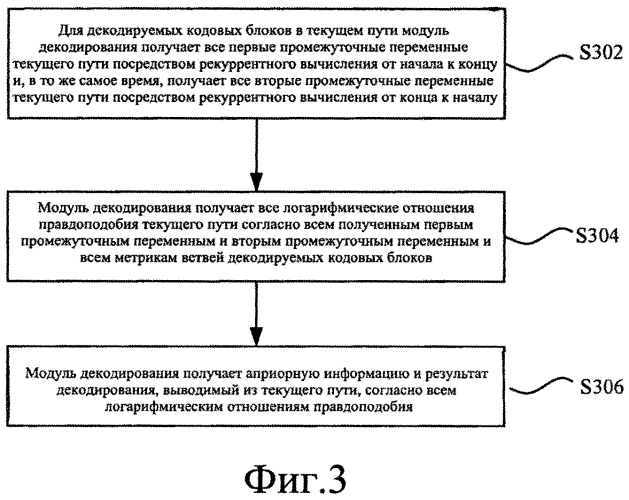

Фиг.3 - блок-схема способа декодирования турбокода согласно форме осуществления данного изобретения.

Фиг.4 - схема многопутевого параллельного декодирования согласно форме осуществления данного изобретения.

Фиг.5 - схема потока обработки второго пути в многочисленных параллельных путях согласно форме осуществления данного изобретения.

Фиг.6 - структурная схема модуля декодирования в декодере турбокода согласно форме осуществления данного изобретения.

Фиг.7 - структурная схема модуля рекуррентного вычисления согласно предпочтительной форме осуществления данного изобретения.

Фиг.8 - структурная схема модуля рекуррентного вычисления согласно другой предпочтительной форме осуществления данного изобретения.

Фиг.9 - схема аппаратной структуры модуля декодирования согласно предпочтительной форме осуществления данного изобретения.

Подробное описание форм осуществления изобретения

Данное изобретение подробно описывается ниже со ссылкой на прилагаемые чертежи и формы осуществления изобретения. Обратим внимание на то, что формы осуществления данного изобретения и признаки форм осуществления изобретения могут комбинироваться друг с другом, если при этом не возникает противоречия.

Фиг.1 - основная принципиальная схема декодирования турбокода, и, как показано на фиг.1, априорная информация (xk) и контрольные биты 1 (y1k) вводятся в модуль декодирования 1 (DEC1). Для способа декодирования, использующего алгоритм log-MAP или MAX-log-MAP, вычисление МАР1 выполняется над входными кодовыми блоками, которые будут декодированы в DEC1, и затем результат вводится в модуль перемежения для перемежения, и далее вводится в модуль декодирования 2 (DEC2), вычисление МАР2 выполняется над результатом перемежения и входными контрольными битами 2 (y2k), и результат выводится модулем деперемежения или вводится в модуль декодирования 1 в качестве априорной информации.

Фиг.2 - принципиальная схема аппаратной структуры декодера турбокода, и, как показано на фиг.2, это устройство в основном содержит: входной модуль управления, модуль системных битов/контрольных битов/априорной информации, модуль перемежения, модуль декодирования (DEC), модуль управления декодированием и выходной модуль управления.

Входной модуль управления отвечает в основном за различение данных, вводимых в декодер турбокода, согласно данным системных битов, контрольных битов 1, контрольных битов 2, системным хвостовым битам, перемеженным системным хвостовым битам, контрольным хвостовым битам 1 и контрольным хвостовым битам 2 и в то же самое время за генерацию сигнала управления выбором соответствующей интегральной схемы и управления операцией записи в оперативное запоминающее устройство (random-access memory, RAM) системных битов и RAM контрольных битов.

Модуль системных битов/контрольных битов/априорной информации выполняет операцию чтения/записи системных битов, контрольных битов и априорной информации, соответственно. Декодируемые данные из входного модуля управления записываются в соответствующие устройства RAM согласно степени параллельного декодирования. После того как декодирование активизировано, данные считываются из соответствующих устройств RAM согласно адресу последовательности/перемежения и передаются в модуль декодирования для декодирования.

Модуль перемежения обеспечивает адреса перемежения в реальном времени так, чтобы декодер турбокода мог получать перемежаемые системные биты и априорную информацию при вычислении МАР2, и таким образом вычислять текущую априорную информацию, и записывать априорную информацию в устройство RAM хранения априорной информации.

Модуль декодирования в основном выполняет декодирование согласно данным, выводимым модулем системных битов/контрольных битов/априорной информации, записывает данные априорной информации, полученные при вычислении, обратно в устройство RAM хранения априорной информации и посылает результат декодирования выходному модулю управления.

Модуль управления декодированием управляет работой всего ядра декодирования турбокода и отвечает за генерирование сигналов запуска декодирования, параметров, связанных с кодовыми блоками, сигналов разрешения чтения/записи данных, адресов, сигналов управления попеременным переключением и сигналов разрешения вычисления и так далее.

Выходной модуль управления отвечает за деперемежение результата декодирования кодовых блоков, управление чтением/ записью и вывод соответствующих параметров.

Если взять в качестве примера кодовый блок длиной K, то процесс декодирования турбокода будет включать следующие основные шаги.

Шаг 1, входные данные декодирования (всего 3K+12) после обработки входным модулем управления разделяются на K системных битов, K контрольных битов 1, К контрольных битов 2, 3 системных хвостовых бита, 3 перемежаемых системных хвостовых бита, 3 хвостовых бита проверки 1 и 3 хвостовых бита проверки 2 и сохраняются в соответствующих устройствах RAM согласно числу блоков обработки (processing unit, PU).

Шаг 2, после того как данные записаны полностью, подается сигнал пуска (start) и начинается многопутевое параллельное декодирование.

Шаг 3, обработка МАР1: системные биты и контрольные биты 1 считываются из соответствующих устройств RAM согласно первоначальным адресам и передаются в блок параллельной обработки MAP для вычисления МАР1 (априорная информация МАР1 равна нулю при вычислении первой итерации), и внешняя информация, полученная при вычислении, записывается в устройство RAM априорной информации. Одновременно с началом выполнения декодирования перемежитель также начинает вычислять адрес перемежения и сохраняет его для того, чтобы заранее подготовить адреса перемежения для последующей обработки МАР2.

Шаг 4, обработка МАР2: контрольные биты 2, считываемые согласно первоначальным адресам, системные биты и априорная информация, считываемые согласно адресам перемежения (во время первой итерации априорная информация хвостовых битов, используемая МАР2, является нулевой, и чтение/запись данных, соответствующих хвостовым битам, не участвуют в перемежении), посылаются в блоки параллельной обработки MAP для вычисления МАР2, и априорная информация, полученная при вычислении, и результат жесткого решения записываются в устройство RAM априорной информации и устройство RAM результата декодирования соответственно. К этому времени одно итерационное декодирование турбокода заканчивается.

Шаг 5, согласно определенным условиям может оцениваться, выполнено ли условие завершения итерации, если да, то итерационное декодирование немедленно останавливается, а иначе возвращается к шагу 3, пока оно не достигает заранее заданного максимального числа итераций.

Фиг.3 - блок-схема способа декодирования согласно форме осуществления данного изобретения, и, как показано на фиг.3, во время многопутевого параллельного декодирования декодируемых кодовых блоков, во время каждой итерации, когда модуль декодирования каждого пути выполняет декодирование (включая вычисление МАР1 и вычисление МАР2), способ включает следующие основные шаги (от шага S302 до шага S306).

Шаг S302, для кодовых блоков, декодируемых в текущем пути, модуль декодирования получает все первые промежуточные переменные (то есть alpha) текущего пути посредством рекуррентного вычисления от начала к концу и в то же самое время получает все вторые промежуточные переменные (то есть beta) текущего пути посредством рекуррентного вычисления от конца к началу.

Первая промежуточная переменная может быть переменной alpha, а вторая промежуточная переменная - переменной beta, или наоборот, то есть первая промежуточная переменная - переменной beta, а вторая промежуточная переменная - переменной alpha. Предпочтительно в формах осуществления данного изобретения первая промежуточная переменная является переменной alpha, а вторая промежуточная переменная - переменной beta.

В предпочтительных формах осуществления данного изобретения, чтобы уменьшить пространство хранения, метрики ветвей (то есть gamma), необходимые при рекуррентном вычислении, могут вычисляться для первых промежуточных переменных и вторых промежуточных переменных соответственно. Для первых промежуточных переменных модуль декодирования получает все метрики ветвей текущего пути посредством рекуррентного вычисления от начала к концу и получает все первые промежуточные переменные (alpha) текущего пути посредством рекуррентного вычисления от начала к концу согласно всем полученным метрикам ветвей; и в то же самое время для вторых промежуточных переменных модуль декодирования получает все метрики ветвей текущего пути посредством рекуррентного вычисления от конца к началу и получает все вторые промежуточные переменные (beta) текущего пути посредством рекуррентного вычисления от конца к началу согласно всем метрикам ветвей, полученным в этот раз.

Первые промежуточные переменные и вторые промежуточные переменные вычисляют непосредственно, используя рекуррентные формулы вместо конвейерной аппаратной обработки. Кроме того, каждое рекуррентное вычисление первой промежуточной переменной и второй промежуточной переменной включает две части, то есть операцию суммирования для добавления gamma к первой промежуточной переменной или второй промежуточной переменной и операцию нормализации, и задержка логики комбинированной схемы также является большой. Поэтому при предпочтительной реализации данного изобретения каждое рекуррентное вычисление первой промежуточной переменной или второй промежуточной переменной выполняется за 2 цикла, сначала выполняется операция суммирования, затем выполняется обработка нормализации, то есть каждое рекуррентное вычисление первой промежуточной переменной или второй промежуточной переменной завершается в течение 2 тактов (clock, clk).

В предпочтительных формах осуществления данного изобретения вычисление с временным разделением выполняется для первых промежуточных переменных и вторых промежуточных переменных передней и задней половин декодируемых кодовых блоков одного и того же пути. Например, при рекуррентном вычислении первой, считая от начала к концу, из первых промежуточных переменных (таких как alpha) передней половины декодируемых кодовых блоков текущего пути, после выполнения операции суммирования, во время выполнения операции нормализации модуль декодирования выполняет операцию суммирования для рекуррентного вычисления первой, считая от начала к концу, из первых промежуточных переменных (alpha) задней половины декодируемых кодовых блоков текущего пути; модуль декодирования выполняет операцию суммирования для рекуррентного вычисления второй, считая от начала к концу, из первых промежуточных переменных (таких как alpha) передней половины и в то же самое время выполняет операцию нормализации для первой, считая от начала к концу, из первых промежуточных переменных (таких как alpha) задней половины, затем выполняет операцию суммирования для второй, считая от начала к концу, из первых промежуточных переменных (alpha) задней половины, и в то же время выполняет операцию нормализации для второй, считая от начала к концу, из первых промежуточных переменных (alpha) передней половины, и так далее, чтобы получить все первые промежуточные переменные (alpha) текущего пути посредством рекуррентного вычисления.

Точно так же, при рекуррентном вычислении первой, считая от конца к началу, из вторых промежуточных переменных (таких как beta) задней половины декодируемых кодовых блоков текущего пути, после выполнения операции суммирования, во время выполнения операции нормализации модуль декодирования выполняет операцию суммирования для рекуррентного вычисления первой, считая от конца к началу, из вторых промежуточных переменных (beta) передней половины декодируемых кодовых блоков текущего пути; модуль декодирования выполняет операцию суммирования для рекуррентного вычисления второй, считая от конца к началу, из вторых промежуточных переменных (beta) задней половины и в то же самое время выполняет операцию нормализации первой, считая от конца к началу, из вторых промежуточных переменных (beta) передней половины, затем выполняет операцию суммирования для второй, считая от конца к началу, из вторых промежуточных переменных (beta) передней половины, и в то же время выполняет операцию нормализации второй, считая от конца к началу, из вторых промежуточных переменных (beta) задней половины, и так далее, для получения всех вторых промежуточных переменных (beta) текущего пути посредством рекуррентного вычисления.

Первые промежуточные переменные и вторые промежуточные переменные вычисляют с использованием двух вышеописанных способов. После вычисления первой промежуточной переменной, соответствующей промежуточному биту передней половины, при вычислении первых промежуточных переменных, соответствующих задней половине передней половины, посредством рекуррентного вычисления, вторые промежуточные переменные, соответствующие этой части, уже вычислены, поэтому первые промежуточные переменные, вычисляемые для этой части, не должны сохраняться, после получения первой промежуточной переменной логарифмическое отношение правдоподобия (LLR), соответствующее этой позиции, вычисляется непосредственно согласно хранящейся второй промежуточной переменной, соответствующей этой позиции, и метрике ветви, соответствующей этой позиции. Аналогично, после вычисления второй промежуточной переменной, соответствующей промежуточному биту задней половины, при вычислении посредством рекуррентного вычисления вторых промежуточных переменных, соответствующих передней половине задней половины, первые промежуточные переменные, соответствующие этой части, вычислены, поэтому вторые промежуточные переменные, вычисленные для этой части, не должны сохраняться, после получения второй промежуточной переменной логарифмическое отношение правдоподобия (LLR), соответствующее этой позиции, вычисляется непосредственно согласно хранящейся первой промежуточной переменной, соответствующей этой позиции, и метрике ветви, соответствующей этой позиции. Поэтому, чтобы экономить пространство памяти, в предпочтительной реализации данного изобретения при выполнении вышеупомянутых операций модуль декодирования сохраняет в памяти первые промежуточные переменные (alpha), соответствующие передней половине кодовых блоков передней половины, и первые промежуточные переменные (alpha), соответствующие передней половине кодовых блоков задней половины; модуль декодирования сохраняет в памяти вторые промежуточные переменные (beta), соответствующие задней половине кодовых блоков задней половины, и вторые промежуточные переменные (beta), соответствующие задней половине кодовых блоков передней половины.

Шаг S304, модуль декодирования получает все логарифмические отношения правдоподобия (LLR) текущего пути согласно всем полученным первым промежуточным переменным и вторым промежуточным переменным, а также всем метрикам ветвей декодируемых кодовых блоков.

Например, в этой форме осуществления при рекуррентном вычислении первых промежуточных переменных (alpha), соответствующих задней половине кодовых блоков передней половины, и первых промежуточных переменных (alpha), соответствующих задней половине кодовых блоков задней половины, каждый раз при получении одной из первых промежуточных переменных (alpha) посредством рекуррентного вычисления модуль декодирования считывает вторую промежуточную переменную (beta), соответствующую этой позиции, и получает логарифмическое отношение правдоподобия, соответствующее этой позиции, согласно первой промежуточной переменной (alpha), второй промежуточной переменной (beta) и метрике ветви (gamma), соответствующий этой позиции; и при рекуррентном вычислении вторых промежуточных переменных (beta), соответствующих передней половине кодовых блоков задней половины, и вторых промежуточных переменных (beta), соответствующих передней половине кодовых блоков передней половины, каждый раз при получении одной второй промежуточной переменной (beta) посредством рекуррентного вычисления модуль декодирования считывает хранящуюся первую промежуточную переменную (alpha), соответствующую этой позиции, и получает логарифмическое отношение правдоподобия, соответствующее этой позиции, согласно второй промежуточной переменной (beta), первой промежуточной переменной (alpha) и метрике ветви (gamma), соответствующей этой позиции.

Например, логарифмическое отношение правдоподобия может быть вычислено согласно следующему способу:

для k=1: N

LLR(k)=max([alpha(k, 0+1)+gamma_1(k, 0+1)+beta(k+1, 4+1),

alpha(k, 1+1)+gamma_1(k, 1+1)+beta(k+1, 0+1), …

alpha(k, 2+1)+gamma_1(k, 2+1)+beta(k+1, 1+1), …

alpha(k, 3+1)+gamma_1(k, 3+1)+beta(k+1, 5+1), …

alpha(k, 4+1)+gamma_1(k, 4+1)+beta(k+1, 6+1), …

alpha(k, 5+1)+gamma_1(k, 5+1)+beta(k+1, 2+1), …

alpha(k, 6+1)+gamma_1(k, 6+1)+beta(k+1, 3+1), …

alpha(k, 7+1)+gamma_1(k, 7+1)+beta(k+1, 7+1), …])

max([alpha(k, 0+1)+gamma_1(k, 0+1)+beta(k+1, 00+1), …

alpha(k, 1+1)+gamma_1(k, 1+1)+beta(k+1, 4+1), …

alpha(k, 2+1)+gamma_1(k, 2+1)+beta(k+1, 5+1), …

alpha(k, 3+1)+gamma_1(k, 3+1)+beta(k+1,1+1), …

alpha(k, 4+1)+gamma_1(k, 4+1)+beta(k+1, 2+1), …

alpha(k, 5+1)+gamma_1(k, 5+1)+beta(k+1, 6+1), …

alpha(k, 6+1)+gamma_1(k, 6+1)+beta(k+1, 7+1), …

alpha(k, 7+1)+gamma_1(k, 7+1)+beta(k+1, 3+1), …]);

конец

Шаг S306, модуль декодирования получает априорную информацию, и результат декодирования выводится текущим путем согласно всем логарифмическим отношениям правдоподобия.

Например, после получения логарифмических отношений правдоподобия априорная информация, выводимая в это время, может быть получена согласно текущим отношениям LLR, полученным путем вычисления, и текущим входным системным битам и априорной информации.

В этой форме осуществления после получения результата декодирования каждого пути выполняется проверка при помощи циклического кода (CRC) согласно результату декодирования каждого пути и коду CRC декодируемых кодовых блоков, если проверка проходит успешно, то итерация будет остановлена и процесс декодирования завершится, а иначе выполняют следующий итерационный процесс, используя априорную информацию, выводимую каждым путем.

В соответствующей области техники одновременное итерационное вычисление первых промежуточных переменных (alpha) и вторых промежуточных переменных (beta) не выполняется, и поэтому проблема слишком длительной системной задержки не решается, кроме того, когда итерация выполняется корректно, итеративная операция не может быть остановлена в реальном времени, что еще более увеличивает время обработки системы. В то же время данная форма осуществления изобретения использует способ выполнения одновременного итерационного вычисления первых промежуточных переменных (alpha) и вторых промежуточных переменных (beta), что сокращает системную задержку до половины от исходной, и в то же самое время результат декодирования проверяется с использованием CRC, и если проверка проходит успешно, то последующий повторный итерационный процесс будет остановлен вовремя, что уменьшает затраты времени.

Если взять в качестве примера, что первая промежуточная переменная - alpha, а вторая промежуточная переменная - beta, то параллельный процесс декодирования турбокода в форме осуществления данного изобретения будет включать следующие основные шаги.

Шаг 1: несколько PU (блоков обработки, также называемых рядом параллельных путей, здесь один PU - это также одно скользящее окно) получают путем разделения согласно длине кодового блока, чтобы подготовиться к многопутевому параллельному декодированию. Каждый блок PU разделяется на две равные части, переднюю часть и заднюю часть, которые соответственно обозначаются как PU-f (передняя половина PU) и PU-b (задняя половина PU).

Шаг 2: устанавливают начальные значения alpha и beta для половин PU-f и PU-b (которые обозначаются как alpha0 и beta0, и далее alphal и betal получают посредством рекуррентного вычисления на основании alpha0 и beta0, затем alpha2 и beta2 получают посредством рекуррентного вычисления на основании alphal и betal, и так далее), и также задают соответствующее перекрытие (overlap) (длина окна перекрытия). Когда alpha итерируется от начала к концу, половина PU-f первого блока PU не имеет перекрытия; и когда beta итерируется от конца к началу, половина PU-b последнего блока PU не имеет перекрытия.

Шаг 3: переменные gamma половин PU-f и PU-b каждого блока PU вычисляют с использованием способа сегментации шага 1 и шага 2 соответственно согласно соответствующим системным битам,