Аналоговый интегратор

Иллюстрации

Показать всеИзобретение относится к электронной измерительной технике и аналитическому приборостроению. Технический результат заключается в снижении нелинейности и повышении точности при интегрировании в широком диапазоне величин входных сигналов. Аналоговый интегратор содержит источники входного и эталонного напряжений, переключатель, основной интегрирующий усилитель, дополнительный интегрирующий усилитель, основной компаратор, суммирующий хронометр и блок управления, дополнительный компаратор и конденсатор, при этом первый и второй входы дополнительного компаратора подключены соответственно к выходу основного интегрирующего усилителя и к источнику входного напряжения, первый вход основного компаратора подключен к точке с нулевым потенциалом, выходы основного и дополнительного компараторов соединены с входами блока управления, выходы последнего соединены с переключателем и суммирующим хронометром, а конденсатор включен между второй выходной клеммой источника эталонного напряжения и входом основного интегрирующего усилителя. 3 з.п. ф-лы, 2 табл., 2 ил.

Реферат

Изобретение относится к электронной измерительной технике и аналитическому приборостроению. Оно может использоваться для интегрирования медленно изменяющихся сигналов, в частности - при точном определении основного вещества методом кулонометрии при контролируемом потенциале.

Известен электронный аналоговый интегратор, содержащий источники входного и эталонного напряжений, переключатель, интегрирующий усилитель, суммирующий хронометр и блок управления переключателем, причем одноименные полюса источников соединены и через нормально замкнутые контакты переключателя подключены к входу интегрирующего усилителя, другой полюс источника эталонного напряжения соединен с нормально разомкнутым контактом переключателя (Авторское свидетельство СССР №374618, кл. G06G 7/18, Бюл. №15, 1973).

В этом интеграторе напряжение входного источника интегрируется циклически - сначала только сигнал входного источника напряжения, затем - алгебраическая сумма сигналов источников входного и эталонного напряжений. Циклическое включение и выключение источника эталонного напряжения осуществляется переключателем по командам блока управления. Величина интеграла оценивается по суммарной продолжительности включения источника эталонного напряжения, измеряемой суммирующим хронометром.

Недостатком данного интегратора является заметная погрешность при интегрировании в широком диапазоне величин входных напряжений. Данное обстоятельство определяется тем, что важнейший параметр интегратора - линейность интегрирования - заметно ухудшается (увеличивается нелинейность интегрирования) при уменьшении величины входного напряжения вследствие увеличения длительности циклов интегрирования.

Наиболее близким к предлагаемому изобретению является аналоговый интегратор, содержащий источники входного и эталонного напряжений, переключатель, основной интегрирующий усилитель, дополнительный интегрирующий усилитель, основной компаратор, суммирующий хронометр и блок управления, причем первые выходные клеммы одинаковой полярности источников входного и эталонного напряжений соединены и через нормально замкнутые контакты переключателя подключены к входу основного интегрирующего усилителя, вторые выходные клеммы источников входного и эталонного напряжений соединены соответственно с точкой с нулевым потенциалом и нормально разомкнутым контактом переключателя, вход дополнительного интегрирующего усилителя соединен с выходом основного интегрирующего усилителя, а выход дополнительного интегрирующего усилителя соединен с вторым входом основного компаратора (Авторское свидетельство СССР №723601, кл. G06G 7/18, Бюл. №11, 1980).

При работе данного интегратора напряжение входного источника также интегрируется циклически основным интегрирующим усилителем - сначала только сигнал входного источника напряжения, затем - алгебраическая сумма сигналов источников входного и эталонного напряжений. Выходное напряжение основного интегрирующего усилителя вторично интегрируется дополнительным интегрирующим усилителем. При этом включение и выключение источника эталонного напряжения осуществляется переключателем (электромагнитным реле) по команде компаратора, подключенного к выходу дополнительного интегрирующего усилителя. Команда компаратора подается в моменты равенства источника опорного напряжения и напряжения на выходе дополнительного интегрирующего усилителя. Величина интеграла оценивается по суммарной продолжительности включения источника эталонного напряжения, измеряемой суммирующим хронометром. Дополнительное интегрирования входного напряжения обеспечивает близкую к нулю величину среднего напряжения на выходе основного интегрирующего усилителя в каждом цикле, что заметно снижает методическую погрешность данного аналогового интегратора.

Недостатком интегратора является возрастание нелинейности интегрирования при малых входных напряжениях. Это связано с увеличением длительности циклов интегрирования для малых входных напряжений. Последнее, в свою очередь, обусловлено тем, что включение и выключение источника эталонного напряжения осуществляется при фиксированной величине выходного напряжения основного интегрирующего усилителя.

Задачей настоящего изобретения является снижение нелинейности и, тем самым, повышение точности при интегрировании в широком диапазоне величин входных сигналов.

Поставленная задача решается тем, что в аналоговом интеграторе, содержащем источники входного и эталонного напряжений, переключатель, основной интегрирующий усилитель, дополнительный интегрирующий усилитель, основной компаратор, суммирующий хронометр и блок управления, причем первые выходные клеммы одинаковой полярности источников входного и эталонного напряжений соединены и через нормально замкнутые контакты переключателя подключены к входу основного интегрирующего усилителя, вторые выходные клеммы источников входного и эталонного напряжений соединены соответственно с точкой с нулевым потенциалом и с нормально разомкнутым контактом переключателя, вход дополнительного интегрирующего усилителя соединен с выходом основного интегрирующего усилителя, а выход дополнительного интегрирующего усилителя соединен со вторым входом основного компаратора, согласно изобретению введены дополнительный компаратор и «запоминающий» электрический конденсатор, при этом первый и второй входы дополнительного компаратора подключены соответственно к выходу основного интегрирующего усилителя и к источнику входного напряжения, первый вход основного компаратора подключен к точке с нулевым потенциалом, выходы основного и дополнительного компараторов соединены с входами блока управления, выходы последнего соединены с переключателем и суммирующим хронометром, а электрический конденсатор включен между второй выходной клеммой источника эталонного напряжения и входом основного интегрирующего усилителя.

Переключатель аналогового интегратора может быть выполнен в виде электромагнитного реле с переключающимися магнитоуправляемыми контактами. В этом случае влияние перерыва в подаче сигналов в моменты срабатывания переключателя и «дребезга» контактов минимизируется «запоминающим» электрическим конденсатором.

Возможно также выполнение переключателя на основе интегрального ключа/интегральных ключей с комплементарными МОП-транзисторами (в этом случае «запоминающий» конденсатор может не применяться). Блок управления может быть выполнен на основе RS-триггера, управляемого сигналами обоих компараторов.

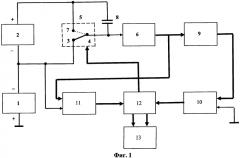

На фиг.1 изображена блок-схема предложенного аналогового интегратора. Для упрощения чертежа источники питания не показаны. Информационно-командные связи выделены утолщенными линиями.

На фиг.2 показаны временные диаграммы сигналов в отдельных узлах интегратора:

а) входное напряжение;

б) напряжение после переключателя (вход основного интегрирующего усилителя);

в) напряжение на выходе основного интегрирующего усилителя (пунктирной линией условно показано инвертированное входное напряжение);

г) напряжение на выходе дополнительного интегрирующего усилителя;

д) выходные импульсы обоих компараторов (в парах импульсов первый импульс - от вспомогательного компаратора, второй импульс - от основного компаратора);

е) импульсы включения суммирующего хронометра.

В состав аналогового интегратора входят источник входного напряжения 1 и источник эталонного напряжения 2. Напряжение источника эталонного напряжения 2 превышает максимальную величину напряжения источника входного напряжения 1. Для определенности выбраны: отрицательная полярность источника входного напряжения 1 и уменьшение величины напряжения этого источника во времени. Источники 1 и 2 включены последовательно и встречно - их первые выходные клеммы одинаковой полярности соединены и через нормально замкнутые контакты 3 и 4 переключателя 5 подключены к входу основного интегрирующего усилителя 6. Вторые выходные клеммы источников входного и эталонного напряжений 1 и 2 соединены соответственно с точкой с нулевым потенциалом и нормально разомкнутым контактом 7 переключателя 5.

Электрический конденсатор 8 включен между второй выходной клеммой источника эталонного напряжения 2 и входом основного интегрирующего усилителя 6.

Выход основного интегрирующего усилителя 6 соединен с входом дополнительного интегрирующего усилителя 9. Основной интегрирующий усилитель 6 и дополнительный интегрирующий усилитель 9 однотипны и выполнены по известной схеме интегрирующего операционного усилителя с отрицательной емкостной обратной связью. Выход дополнительного интегрирующего усилителя 9 соединен со вторым входом основного компаратора 10, первый вход которого подключен к точке с нулевым потенциалом. Первый вход дополнительного компаратора 11 подключен к выходу основного интегрирующего усилителя 6, а второй вход соединен с источником входного напряжения 1.

Компараторы 10 и 11 выполнены однотипно на основе операционного усилителя без обратной связи. Выходные сигналы основного компаратора 10 и дополнительного компаратора 11 в виде коротких импульсов подводятся к блоку управления 12, который построен на основе RS-триггера и управляет включением/выключением переключателя 5 и суммирующего хронометра 13.

Работа аналогового интегратора происходит следующим образом. В начальный момент переключатель 5 находится в положении, указанном на фиг.1. Напряжение отрицательной полярности от источника входного напряжения 1 (фиг.2-а) поступает через контакты 3 и 4 переключателя 5 на вход основного интегрирующего усилителя 6 (фиг.2-б). На выходе основного интегрирующего усилителя 6 напряжение положительной полярности линейно увеличивается во времени (фиг.2-в). Одновременно увеличивается напряжение отрицательной полярности на выходе дополнительного интегрирующего усилителя 9 (фиг.2-г).

Когда модуль величины напряжения на выходе основного интегрирующего усилителя 6 сравняется с величиной напряжения источника входного напряжения 1 в данный момент (фиг.2-в), то дополнительный компаратор 11 вырабатывает импульс (первый в паре импульсов на фиг.2-д). Этот импульс переводит триггер в блоке управления 12 в другое состояние, выходной сигнал триггера включает суммирующий хронометр 13 (фиг.2-е) и переводит переключатель 5 в положение, при котором контакты 3 и 4 разомкнуты, а контакты 7 и 4 замкнуты. Теперь на вход основного интегрирующего усилителя 6 поступает уже алгебраическая сумма напряжений источника входного напряжения 1 и источника эталонного напряжения 2 (фиг.2-б). Выходные напряжения основного и дополнительного интегрирующих усилителей 6 и 9 начинают уменьшаться (фиг.2-в, г).

В тот момент, когда напряжение на выходе дополнительного интегрирующего усилителя 9 уменьшится до нуля, основной компаратор 10 вырабатывает импульс (второй в паре импульсов на фиг.2-д), который возвращает триггер в блоке управления 12 в исходное состояние. При этом выходной сигнал триггера выключает суммирующий хронометр 13 (фиг.2-е) и переводит переключатель 5 в положение, при котором контакты 3 и 4 замкнуты, а контакты 7 и 4 разомкнуты. Теперь на вход основного интегрирующего усилителя 6 поступает только напряжение от источника входного напряжения 1 (фиг.2-б), на выходе основного интегрирующего усилителя 6 напряжение положительной полярности начинает линейно увеличивается (фиг.2-в), и все описанные процессы циклически повторяются (фиг.2-в).

Вследствие того что включением источника эталонного напряжения 2 управляет дополнительный компаратор 11, следящий за величиной входного напряжения, длительности отдельных циклов практически не зависят от величины входного напряжения. Выключением источника эталонного напряжения 2 управляет дополнительный интегрирующий усилитель 9, в результате чего среднее значение выходного напряжения основного интегрирующего усилителя 6 близко к нулю и общая методическая погрешность интегрирования мала (аналогично прототипу).

Учитывая, что нелинейность данного аналогового интегратора предполагается очень малой, проверка параметров интегратора проведена методом компьютерного моделирования применительно к особенностям использования интегратора в составе кулонометрической установки для определения основного вещества в растворах методом кулонометрии при контролируемом потенциале.

Для проверки параметров интегратора в составе кулонометрической установки были использованы два типа переключателей:

первый - выполнен в виде электромагнитного реле с переключающимися магнитоуправляемыми контактами типа МКУ с временем переключения 1 мс;

второй - выполнен на базе двух интегральных замыкающих ключей с комплементарными МОП-транзисторами (тип ключа К590КН25) с временем переключения около 100 нс (ключи соединены по схеме переключателя).

В первом случае выбраны следующие параметры интегратора:

- входное напряжение уменьшается во времени по экспоненциальному закону с постоянной времени 50 с (типичная зависимость величины напряжения от времени при определении основного вещества методом кулонометрии при контролируемом потенциале);

- диапазон входных напряжений выбран с определенным запасом и с учетом параметров примененных операционных усилителей - от 10 В до 0,3 мВ (33000:1 или 15 двоичных разрядов);

- конденсаторы емкостной обратной связи основного и дополнительного интегрирующих усилителей (тип К72П-6) имеют диэлектрик из фторопласта и собственную постоянную времени в конце срока службы не менее 1000 с;

- постоянные времени емкостной обратной связи основного и дополнительного интегрирующих усилителей одинаковы и равны 1 с;

- емкость установленного «запоминающего» конденсатора 10 мкФ;

- напряжение источника эталонного напряжения Uэт=18,2 В (два прецизионных термокомпенсированных стабилитрона типа КС191Р).

Для второго случая выбраны следующие параметры интегратора:

- напряжение источника эталонного напряжения снижено до Uэт=15 В (обусловлено параметрами ключей);

- «запоминающий» конденсатор в этом случае не устанавливается;

- остальные данные интегратора полностью совпадают с данными первого случая 1.

Компьютерное моделирование осуществлялось по следующему алгоритму:

- выбранный диапазон входного напряжения разделялся на 15 двоичных частей (поддиапазонов), величины начального и конечного напряжений которых относятся как 2:1 (примеры: 10 В - 5 В; 5 В - 2,5 В; 2,5 В - 1,25 В и т.д.);

- для средней величины напряжений каждого поддиапазона вычислялись частные нелинейности (относительные величины отклонения от линейной зависимости напряжения от времени на выходе основного интегрирующего усилителя 6);

- полученные величины частных нелинейностей скорректировались (уменьшались) с учетом величины интеграла, соответствующего каждому двоичному поддиапазону входного напряжения. Можно показать, что в нашем случае корректирующие коэффициенты изменяются по двоичному закону и равны: 1/2 (участок 10 В - 5 В), 1/4 (участок 5 В - 2,5 В), 1/8 (участок 2,5 В - 1,25 В) и т.д.;

- общая нелинейность интегрирования оценивалась как сумма частных нелинейностей всех выбранных двоичных поддиапазонов.

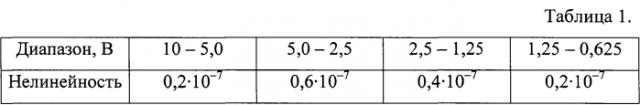

Итоги компьютерного моделирования. Первый Интегратор (случай: общая погрешность нелинейности при интегрировании напряжения, уменьшающегося во времени по экспоненциальному закону в диапазоне напряжений от 10 В до 0,3 мВ, не превышает 2·10-7). В качестве примера в таблице 1 приведены данные о величинах корректированных частных нелинейностях в верхних поддиапазонах входных напряжений.

Погрешность нелинейности из-за перерывов интегрирования вследствие конечной величины времени переключения электромагнитного реле с магнитоуправляемыми контактами оценена как 5,3·10-7. Второй Интегратор (случай: общая погрешность нелинейности при интегрировании напряжения, уменьшающегося во времени по экспоненциальному закону в диапазоне напряжений от 10 В до 0,3 мВ, не превышает 1,6·10-7).

Погрешность нелинейности вследствие перерывов в процессе интегрирования из-за конечной величины времени переключения интегральных ключей оценена как 0,5·10-7.

Таким образом, суммарные погрешности нелинейности предложенного интегратора в итоге не превышают:

для интегратора с переключателем в виде электромагнитного реле с магнитоуправляемыми контактами - 6·10-7 (6·10-5%), для интегратора с переключателем на базе интегральных ключей с комплементарными МОП-транзисторами - 2·10-7 (2·10-5%).

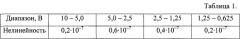

Для сравнения нелинейности предложенного интегратора с прототипом проведено исследование интегратора-прототипа таким же методом компьютерного моделирования с использованием данных интегратора по первому случаю. Напряжение источника опорного напряжения компаратора в прототипе выбрано равным 7 В, что позволило сделать практически одинаковыми условия работы предложенного интегратора и интегратора-прототипа в верхнем участке входных напряжений. В качестве примера в таблице 2 приведены данные о величинах корректированных частных нелинейностях интегратора-прототипа в верхних поддиапазонах входных напряжений, уменьшающихся во времени по экспоненциальному закону (диапазон от 10 В до 0,3 мВ).

Данные таблицы 2 свидетельствуют заметном увеличении нелинейности интегратора-прототипа при уменьшении входных напряжений начиная уже с 5,0 В. Общая погрешность нелинейности прототипа в диапазоне от 10 В до 0,3 мВ оценена как 5·10-3 (0,5%), что связано с резким увеличением нелинейности при малых входных напряжениях.

Оценка нелинейности прототипа, связанной с конечной величиной времени переключения электромагнитного реле с магнитоуправляемыми контактами, показала, что вследствие отсутствия в прототипе «запоминающего» конденсатора указанная нелинейность составляет не менее 5·10-4, то есть намного больше, чем у предложенного интегратора. Суммарная погрешность нелинейности прототипа оценивается как 5·10-3 (0,5%).

Таким образом, проверки показали, что предложенный аналоговый интегратор по сравнению с прототипом характеризуется существенно более низкой (не менее трех порядков величины) нелинейностью. Малое значение нелинейности предложенного интегратора связано, главным образом, с введением в состав интегратора дополнительного управляемого входным напряжением компаратора, что и обеспечило, в отличие от прототипа, слабую зависимость длительности отдельных циклов интегрирования от величины входного напряжения. Дополнительное повышение точности интегрирования достигается также применением переключателя на основе интегральных ключей с комплементарными МОП-транзисторами.

1. Аналоговый интегратор, содержащий источники входного и эталонного напряжений, переключатель, основной интегрирующий усилитель, дополнительный интегрирующий усилитель, основной компаратор, суммирующий хронометр и блок управления, причем первые выходные клеммы одинаковой полярности соединены и через нормально замкнутые контакты переключателя подключены к входу основного интегрирующего усилителя, вторые выходные клеммы источников входного и эталонного напряжений соединены соответственно с точкой с нулевым потенциалом и нормально разомкнутым контактом переключателя, вход дополнительного интегрирующего усилителя соединен с выходом основного интегрирующего усилителя, а выход дополнительного интегрирующего усилителя соединен с вторым входом основного компаратора, отличающийся тем, что в него введены дополнительный компаратор и электрический конденсатор, при этом первый и второй входы дополнительного компаратора подключены соответственно к выходу основного интегрирующего усилителя и к источнику входного напряжения, первый вход основного компаратора подключен к точке с нулевым потенциалом, выходы основного и дополнительного компараторов соединены с входами блока управления, выходы последнего соединены с переключателем и суммирующим хронометром, а электрический конденсатор включен между второй выходной клеммой источника эталонного напряжения и входом основного интегрирующего усилителя.

2. Аналоговый интегратор по п. 1, отличающий тем, что переключатель выполнен в виде электромагнитного реле с переключающимися контактами на герконах.

3. Аналоговый интегратор по п. 1, отличающий тем, что переключатель выполнен в виде интегрального ключа/интегральных ключей на базе комплементарных МОП-транзисторов.

4. Аналоговый интегратор по п. 1, отличающий тем, что блок управления построен на основе RS-триггера.