Схемы многопланового видеокодирования

Иллюстрации

Показать всеИзобретение относится к области кодирования нескольких видеопоследовательностей с различных планов сцены. Технический результат - обеспечение улучшения эффективности кодирования. Реализуемый компьютером способ межпланового кодирования содержит этапы, на которых в видеокодере: определяют режим межпланового кодирования для по меньшей мере части кадра изображения; конкретизируют соответствующее значение для индикатора режима межпланового кодирования; и встраивают индикатор режима в двоичный поток, при этом двоичный поток включает в себя кодированный вектор, связанный с частью кадра изображения; причем первое значение индикатора режима соответствует первому режиму межпланового кодирования, в котором кодированный вектор движения включает в себя составляющие во многих измерениях, а второе значение индикатора режима соответствует второму режиму межпланового кодирования, в котором составляющие кодированного вектора движения включают в себя составляющие только в одном измерении. 5 н. и 25 з.п. ф-лы, 9 ил.

Реферат

Уровень техники

Многоплановое видеокодирование (МВК) (MVC) представляет собой расширение стандарта видеокодирования H.264/AVC. Оно позволяет кодировать несколько видеопоследовательностей с различных планов сцены в единый двоичной поток, в том числе основной план и дополнительные неосновные планы, которые могут кодироваться независимо от основного плана. Существуют также возможные соотношения зависимости в кодировании между неосновными планами. После кодирования каждый план может быть представлен как отдельный двоичный поток, либо эти отдельные двоичные потоки планов могут сливаться вместе.

Важным методом сжатия в МВК является межплановое предсказание. Различные видеопоследовательности, полученные в различных положениях камер относительно сцены, зачастую проявляют сильные корреляции между планами. Таким образом, при кодировании кадра изображения или картинки в конкрегном плане, картинка в основном плане и(или) в других дополнительных планах могут использоваться в качестве межплановых опорных картинок для улучшения эффективности кодирования. Далее, кодер может выбирать между использованием межплановых опорных картинок или использованием временных опорных картинок из видеопоследовательности одного и того же плана. При оценке движения сначала предсказывается двумерный (2D) вектор движения (ВД) (MV) в форме MV(xp,yp), а затем ищут другие векторы движения в конкретном диапазоне, чтобы выявить наилучший MV(x,y), который минимизирует искажение между текущим блоком и опорным блоком. Разность между MV(x,y) и MV(xp,yp) кодируется затем как разностный сигнал.

В последовательностях множества планов проекция одного и того же объекта на различные планы может быть связана с соответствующими положениями камер. Например, широко используются методы параллельных камер, потому что они хорошо моделируют человеческую систему стереоскопического зрения. В установках параллельных камер эти камеры могут так выравниваться, что их положения отличаются практически только в одном измерении (к примеру, по оси x). Таким образом, положения двух проекций одного и того же пиксела трехмерного пространства на два соответствующих плана могут отличаться только в одном измерении (к примеру, в направлении x).

Краткое описание чертежей

Описанный здесь материал иллюстрируется посредством примеров, а не ограничений, в сопровождающих чертежах. Для простоты и ясности иллюстраций показанные на чертежах элементы необязательно изображены в масштабе. Например, размеры некоторых элементов для ясности могут быть увеличены по отношению к другим элементам. Далее, когда это считается уместным, ссылочные позиции повторены на чертежах, чтобы указывать соответствующие или аналогичные элементы.

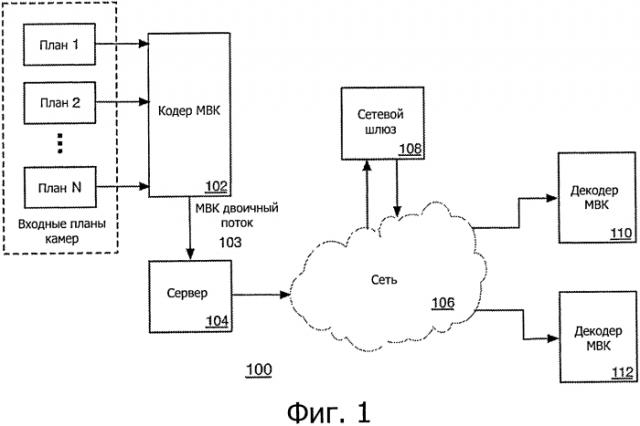

Фиг.1 является иллюстративной схемой примера системы многопланового видеокодирования.

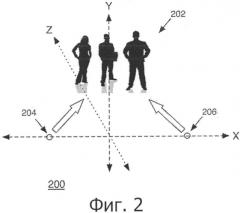

Фиг.2 иллюстрирует пример многопланового сценария.

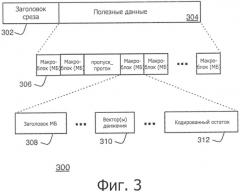

Фиг.3 иллюстрирует часть двоичного потока.

Фиг.4 и 5 иллюстрируют синтаксические схемы.

Фиг.6 и 7 являются блок-схемами алгоритмов для примера процессов по реализации схем многопланового кодирования.

Фиг.8 является иллюстративной схемой примерной системы.

Фиг.9 является иллюстративной схемой примерного устройства.

При этом все чертежи сделаны и соответствии с по меньшей мере некоторыми реализациями настоящего изобретения.

Подробное описание

Теперь со ссылками на сопровождающие чертежи будут описаны один или несколько вариантов осуществления или реализации. Хотя обсуждаются конкретные конфигурации и конструкции, следует понимать, что это делается только в иллюстративных целях. Специалисты поймут, что и иные конфигурации и конструкции могут применяться без отхода от сущности и объема данного изобретения. Для специалистов будет очевидно, что описанные здесь методы и(или) конструкции могут также применяться во множестве других систем и приложений, иных, нежели те, что описаны здесь.

Хотя нижеследующее описание излагает реализации, которые могут проявляться в таких, например, архитектурах, как архитектуры система на кристалле (SoC), реализация описанных здесь методов и(или) конструкций не ограничена конкретными архитектурами и(или) вычислительными системами и может воплощаться в архитектуре и(или) вычислительной системе для аналогичных целей. Например, описанные здесь методы и(или) конструкции могут реализовывать различные архитектуры, применяющие, к примеру, множество кристаллов и(или) корпусов интегральных схем (ИС) (IC), и(или) различные вычислительные устройства и(или) устройства бытовой электроники (СЕ), такие как телеприставки, смартфоны и т.п. Далее, хотя нижеследующее описание может излагать многочисленные конкретные подробности, такие как логические реализации, типы и взаимозависимости системных компонентов, предпочтения логического разделения-объединения и т.п., заявленный предмет может осуществляться и без таких конкретных подробностей. В иных случаях некоторые материалы, такие, например, как управляющие структуры и полные последовательности программных команд могут не показываться подробно, чтобы не затемнять описанного здесь материала.

Описанный здесь материал может быть воплощен аппаратно, программно, программно-аппаратно или в любой их комбинации. Описанный здесь материал может быть также реализован как команды, хранящиеся на машиночитаемом носителе, которые могут считываться и исполняться одним или несколькими процессорами. Машиночитаемый носитель может включать в себя среду и(или) механизм для хранения или передачи информации в виде, считываемом машиной (к примеру, вычислительным устройством). Например, машиночитаемый носитель может включать в себя постоянное запоминающее устройство (ПЗУ) (ROM), оперативно запоминающее устройство (ОЗУ) (RAM), носитель в виду магнитного диска, оптический носитель, устройства на флэш-памяти, электрические, оптические, акустические или другие виды распространяемых сигналов (к примеру, несущие частоты, инфракрасные сигналы, цифровые сигналы и т.п.) и проч.

Ссылки в данном описании на «одну реализацию», «реализацию», «примерную реализацию» и т.п. указывают, что описанная реализация может включать в себя конкретные признак, структуру или характеристику, но каждая реализация необязательно может включать в себя эти конкретные признак, структуру или характеристику. Кроме того, такие выражения необязательно относятся к одной и той же реализации. Далее, когда конкретные признак, структура или характеристика описаны в связи с реализацией, предполагается, что они находятся в сфере знаний специалиста, чтобы осуществлять такие признак, структуру или характеристику в связи с другими реализациями, описаны они или нет здесь явным образом.

Фиг.1 иллюстрирует примерную систему 100 многопланового видеокодирования (MBK) в соответствии с настоящим изобретением. В различных реализациях система 100 МВК может включать в себя кодер 102 МВК, сервер 104, сеть 106, сетевой шлюз 108 и декодеры 110 и 112 МВК. В разных реализациях кодер 102 МВК может принимать кадры или картинки видеоизображений, соответствующие множеству планов входных камер трехмерной (3D) сцены и может быть выполнен с возможностью предпринимать видеосжатие и(или) реализовывать видеокодеки согласно одному или нескольким расширенным стандартам на видеокодеки, например, таким как стандарт H.264/AVC (см. ISO/IEC JTCI и ITU-T, H.264/AVC - «Усовершенствованное видеокодирование для типовых аудиовизуальных услуг», ITU-T Rec. H.264 и ISO/IEC 14496-10 (MPEG-4 часть 10), версия 3, 2005), и их расширениям, в том числе расширение многопланового видеокодирования к стандарту AVC (см. ISO/IEC 14496-10:2008 Изменение I (2008) (здесь и далее: «стандарт MBK»). Хотя система 100 и(или) другие системы, схемы и процессы могут описываться здесь в контексте этого стандарта МВК для целей иллюстрации и пояснения, настоящее изобретение не ограничено какими-либо конкретными стандартами или описаниями видеокодирования.

В различных реализациях кодер 102 МВК может воплощать основанный на блоках подход гибридного видеокодирования, в котором видеокадры подразделяются на срезы, которые в свою очередь подразделяются на макроблоки (МБ) для кодирования. Каждый МБ может соответствовать площади прямоугольного изображения размером 16×16 яркостных отсчетов и, в случае видео в формате отсчетов цветности 4:2:0, двум площадям отсчетов компонентов цветности размером 8×8. Отсчеты МБ могут предсказываться либо в пространстве, либо по времени, и результирующий разностный сигнал предсказания может быть представлен с помощью кодирования с преобразованием. В различных реализациях кодер 102 МВК может определять, какой тип кодирования выполнять на помакроблочной основе. Как используется здесь, «блок» может относиться к МБ или подразделению под-макроблоков видеоданных.

Как будет подробнее пояснено далее, кодер 102 МВК может использовать методы в соответствии с настоящим изобретением для генерирования кодированных многоплановых видеоданных, представляющих различные планы сцены. Кодер 102 МВК может выдавать кодированные многоплановые видеоданные в виде кодированного МВК двоичного потока 103, включающего в себя основной план и дополнительные неосновные планы, кодирование которых может зависеть от основного плана. В различных реализациях каждый план может быть представлен отдельным МВК двоичным потоком, либо двоичные потоки планов могут сливаться вместе для образования единого двоичного потока, такого как МВК двоичный поток 103.

Сервер 104 может передавать двоичный поток 103 по сети 106 различным клиентам, таким как декодеры 110 и 112 МВК, имеющие различные функциональные возможности видеодекодирования, В различных реализациях двоичный поток 103 может передаваться через один или несколько сетевых шлюзов, таких как сетевой шлюз 108. В различных реализациях сетевой шлюз 108 может быть знающим о сети сетевым элементом, который может обрабатывать входящие видеопакеты или двоичные подпотоки двоичного потока 103 перед тем, как предоставить измененную форму двоичного потока 103 декодерам 110 и 112 MBK. В некоторых реализациях сетевой шлюз 108 может обрабатывать двоичный поток 103, чтобы подавать только двоичный поток основного плана в систему и(или) устройства (не показаны на Фиг.1), которые не имеют возможности осуществлять методы МВК. Для систем и(или) устройств, которые способны осуществлять методы МВК, таких как декодеры 110 и 112 МВК, двоичный поток основного плана и один или несколько двоичных потоков неосновных планов, являющихся составляющими двоичного потока 103, могут использоваться для осуществления описанных здесь методов МВК.

В декодерах 110 и 112 МВК кодированные видеоданные могут извлекаться из двоичного потока 103, а затем декодироваться и визуализироваться различным образом в зависимости от прикладных сценариев и функциональных возможностей систем и(или) устройств, включающих в себя эти декодеры 110 и 112 МВК. Например, из числа неограничивающих примеров, декодер 110 МВК может быть частью системы стереоскопического отображения (не показано на Фиг.1), тогда как декодер 112 МВК может быть частью видеосистемы, не ограниченной планом (также не показано на Фиг.1). В различных реализациях декодеры 110 и 112 МВК могут осуществлять разные методы МВК, такие как компенсация межпланового движения, используя информацию и(или) данные, предоставляемые двоичным потоком 103. Например, макроблоки в срезе картинки неосновного плана могут предсказываться на основе кодированного вектора движения, предоставленного в МВК двоичном потоке 103, который указывает или ссылается на МБ в картинке основного плана.

В различных вариантах осуществления видео- и(или) медиапроцессор может воплощать кодер 102 МВК или декодеры 110 и(или) 112 МВК в системе 100. В общем, различные составляющие системы 100 могут быть воплощены программно, программно-аппаратно и(или) аппаратно и(или) в любой их комбинации. Например, различные составляющие системы 100 могут, по меньшей мере частично, выполняться за счет аппаратного обеспечения вычислительной системы на кристалле (SoC), как встречается в устройстве или системе бытовой электроники (СЕ).

Далее, хотя Фиг.1 показывает сервер 104, коммуникативно связывающий кодер 102 МВК с сетью 106, подобный (-е) сервер(ы), не показанный (-е) на Фиг.1 в интересах ясности, может (могут) аналогично коммуникативно связывать декодеры 110 и 112 МВК с сетью 106. Помимо этого, хотя Фиг.1 показывает декодеры 110 и 112 МВК как принимающие двоичный поток 103 из сети 106, настоящее изобретение не ограничивается какими-либо конкретными схемами, методами и(или) системами для обеспечения связи двоичного потока 103 с декодерами 110 и 112 MB К. Таким образом, в различных реализациях декодеры 110 и 112 МВК могут принимать двоичный поток 103 как данные, хранящиеся на машиночитаемом носителе, таком, например, как цифровой видеодиск с записями высокого разрешения или высокой плотности (HD-DVD). Кроме того, в различных реализациях декодер МВК в соответствии с настоящим изобретением может быть реализован в устройстве бытовой электроники, таком как телеприставка, кабельный телевизор или тому подобное, и может принимать МВК двоичный поток в соответствии с настоящим изобретением по кабельной сети, спутниковой сети и т.п.

В различных реализациях настоящее изобретение не ограничивается конкретной природой различных составляющих системы 100, таких как сервер 104, сеть 106 и(или) сетевой шлюз 108. Например, сервер 104 может включать в себя любой веб-сервер или аналогичную компьютерную программу, исполняемую на любой вычислительной системе, которая позволяет кодеру 102 МВК посылать двоичный поток 103 по сети 106. Аналогично, сеть 106 может быть любого типа и(или) комбинацией проводных и(или) беспроводных сетей или сетевых систем, которые способны передавать двоичный поток 103 между кодером 102 МВК и(или) сервером 104 и декодерами 110 и 112 МВК.

Межплановое предсказание

Как отмечено ранее, при кодировании картинки в конкретном плане, таком как неосновной план, кодер 102 МВК может использовать картинки в основном плане и(или) в других неосновных планах в качестве межплановых опорных картинок для улучшения эффективности кодирования. Далее, при выполнении оценки движения для конкретной кадровой части (к примеру, для МБ) кодер 102 МВК может выбирать между использованием методов межпланового предсказания и временного предсказания. При выполнении методов межпланового предсказания кодер 102 МВК может использовать межплановые картинки в качестве опорных картинок для целей оценки движения.

В соответствии с настоящим изобретением и как будет подробнее поясняться ниже, кодер 102 МВК может определять режим межпланового кодирования, применяемый при выполнении межпланового предсказания и может выдавать в двоичный поток 103 соответствующий режимный индикатор, бит или флаг, указывающий на режим межпланового кодирования, связанный с по меньшей мере частью изображения или многоплановой видеопоследовательностью. В различных реализациях кодер 102 МВК может помещать индикатор режима в различные местоположения в двоичном потоке 103, в том числе в синтаксических компонентах заголовка картинки и(или) среза либо в синтаксических компонентах МБ в двоичном потоке 103.

В соответствии с настоящим изобретением режим межпланового кодирования, определенный кодером 102 MBK, может конкретизироваться как имеющий одно или два состояния: первый режим межпланового кодирования, когда двумерные (2D) межплановые ВД кодируются так, что для каждого ВД обе составляющих ВД кодируются и показываются в двоичном потоке, и второй режим межпланового кодирования, когда одномерные (ID) межплановые ВД кодируются так, что для каждого ВД только одна составляющая ВД кодируется и показывается в двоичном потоке. Как используется здесь, межплановый ВД задает направление из МБ (или подразделения макроблока и(или) под-макроблока) в видеопоследовательности одного плана на МБ (или подразделения макроблока и(или) под-макроблока) в видеопоследовательности другого плана. Например, в первом режиме межпланового кодирования кодированный межплановый МБ мотет включать в себя две составляющих ВД (к примеру, x и y), которые определяют смещение в двух направлениях, тогда как во втором режиме межпланового кодирования кодированный межплановый ВД может включать в себя только одну составляющую ВД (к примеру, x или y), которая определяет смещение только в одном направлении, тем самым снижая число двоичных разрядов, появляющихся в соответствующем двоичном потоке.

Например, Фиг.2 иллюстрирует пример многопланового сценария 200, в котором видеопоследовательности трехмерной сцены 202 снимаются с двух разных точек 204 и 206 наблюдения, которые смещены одна от другой вдоль одного направления, произвольно помеченного как ось «x» в данном примере. В сценарии 200 устройства получения изображений, такие как камеры (не показано), снимающие видео из точек 204 и 206 наблюдения, могут находиться в параллельной установке, когда эти камеры выровнены вдоль одного направления так, что из положения существенно отличаются только в одном измерении (к примеру, по оси x) и являются практически одинаковыми в других двух измерениях. В результате положения двух проекций трехмерного пространственного пиксела в сцене 202 на два плана 204 и 206 могут существенно отличаться только в одном измерении. Поэтому межплановый ВД, задающий направление из МБ в одном плане в МБ в другом плане, может иметь только одну существенную составляющую (к примеру, составляющую x), тогда как другая составляющая (к примеру, составляющая y) имеет нулевое или практически нулевое значение. Таким образом, при формировании двоичного потока в сценариях с нулевыми или практически нулевыми значениями составляющих ВД, таких как сценарий 200, кодер 102 МВК может принять решение не кодировать нулевые или практически нулевые составляющие ВБ и, следовательно, только составляющая ВД, подлежащая кодированию и помещению в двоичный поток, может быть ненулевой составляющей ВД.

МВК двоичный поток

В различных реализациях схема межпланового видеокодирования в соответствии с настоящим изобретением может непосредственно указывать в двоичном видеопотоке, кодируется ли и позывается ли в двоичном потоке составляющая ВД. Например, двоичный поток может включать в себя индикатор, флаг или двоичный разряд (b) межпланового режима, чтобы установить, что в первом режиме межпланового видеокодирования (к примеру, со значением b=0) обе составляющих x и y ВД кодируются и показываются в двоичном потоке, либо что во втором режиме межпланового видеокодирования (к примеру, со значением b=1) только составляющие x ВД кодируются и показываются в двоичном потоке и что никакие составляющие y ВД не кодируются, а потому и не показываются в этом двоичном потоке. Соответственно, синтаксис двоичного потока будет включать в себя кодированные x и кодированные у составляющие ВД (к примеру, (MVx, MVy)), когда двоичный разряд режима имеет нулевое значение, или может включать в себя только кодированные x составляющие ВД (к примеру, (MVx, 0)), когда двоичный разряд режима имеет единичное значение. Однако настоящее изобретение не ограничивается конкретными логическими значениями индикатора межпланового режима, а, значит, в других реализациях нулевое значение двоичного разряда режима может использоваться для указания, что кодируются только составляющие MVx, тогда как значение b=1 двоичного разряда режима может использоваться для указания того, что кодируются обе составляющих MVx и MVy, и т.д.

В различных реализациях индикатор межпланового кодирования может применяться на разных уровнях кодирования, в том числе - но без ограничения ими - к уровню МБ и(или) к более высоким уровням, таким как уровень срезов или уровень картинок. При применении к уровню кодирования, который указывает множество ВД, двоичный разряд режима межпланового кодирования может быть ведущим двоичным разрядом в заголовке уровня кодирования, тогда как кодированные составляющие ВД могут быть включены в синтаксис МБ.

В различных вариантах осуществления кодер 102 МВК может воплощать уровень сетевой абстракции (УСА) (NAL), который генерирует двоичный поток 103 путем форматирования кодированных видеоданных для включения в двоичный поток 103 и путем обеспечения в двоичном потоке 103 информации заголовка, которая позволяет воплотить схемы многопланового кодирования декодерами 110 и 112 МВК. В соответствии с настоящим изобретением, кодер 102 МВК может генерировать двоичный поток 103 как последовательности секций или пакетов УСА, когда каждая секция УСА включает в себя полезные многобайтовые видеоданные, в том числе составляющие векторов движения. Единственный кодированный кадр изображения, или секция доступа, может соответствовать набору следующих один за другим секций УСА, а кодированная видеопоследовательность, такая как кодированная видеопоследовательность основного плана или неосновного плана, может соответствовать набору следующих один за другим секций доступа.

В различных реализациях секции УСА в двоичном потоке 103 могут включать в себя заголовки срезов и(или) картинок, имеющие набор параметров последовательности и картинки и(или) дополнительные улучшающие информационные (ДУЙ) сообщения. Например, в стандарте МВК, МВК кодированная секция УСА среза включает в себя четырехразрядный заголовок, за которым следует секция полезных данных УСА. Синтаксические элементы в заголовке среза или картинки могут включать в себя идентификатор приоритета, идентификатор плана и т.д. Например, Фиг.3 иллюстрирует примерную часть 300 двоичного потока, включающую в себя заголовок 302 среза и полезные данные 304, а полезные данные 304 включают в себя, например, кодированные элементы 306 синтаксиса МБ. Каждый кодированный элемент 306 синтаксиса МБ может включать в себя заголовок 308 МБ, кодированные значения составляющих для одного или нескольких кодированных векторов 310 движения и кодированные разностные данные 312.

В различных реализациях в соответствии с настоящим изобретением заголовки срезов и(или) картинок в двоичном потоке 103 могут включать в себя индикаторы режима межпланового кодирования, как описано здесь. В различных реализациях двоичный поток 103 может включать в себя индикаторы режима межпланового кодирования на макроблоковом уровне или слое. В таких реализациях индикатор режима межпланового кодирования может быть ведущим двоичным разрядом, предусмотренным в заголовке макроблока. Например, Фиг.4 иллюстрирует примерную схему 400 синтаксиса макроблокового уровня в соответствии с различными реализациями настоящего изобретения. Схема 400 включает в себя синтаксис 402, где нулевое значение для ведущего двоичного разряда 404 (к примеру, соответствующее первому режиму межпланового кодирования) указывает, что кодированы обе составляющих MVx 406 и MVy 408. Схема 400 также включает в себя синтаксис 410 МБ, где единичное значение для ведущего двоичного разряда 404 (к примеру, соответствующее второму режиму межпланового кодирования) указывает, что кодированы только составляющие 412 MVx. В некоторых реализациях множество пар 414 из составляющих MVx и MVy (к примеру, более двух пар составляющих MVx и MVy) могут следовать за ведущим двоичным разрядом 404 в синтаксисе 402 и(или) множество составляющих 416 MVx (к примеру, более одной составляющей MVx) могут следовать за ведущим двоичным разрядом 404 в синтаксисе 410.

В различных реализациях двоичный поток 103 может включать в себя индикаторы режима межпланового кодирования на слое и(или) уровне картинки или среза. В таких реализациях индикатор режима межпланового кодирования может быть ведущим двоичным разрядом, предусмотренным в заголовке картинки и(или) среза. Например, Фиг.5 иллюстрирует примерную схему 500 синтаксиса на уровне среза в соответствии с различными реализациями настоящего изобретения. Схема 500 включает в себя синтаксис 512 среза/картинки, где нулевое значение для двоичного разряда 504 в заголовке 506 среза/картинки (к примеру, соответствующее первому режиму межпланового кодирования) указывает, что кодированы обе составляющих MVx 506 и MVy 508. Схема 500 также включает в себя синтаксис 508 среза/картинки, где единичное значение для двоичного разряда 504 в заголовке 506 (к примеру, соответствующее второму режиму межпланового кодирования) указывает, что кодированы только составляющие 512 MVx. В некоторых реализациях множество пар 510 из составляющих MVx и MVy могут следовать за заголовком 506 в синтаксисе 502 и(или) множество составляющих 512 MVx могут следовать за заголовком 506 в синтаксисе 508.

Фиг.6 иллюстрирует блок-схему алгоритма примерного процесса 600 для реализации схем межпланового кодирования в видеокодере согласно различным реализациям настоящего изобретения. В различных реализациях процесс 600 может использоваться для указания режима межпланового кодирования с помощью индикатора режима кодирования, введенного в двоичный поток, вырабатываемый, например, кодером 102 МВК в системе 100. Процесс 600 может включать в себя одну или несколько операций, функций или действий, как иллюстрируется одним или несколькими из блоков 602, 604 и 606 на Фиг.6. Посредством неограничивающего примера, процесс 600 будет описан здесь со ссылкой на примерные схемы 400 и 500 синтаксиса межпланового кодирования по Фиг.4 и 5, соответственно, как и на систему 100 по Фиг.1.

Процесс 600 может начинаться в блоке 602, где может быть определен режим межпланового кодирования для по меньшей мере части кадра изображения. Например, блок 602 может затрагивать кодер 102 МВК, определяющий режим межпланового кодирования, соответствующий синтаксису 402 в схеме 400, где кодированные составляющие для множества измерений (к примеру, составляющие MVx и MVy) подлежат включению в двоичный поток 103 для конкретного макроблока текущего кадра изображения. Альтернативно, может быть определен режим межпланового кодирования, соответствующий синтаксису 410 в схеме 400, где кодированные составляющие ВД только для одного измерения (к примеру, только составляющая MVx) подлежат включению в двоичный поток 103 для этого конкретного макроблока.

В различных реализациях блок 602 может включать в себя выборочное определение режима межпланового кодирования. Например, схемы МВК кодирования в соответствии с настоящим изобретением могут применяться к схемам как межпланового предсказания, так и временного предсказания. Например, реализация режимов межпланового кодирования может не описываться, если кодирование текущего кадра зависит только от единственной опорной картинки в той же самой видеопоследовательности (и, значит, только временное предсказание применимо к этому кадру). В таких обстоятельствах флаги или индикаторы режима межпланового кодирования могут быть удалены из синтаксиса двоичного потока или могут не размещаться в нем. С другой стороны, если текущий кадр имеет множество опорных кадров и могут применяться как межплановое, так и временное предсказания, флаги режима межпланового кодирования могут быть выборочно добавлены к синтаксису на основе индекса опорного кадра. Например, флаги режима межпланового кодирования могут быть добавлены в двоичный поток, если индекс кадра с опорным изображением соответствует кадру изображения в видеопоследовательности другого плана. Таким образом, в различных реализациях, если конкретная часть МБ или подблока использует только временное предсказание, то индикаторы режима межпланового кодирования не нужно вводить в двоичный поток. С другой стороны, если конкретная часть МБ или подблока может применять межплановое кодирование, то один или несколько индикаторов режима межпланового кодирования могут быть введены в соответствующий двоичный поток, как описано выше, и т.д.

В блоке 604 может устанавливаться соответствующее значение индикатора режима межпланового кодирования. Например, со ссылкой на схему 400 синтаксиса, ведущий двоичный разряд 404 может устанавливаться кодером 102 МВК, чтобы иметь значение, соответствующее режиму, определенному в блоке 602. Следуя примеру схемы 400, если режим межпланового кодирования, определенный в блоке 602, устанавливает многомерные межплановые векторы движения, то кодер 102 МВК может устанавливать, что ведущий двоичный разряд 404 должен иметь нулевое значение в блоке 604. Если же, с другой стороны, режим межпланового кодирования, определенный в блоке 602, устанавливает только одномерные межплановые векторы движения, то кодер 102 МВК может устанавливать, что ведущий двоичный разряд 404 должен иметь единичное значение в блоке 604. Аналогично, со ссылкой на схему 500 синтаксиса, ведущий двоичный разряд 504 в заголовке 506 среза может устанавливаться кодером 102 МВК в блоке 604, чтобы иметь значение, соответствующее режиму, определенному в блоке 602.

Процесс 600 может завершаться в блоке 606, где индикатор режима межпланового кодирования может встраиваться в двоичный поток. Например, блок 606 может затрагивать кодер 102 МВК в системе 100, вводящий двоичный разряд 404 и(или) двоичный разряд 504 в двоичный поток 103 для указания режима межпланового кодирования, определенного в блоке 602. Как отмечено выше, этот индикатор режима межпланового кодирования может предусматриваться в синтаксисе заголовка картинки и(или) среза в секции УСА среза и(или) в синтаксисе заголовка кодированного элемента МБ или подблока.

Фиг.7 иллюстрирует блок-схему алгоритма примерного процесса 700 для воплощения схем межпланового кодирования в видеодекодере согласно различным реализациям настоящего изобретения. В различных реализациях процесс 700 может использоваться для осуществления компенсации межпланового движения в одном или обоих декодерах 110 и(или) 112 МВК в системе 100, как указано индикатором режима межпланового кодирования, принятым в двоичном потоке, выданном, например, кодером 102 МВК в системе 100. Процесс 700 может включать в себя одну или несколько операций, функций или действий, как показано одним или несколькими из блоков 702, 704 и 706 на Фиг.7. Путем неограничивающего примера процесс 700 будет здесь описан со ссылкой на примерные схемы 400 и 500 синтаксиса межпланового кодирования по Фиг.4 и 6, соответственно, как и на систему 100 по Фиг.1.

Процесс 700 может начинаться в блоке 702, где может быть принят двоичный поток, который включает в себя индикатор режима межпланового кодирования, связанный с по меньшей мере частью кадра изображения. Например, блок 702 может затрагивать декодер 110 МВК, принимающий двоичный поток, который включает в себя индикатор режима межпланового кодирования, как описано здесь. Например, двоичный поток, принятый в блоке 702, может соответствовать двоичному потоку, как предусмотрено в блоке 606 процесса 600, как описано выше.

В блоке 704 может определяться режим межпланового кодирования в ответ на индикатор режима межпланового кодирования, принятый в блоке 702. Например, в зависимости от значения этого индикатора режима межпланового кодирования декодер 110 МВК может определять режим межпланового кодирования в блоке 704. Например, декодер 110 МВК принимает индикатор режима межпланового кодирования, аналогичный тому, что предусмотрен синтаксисом 402 схемы 400, тогда декодер 110 МВК может определить режим межпланового кодирования, где кодированный многоразмерный вектор движения (к примеру, включающий в себя составляющие MVx и MVy) должен использоваться для выполнения компенсации межпланового движения для конкретного макроблока в текущем кадре изображения. Альтернативно, если декодер 110 МВК принимает индикатор режима межпланового кодирования, аналогичный тому, что предусмотрен синтаксисом 410 схемы 400, тогда декодер 110 МВК может определить режим межпланового кодирования, где кодированный одномерный вектор движения (к примеру, включающий в себя составляющую MVx) должен использоваться для выполнения компенсации межпланового движения в этом конкретном макроблоке.

Процесс 700 может завершаться в блоке 706, где может выполняться компенсация межпланового движения для части кадра изображения в ответ на режим межпланового кодирования, определенный в блоке 704. Например, в различных реализациях, в одном режиме межпланового кодирования блок 706 может затрагивать декодер 110 МВК, выполняющий компенсацию межпланового движения для конкретного макроблока с помощью многомерного ВД (к примеру, включающий в себя составляющие MVx и MVy). Альтернативно, в другом режиме межпланового кодирования блок 706 может затрагивать декодер 110 МВК, выполняющий компенсацию межпланового движения для конкретного макроблока с помощью одномерного ВД (к примеру, включающий в себя только составляющую MVx).

Хотя реализации примерных процессов 600 и 700, как показано на Фиг.6 и 7, могут включать в себя осуществление всех блоков, показанных в иллюстрированном порядке, настоящее изобретение не ограничивается в этом отношении и в различных примерах реализация процессов 600 и 700 может включать в себя осуществление только поднабора показанных блоков и(или) в порядке, отличном от показанного.

Помимо этого, любые один или несколько из блоков по Фиг.6 и 7 могут осуществляться в ответ на команды, предоставленные одним или несколькими компьютерными программными продуктами. Такие программные продукты могут включать в себя несущую сигнал среду с командами, которые при их исполнении, например, процессором могут обеспечивать описанные здесь функциональные возможности. Эти компьютерные программные продукты могут предусматриваться в виде машиночитаемых носителей. Так, например, процессор, включающий в себя одно или несколько процессорных ядер, может осуществлять один или несколько блоков, показанных на Фиг.6 и 7, в ответ на команды, подаваемые в этот процессор машиночитаемым носителем.

Как используется в любой описанной здесь реализации, выражение «модуль» относится к любой комбинации программного, программно-аппаратного и(или) аппаратного обеспечения, выполненного с возможностью обеспечить описанные здесь функциональные возможности. Программное обеспечение может быть воплощено как пакет программ, код и(или) набор команд либо команды, а «аппаратное обеспечение», как используется в описанной здесь реализации, может включать в себя, например, по отдельности или в любой комбинации, «зашитую» схему, программируемую схему, схему конечного автомата и(или) программно-аппаратное обеспечение, которое хранит команды, исполняемые программируемой схемой. Модули могут, совместно или по отдельности, быть воплощены как схема, которая образует части большей системы, например, интегральная схема (ИС) (1C), система на кристалле (SoC) и т.д.

Фиг.8 иллюстрирует примерную систему 800 в соответствии с настоящим изобретением. В различных реализациях система 800 может быть медиа системой, хотя система 800 и не ограничена в этом отношении. Например, система 800 может встраиваться в персональный компьютер (ПК) (PC), портативный компьютер, сверхпортативный компьютер, планшет, сенсорную панель, переносной компьютер, карманный компьютер, ручной компьютер, персональный цифровой ассистент (ПЦА) (PDA), сотовый телефон, комбинированный сотовый телефон-ПЦА, телевизор, интеллектуальное устройство (к примеру, смартфон, смарт-планшет или смарт-телевизор), мобильное Интернет-устройство (MID), устройство обмена сообщениями, устройство обмена данными и т.п.

В различных реализациях система 800 включает в себя платформу 802, связанную с дисплеем 820. Платформа 802 может принимать контент из контентного устройства, такого как устройство(-а) 830 контентных услуг или устройство(-а) 840 доставки контента, либо иные аналогичные источники контента. Навигационный контроллер 850, включающий в себя одно или несколько навигационных элементов, может использоваться для взаимодействия с, например, платформой 802 и(или) дисплеем 820. Каждый из этих компонентов подробнее описан ниже.

В различных реализациях платформа 802 может включать в себя любую комбинацию из набора 805 микросхем, процессора 810, оперативной памяти 812, постоянной памяти 814, графической подсистемы 815, приложений 816 и(или) радио 818. Набор 805 микросхем обеспечивает взаимосвязь между процессором 810, оперативной памятью 812, постоянной памятью 814, графической подсистемой 815, приложениями 816 и(или) радио 818. Например, набор 805 микросхем может включать в себя адаптер уст