Способ обеспечения связи в коммуникационной среде, компьютерная система и энергонезависимый машиночитаемый носитель данных

Иллюстрации

Показать всеИзобретение относится к области связи в коммуникационной среде. Техническим результатом является повышение эффективности передачи данных в коммуникационной среде. Раскрыт способ обеспечения связи в коммуникационной среде, включающий: получение процессором коммуникационной среды от отправителя коммуникационной среды предварительного разрешения на преобразование синхронной пересылки данных в асинхронную пересылку данных, причем предварительное разрешение включает получение указания блока памяти для слежения за асинхронной пересылкой данных; получение процессором от отправителя запроса на передачу данных получателю коммуникационной среды; инициирование процессором передачи данных получателю, выполняемой с использованием синхронной пересылки данных; установление процессором необходимости преобразования синхронной пересылки данных в асинхронную пересылку данных; и выполняемое при указанном установлении автоматическое преобразование процессором синхронной пересылки данных в асинхронную пересылку данных для завершения передачи данных получателю, при этом автоматическое преобразование является независимым от любых действий отправителя, кроме предварительного разрешения. 3 н. и 28 з.п. ф-лы, 15 ил.

Реферат

Настоящее изобретение согласно одной из его особенностей относится в целом к поддержанию связи в коммуникационной среде, точнее, к облегчению обмена данными между изолированными областями памяти коммуникационной среды.

Для обмена данными между изолированными областями памяти коммуникационной среды обычно применяются сетевые технические средства и протоколы. В частности, данные могут передаваться от одной изолированной области памяти другой изолированной области памяти с использованием протокола управления передачей/протокола IP (TCP/IP) по каналу сети Ethernet. Существующие сетевые технические средства позволяют передавать данные синхронно или асинхронно. Выбор осуществляется исключительно отправителем.

При синхронной пересылке данных работа отправителя приостанавливается до завершения пересылки данных. С другой стороны, при асинхронной пересылке данных отправитель может продолжать действовать.

Преодоление недостатков известного уровня техники и достижение преимуществ обеспечивается в способе обеспечения связи в коммуникационной среде, включающему: получение процессором коммуникационной среды от отправителя коммуникационной среды предварительного разрешения на преобразование синхронной пересылки данных в асинхронную пересылку данных, причем предварительное разрешение включает получение указания блока памяти для слежения за асинхронной пересылкой данных; получение процессором от отправителя запроса на передачу данных получателю коммуникационной среды; инициирование процессором передачи данных получателю, выполняемой с использованием синхронной пересылки данных; установление процессором необходимости преобразования синхронной пересылки данных в асинхронную пересылку данных; и выполняемое при указанном установлении автоматическое преобразование процессором синхронной пересылки данных в асинхронную пересылку данных для завершения передачи данных получателю, при этом автоматическое преобразование является независимым от любых действий отправителя, кроме предварительного разрешения.

Объектами изобретения являются также компьютерная система, сконфигурированная для осуществления описанного выше способа, а также энергонезависимый машиночитаемый носитель данных, в котором хранятся команды, считываемые и выполняемые устройством обработки данных для осуществления описанного выше способа.

Технический результат, достигаемый при осуществлении изобретения, заключается в облегчении передачи данных в коммуникационной среде за счет указания блока памяти для слежения за асинхронной пересылкой данных, что, в частности, позволяет отправителю регулировать максимальное число не выполненных запросов асинхронной пересылки и автоматизирует асинхронную пересылку данных.

Дополнительные признаки и преимущества изобретения реализованы посредством приемов, раскрытых в описанных вариантах осуществления. В описании подробно рассмотрены другие варианты осуществления и особенности, считающиеся частью заявленного изобретения.

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чего чертежами, на которых:

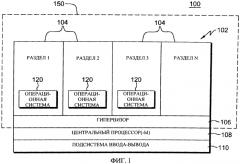

на фиг. 1 проиллюстрирован один из примеров коммуникационной среды, в которой содержится и/или используется одна или несколько особенностей настоящего изобретения,

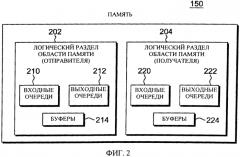

на фиг. 2 - примеры областей памяти, связанных с проиллюстрированными на фиг. 1 логическими разделами согласно одной из особенностей настоящего изобретения,

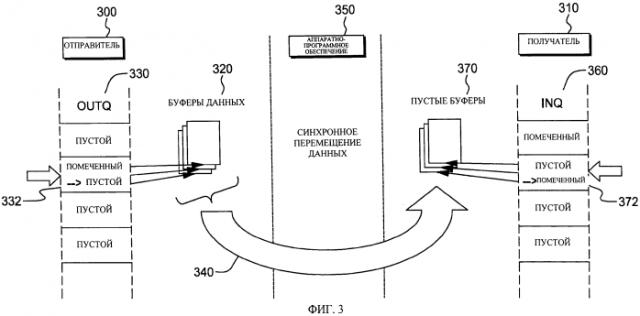

на фиг. 3 - один из примеров исходящей синхронной пересылки данных, используемой согласно одной из особенностей настоящего изобретения,

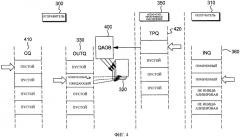

на фиг. 4 - примеры структур управления, используемых для автоматического преобразования синхронной пересылки данных в асинхронную пересылку данных, согласно одной из особенностей настоящего изобретения,

на фиг. 5А - один из вариантов осуществления логики автоматического преобразования синхронной пересылки данных в асинхронную пересылку данных согласно одной из особенностей настоящего изобретения;

на фиг. 5Б - один из наглядных примеров успешного завершения асинхронной пересылки данных согласно одной из особенностей настоящего изобретения;

на фиг. 6 - один из вариантов осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения,

на фиг. 7 - один из вариантов осуществления главной компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 8 - дополнительный пример компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 9 - другой пример компьютерной системы, содержащей компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 10 - один из вариантов осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 11А - один из вариантов осуществления блока выполнения проиллюстрированной на фиг. 10 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 11Б - один из вариантов осуществления блока выполнения команд перехода проиллюстрированной на фиг. 10 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг. 11В - один из вариантов осуществления блока выполнения команд загрузки/сохранения проиллюстрированной на фиг. 10 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения, и

на фиг. 12 - один из вариантов осуществления главной компьютерной системы эмуляции, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

Согласно одной из особенностей настоящего изобретения предложено средство автоматического преобразования синхронной пересылки данных в асинхронную пересылку данных. Например, синхронная пересылка данных автоматически преобразуется в асинхронную пересылку данных, если определено, что завершение пересылки данных задерживается, например, получатель данных не способен принять данные во время пересылки. Преобразование синхронной пересылки данных в асинхронную пересылку данных является автоматическим в том смысле, что оно осуществляется не по запросу отправителя (или получателя), а отправителю (или получателю) не известно о преобразовании в момент его инициации. Кроме того, в момент преобразования отправителю (или получателю) не требуется предпринимать какое-либо действие или вмешиваться в преобразование.

Один из вариантов осуществления коммуникационной среды, в которой содержится и/или используется одна или несколько особенностей настоящего изобретения, описан со ссылкой на фиг.1. В одном из примеров коммуникационная среда 100 содержит комплекс 102 центральных процессоров (CPC), который основан на системе z/Architecture®, предлагаемой International Business Machines Corporation (IBM®). Особенности системы z/Architecture® описаны в публикации № SA 22-7832-08 "IBM® z/Architecture Principles of Operation" (август 2010 г.), которая в порядке ссылки во всей полноте включена в настоящую заявку. Одной из систем, в которых может содержаться комплекс 102 центральных процессоров, является система zEnterprise 196 (z196), предлагаемая International Business Machines Corporation (Армонк, штат Нью-Йорк, США). IBM® и z/Architecture® являются зарегистрированными товарными знаками, а zEnterprise 196 и z196 являются товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Названия других продуктов, используемые в описании, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

Комплекс 102 центральных процессоров содержит, например, один или несколько разделов 104, гипервизор 106, один или несколько центральных процессоров 108 и один или несколько компонентов подсистемы 110 ввода-вывода. В этом примере одним или несколькими разделами 104 являются логические разделы (также известные как LPAR), в которых содержится набор аппаратных ресурсов системы в форме отдельной виртуальной системы.

Каждый логический раздел 104 способен функционировать как отдельная система. Иными словами, каждый логический раздел может независимо возвращаться в исходное состояние, если желательно, в него может осуществляться начальная загрузка операционной системы 120, и он может оперировать различными программами. Операционная система или прикладная программа, выполняемая в логическом разделе, выглядит как имеющая доступ ко всей системе в целом, но, в действительности, для нее доступна только ее часть. За счет сочетания аппаратного обеспечения и лицензионного внутреннего кода (LIC) также называемого аппаратно-программным обеспечением, предотвращается взаимное влияние программы в одном логическом разделе и программы в другом логическом разделе. Это позволяет нескольким различным логическим разделам использовать один или множество физических процессоров в режиме квантования времени. В этом примере несколько логических разделов имеют резидентную операционную систему 120, которая может различаться в одном или нескольких логических разделах. В одном из вариантов осуществления операционной системой 120 является операционная система z/OS®, предлагаемая компанией International Business Machines Corporation (Армонк, штат Нью-Йорк, США).

В контексте настоящего изобретения аппаратно-программное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном из вариантов осуществления оно содержит, например, собственный код, который обычно представляет собой микрокод, содержащий выверенное программное обеспечение или характерный для базового аппаратного обеспечения и управляющий доступом операционной системы к аппаратному обеспечению системы.

Логическими разделами 104 управляет гипервизор 106, который реализован посредством аппаратно-программного, обеспечения действующего в центральных процессорах 108. Одним из примеров гипервизора 106 является администратор ресурсов процессора/системы (Processor Resource/Systems Manager (PR/SM™)), предлагаемый компанией International Business Machines Corporation (Армонк, штат Нью-Йорк, США).

Центральные процессоры 108 являются физическими ресурсами процессора, которые выделяются логическим разделам. Например, логический раздел 104 содержит один или несколько логических процессоров, при этом каждый из них отображает все или часть физических ресурсов 108 процессора, выделенных разделу. Логические процессоры конкретного раздела 104 могут быть закреплены за разделом, и в этом случае ресурсы базового процессора резервируются за этим разделом; или могут использоваться совместно с другим разделом, и в этом случае ресурсы базового процессора потенциально доступны для другого раздела.

Логические разделы 104 и гипервизор 106 в каждом случае могут содержать одну или несколько программ, постоянно хранящихся в соответствующих частях основной памяти 150, связанной с центральными процессорами. В одном из примеров каждому логическому разделу выделена часть основной памяти, именуемая областью памяти, как подробнее описано далее со ссылкой на фиг.2.

Как показано на фиг.2, в одном из вариантов осуществления основная память 150 содержит множество областей памяти, каждая из которых имеет диапазон адресов в основной памяти. Область памяти может быть выделена какому-либо объекту, такому как логический раздел, или другому объекту. В примере, проиллюстрированном на фиг.2, две области памяти выделены, соответственно, двум логическим разделам. Одна область памяти именуется областью 202 памяти отправителя, а другая область памяти именуется областью 204 памяти получателя, поскольку далее дополнительно описана связь между отправителем и получателем. В области 202 памяти отправителя содержится, например, одна или несколько входных очередей 210, одна или несколько выходных очередей 212 и один или несколько буферов 214. Аналогичным образом, в области 204 памяти получателя одна или несколько входных очередей 220, одна или несколько выходных очередей 222 и один или несколько буферов 224. Использование очередей и буферов дополнительно описано далее.

Отдельные области памяти являются изолированными друг от друга в том смысле, что данные не могут записываться непосредственно из одной области памяти в другую область памяти без контроля со стороны аппаратно-программного обеспечения. В одном из примеров для пересылки данных из одной области памяти в другую область памяти применяется сетевая пересылка с использованием, например, протокола TCP/IP по каналам сети Ethernet. В одном из конкретных примеров для осуществления пересылки применяется предлагаемая компанией International Business Machines Corporation технология под названием HiperSockets™.

HiperSockets™ обеспечивает возможность установления высокоскоростной связи по протоколу TCP/IP в комплексе центральных процессоров. При этом исключается потребность в какой-либо физической кабельной сети или внешних сетевых соединениях между серверами, действующими в различных логических разделах. Вместо этого связь осуществляется посредством системной памяти процессора. HiperSockets™ реализована на основе протокола OSA-Express прямого ввода-вывода с организацией очередей (QDIO). Аппаратно-программное обеспечение эмулирует уровень управления каналом интерфейса OSA-Express QDIO.

Пересылка данных из одной области памяти в другую область памяти с использованием сетевых технических средств является, например, синхронным, и в этом случае после инициации пересылки данных работа отправителя приостанавливается до завершения пересылки. Один из примеров синхронной пересылки данных из одной области памяти в другую описан ссылкой на фиг.3.

Как показано на фиг.3, отправитель 300, такой как стек протоколов TCP/IP или программа, действующая в области памяти отправителя, инициирует запрос на передачу данных получателю 310, такому как другой стек протоколов TCP/IP или программа, например в области памяти получателя. Поскольку в этом примере область памяти получателя изолирована от области памяти отправителя, для осуществления синхронной передачи данных от отправителя получателю используется протокол сетевой связи. Использование синхронной пересылки данных обеспечивает канал высокоскоростной прямой связи с малым временем ожидания между отправителем и получателем путем пересылки данных из одной области памяти в другую под управлением аппаратно-программного обеспечения. В одном из примеров пересылка данных из одной области памяти в другую осуществляется посредством HiperSockets™. Этот механизм пересылки является очень эффективным, поскольку получатель может принимать данные с той же или более высокой скоростью, чем скорость передачи данных отправителем.

Для пересылки данных отправитель извлекает данные, которые содержатся в выбранном буфере 320 данных, и помещает их в выходную очередь 330 отправителя (OUTQ). Например, в выходную очередь помещается указатель 332 выбранного буфера данных. Затем отправитель 300 передает процессору сигнал 340 осуществления пересылки данных получателю 310. В одном из примеров сигнал передается аппаратно-программному обеспечению 350 процессора, которое собирается осуществлять пересылку; тем не менее, в других примерах сигнал передается не аппаратно-программному обеспечению, а другому коду и/или аппаратному обеспечению процессора.

В ответ на прием сигнала с запросом пересылки данных от отправителя получателю аппаратно-программное обеспечение копирует данные из выходной очереди отправителя и помещает их во входную очередь 360 получателя (INQ). Например, данные копируются в пустой буфер 370, а указатель 372 этих данных помещается во входную очередь 360. После завершения пересылки данных аппаратно-программное обеспечение передает отправителю сигнал завершения пересылки. Пока отправитель не примет этот сигнал завершения, его работа приостанавливается, и он не может выполнять какие-либо другие операции.

В качестве одного из конкретных примеров, чтобы передать сигнал процессору, отправитель передает команду адаптера сигналов (SIGA, от английского - Signal Adapter) с указанием функции записи (SIGA-w), которая сообщает процессору о том, что в одной или нескольких выходных очередях содержатся данные для передачи получателю. Функция записи задана в виде кода функции, содержащегося в первом общем регистре общего назначения, используемом командой, а во втором регистре общего назначения, используемом командой, указан адрес сетевого соединения (например, идентификатор подсистемы) функции записи. Кроме того, в еще одном, третьем регистре общего назначения, используемом командой, заданы выходные очереди.

В этом конкретном примере очереди реализованы в виде очередей прямого доступа с организацией очередей (QDIO), при этом каждая очередь имеет множество связанных с ней буферов, а также различную управляющую информацию. В одном из вариантов осуществления очередь QDIO содержит структуры данных, описывающие очередь, а также блоки буферных запоминающих устройств, которые используются для пересылки данных. В качестве одного из примеров, структуры данных множества запоминающих устройств, называемые компонентами очереди, которые собирательно описывают характеристики очереди и обеспечивают средства управления для обмена данными, включают, например:

блок информации очереди (QIB), в котором содержится информация о совокупности входных и выходных очередей QDIO. В QIB содержится адрес блока информации из списка запоминающих устройств (SLIB) для входных очередей и адрес SLIB для выходных очередей.

Для каждой очереди существует один SLIB, и в каждом SLIB содержится информация об очереди и о каждом буфере очереди. Каждый SLIB имеет заголовок и один или несколько элементов, называемых элементами блока информации из списка запоминающих устройств (SLIBE), в которых содержится информация о каждом из буферов очереди. В одном из примеров каждый блок информации из списка запоминающих устройств содержит адрес следующего блока информации из списка запоминающих устройств, адрес списка запоминающих устройств (SL) и адрес блока состояния списка запоминающих устройств (SLSB).

Для каждой очереди определен один список запоминающих устройств, который содержит, например, 128 записей, по одной на каждый из буферов очереди. Список запоминающих устройств содержит информацию о местоположениях буферов ввода-вывода в основной памяти. В каждой записи содержится абсолютный адрес списка адресов блоков запоминающих устройств (SBAL). Каждый список адресов блоков запоминающих устройств содержит список абсолютных адресов блоков запоминающих устройств, которые в совокупности образуют один из буферов данных, связанных с каждой очередью.

В состав каждого SBAL входит запись из списка блоков запоминающих устройств (SBALE). В каждом SBALE содержится абсолютный адрес блока запоминающего устройства. В совокупности блоки запоминающих устройств, адресуемые всеми записями отдельного SBAL, образуют один из множества возможных буферов QDIO очереди QDIO. В одном из примеров очередь QDIO может содержать 128 связанных с ней буферов QDIO.

В SLSB содержатся индикаторы состояния, которые обеспечивают информацию о состоянии буферов, которые образуют очередь.

Дополнительные подробности, касающиеся SIGA, очередей QDIO и соответствующих структур управления, описаны в патенте US 6332171 B1 под названием "Self-Contained Queues With Associated Control Information For Receipt And Transfer Of Incoming And Outgoing Data Using A Queued Direct Input-Output Device" на имя Baskey и др., выданном 18 декабря 2001 г.; патенте US 6345241 B1 под названием "Method And Apparatus For Simulation Of Data In a Virtual Environment Using A Queued Direct Input-Output Device" на имя Brice и др., выданном 5 февраля 2002 г.; патенте US 6519645 B2 под названием "Method And Apparatus For Providing Configuration Information Using A Queued Direct Input-Output Device" на имя Markos и др., выданном 11 февраля 2003 г.; и патенте US 7941799 B2 под названием "Interpreting I/O Operation Requests From Pageable Guests Without Host Intervention" на имя Easton и др., выданном 10 мая 2011 г.

Когда при описанной обработке получатель не способен использовать пустые буферы с такой же скоростью, с которой отправитель передает данные, на стороне отправителя увеличивается время ожидания и затраты ресурсов ЦП в силу синхронной природы протокола. Когда пустой буфер недоступен для получателя, у отправителя существует два варианта. Он может пойти на затраты ресурсов на постановку в очередь невыполненной операции и последующую повторную передачу данных тому же получателю или отбросить данные, чтобы протокол связи более высокого уровня, такой как TCP/IP, мог снова привести в действие операцию. Сложности постановки в очередь и повторной передачи данных заключаются в том, что для этого не только требуется восстановление дополнительных циклов ЦП, но потенциально могут блокироваться или задерживаться последующие передачи отправителем данных другим адресатам, которые могут быть способны принимать поступающие данные.

В виртуальных средах, в которых множество серверов (например, отправители, получатели) могут совместно использовать ресурсы ЦП, с большей вероятностью возникают ситуации, в которых получатель может быть не способен поддерживать скорость, с которой различные отправителю передают ему данные. Это обычно происходит, когда гипервизор, такой как PR/SM управляет диспетчеризацией серверов в различных доступных совместно используемых процессорах. Задача решается, когда между отправителем и совместно используемым ресурсом ЦП имеются гипервизоры множества уровней. Это имеет место, например, когда отправитель действует в виртуальной машине под управлением z/VM®, которая также действует в логическом разделе. В данном случае два гипервизора должны осуществлять диспетчеризацию сервера таким образом, чтобы он своевременно восполнял пустые буферы.

Своевременная диспетчеризация получателя не создает затруднений при наличии достаточных доступных ресурсов ЦП. Синхронная пересылка данных прерывается только при ограниченности ресурсов ЦП в течение короткого или длительного времени. Так, согласно одной из особенностей настоящего изобретения отправитель способен использовать синхронную передачу данных с малым временем ожидания в среде без ограничения ресурсов ЦП с одновременным устранением сопутствующих трудностей и затрат, когда ресурсы ЦП становятся ограниченными. Это достигается путем преобразования протокола синхронного обмена в протокол асинхронного обмена, когда получатель не способен поддерживать скорость передачи данных отправителем. В одном из вариантов осуществления протокол синхронного обмена преобразуется в протокол асинхронного обмена автоматически без какого-либо уведомления отправителя (т.е. отправителю не требуется совершать какое-либо действие в момент преобразования). Тем самым отправитель освобождается от необходимости выполнять восстановление какого-либо типа или блокировать или замедлять передачу данных другим получателям, когда ресурсы ЦП становятся ограниченными для конкретного получателя. Кроме того, синхронная передача данных получателю с ранее ограниченными ресурсами может возобновляться автоматически.

Согласно одной из особенностей настоящего изобретения предложено средство организации отправителем очереди данных в своей памяти, пока получатель не обеспечит пустые буферы, которые могут принять данные. С целью облегчения этого используется одна или несколько структур управления, описанных со ссылкой на фиг.4. Например, отправитель выделяет пустой блок 400 в своей каждой незавершенной асихронной пересылке. В одном из примеров число этих блоков в любой момент времени может составлять X, при этом X является зависящей от модели и конфигурируемой величиной. X отображает число одновременных запросов асинхронной пересылки, разрешенных отправителем. Этот блок памяти, именуемый блоком асинхронных операций QDIO (прямого ввода-вывода с организацией очередей) (QAOB), используется, чтобы следить за асинхронной пересылкой данных, пока аппаратно-программное обеспечение не завершит операцию. В этом примере в QAOB содержится только управляющая информация, а не сами данные. Отправитель использует этот блок при инициировании пересылки данных для запросов, которые он асинхронное выполнение которых он необязательно разрешит; в противном случае ему не требуется обеспечивать блок управления. Это позволяет отправителю регулировать максимальное число не выполненных запросов асинхронной пересылки. QAOB как таковой используется и инициализируется только аппаратно-программным обеспечением, когда оно определяет, что пересылка данных должна осуществляться асинхронно. От отправителя не требуется каких-либо действий для пересылки данных помимо обеспечения памяти для QAOB, если пересылка данных должна осуществляться асинхронно.

В одном из конкретных примеров QAOB включен в команду SIGA, в которой содержится запрос. Отправитель передает команду записи SIGA с QAOB (SIGA-wq) с указанием выбранного кода функции в первом регистре общего назначения, в котором указана функция записи с QAOB. В четвертом регистре общего назначения, используемом командой, указан адрес QAOB. Этот регистр общего назначения имеет значение 0, когда QAOB не указан, или содержит абсолютный адрес QAOB (например, 256-байтового QAOB). В ответ на заданный код функция записи с QAOB аппаратно-программное обеспечение определяет, указан ли в четвертом регистре общего назначения QAOB, который может использоваться при асинхронной пересылке данных.

Когда аппаратно-программное обеспечение изменяет протокол пересылки данных на асинхронный, оно использует QAOB для слежения за данными, постоянно хранящимися в памяти отправителя, связанной с пересылкой исходящих данных. В примере, в котором для передачи используется HiperSockets™, QAOB следит за адресами и средствами управления, указанными отправителем в списке адресов блоков запоминающих устройств (SBAL), связанном с пересылкой данных. Примеры полей, извлекаемых из SBAL и помещаемых в QAOB, включают, например:

все значащие SBALE из SBAL (например, первый SBALE для SBALE с установленным разрядом последней записи). Они содержат абсолютный адрес буфера данных и счет байтов;

номер выходной очереди SBAL,

номер буфера (например, 1-27) SBAL, инициирующего запрос,

число значащих записей SBALE и

ключ хранения, используемый для доступа к блокам запоминающего устройства, указанным каждым значащим SBALE.

Помимо QAOB используется другая управляющая структура, именуемая очередью 410 завершения (CQ). Иными словами, в одном из примеров помимо обеспечения QAOB отправитель также выделяет в своей памяти очередь нового типа, а именно, очередь завершения при формировании очереди передаваемых данных. В случае HiperSockets™ ей является входная очередь QDIO с SBAL, но без буферов, связанных с SBALE. Эта новая входная очередь используется не для пересылки данных, а используется аппаратно-программным обеспечением для сообщения о событиях завершения, чтобы уведомить отправителя о завершении асинхронной пересылки данных. Когда поступление в очередь помечается как "входящее", информация о событии завершения находится в самих SBALE, которые включены в очередь завершения. Аппаратно-программное обеспечение сообщает адрес QAOB, связанного с завершенной асинхронной пересылкой данных в CQ, и при необходимости генерирует прерывание, чтобы уведомить отправителя о завершенной пересылке данных. На этом этапе отправитель может повторно использовать в других целях память, связанную с завершенной операцией. (В одном из вариантов осуществления для сообщения об одном событии завершения используется SBALE. Поскольку SBAL содержит, например, 16 SBALE, аппаратно-программное обеспечение может сообщать о вплоть до 16 событиях завершения (QAOB) в одном SBAL.)

Кроме того, в одном из вариантов осуществления аппаратно-программное обеспечение формирует для предполагаемого получателя другую очередь TPQ 420, которая используется, чтобы запоминать, что имеется невыполненный запрос пересылки данных.

Дополнительные подробности преобразования синхронной пересылки данных в асинхронную пересылку данных описаны со ссылкой на фиг.5А-5Б. На фиг.5А проиллюстрирован один из вариантов осуществления логики, используемой аппаратно-программным обеспечением для выполнения преобразования, а на фиг.5Б наглядно проиллюстрирован один из примеров преобразования. Обе фигуры рассмотрены далее в описании.

Как показано на фиг.5А-5Б, сначала на шаге 500 аппаратно-программное обеспечение 350 принимает указание QAOB (например, адрес блока запоминающего устройства, который может использоваться для асинхронной пересылки данных). Соответственно, ему известно, что при необходимости (или при желании) оно может асинхронно выполнить запрошенную пересылку данных. В одном из вариантов осуществления аппаратно-программное обеспечение может принимать множество QAOB, указывающих, что оно может выполнить вплоть до указанного числа асинхронных пересылок данных. Предоставление QAOB отправителем является предварительным разрешением аппаратно-программному обеспечению на выполнение асинхронной пересылки данных, если она выбрана аппаратно-программным обеспечением.

В одном из конкретных примеров QAOB включен в состав запроса пересылки данных, который аппаратно-программное обеспечение принимает на шаге 502 от отправителя 300. В ответ на прием запроса пересылки данных на шаге 504 аппаратно-программное обеспечение пытается передать данные получателю. Если на шаге 506 запроса установлено, что получатель способен принять данные (например, у получателя имеется пустой буфер), данные синхронно пересылаются на шаге 508, и пересылка данных завершается. После этого, отправитель может выполнить другую пересылку данных, а, если отправителем разрешена асинхронная обработка, он может включить QAOB в новый запрос.

Тем не менее, если получатель не способен в данный момент принять данные (например, как определено состоянием буферов, у получателя отсутствует пустой буфер, и, соответственно, прием данных получателем задерживается), запрос пересылки данных автоматически преобразуется аппаратно-программным обеспечением из синхронного в асинхронный при условии, что в запросе содержится QAOB. Запрос сохраняется в QAOB на шаге 510, и QAOB помещается в очередь TPQ 420 планируемого пункта назначения, например, путем помещения указателя QAOB в TPQ на шаге 512. Теперь в QAOB входит содержимое SBAL, и, соответственно, SBAL может использоваться для другой обработки.

В одном из вариантов осуществления, если QAOB не указан, запрос не выполняется или ожидает возможности синхронной передачи.

В одном из примеров в ответ на постановку QAOB в очередь управление передается серверу-отправителю с указанием того, что для этой асинхронной пересылки данных используется заданный QAOB. Затем сервер-отправитель может немедленно настроиться на свою следующую пересылку данных и необязательно выделить другой QAOB, если он необходим для следующей пересылки данных.

Затем на шаге 514 запроса определяется, способен ли получатель принять данные. Например, определяется, приняло ли аппаратно-программное обеспечение от получателя сигнал, указывающий, что получатель в настоящее время способен принять данные (например, имеются доступные пустые буферы), или установило ли аппаратно-программное обеспечение, что имеется доступный буфер путем проверки состояния буферов. В одном из конкретных примеров получатель использует команду SIGA для передачи аппаратно-программному обеспечению сигнала, указывающего, что получатель поместил пустые буферы в свои входные очереди. В первом регистре общего назначения указан код функции чтения SIGA (SIGA-r). Функция чтения SIGA побуждает аппаратно-программное обеспечение к пересылке любых ожидающих пакетов из очереди TPQ получателя во входные буферы целевого объекта.

Если получатель не способен принять данные, аппаратно-программное обеспечение переходит к ожиданию. В противном случае, если получатель способен принять данные (например, имеется по меньшей мере один пустой буфер), аппаратно-программное обеспечение на шаге 518 запроса определяет, имеет ли оно указатель QAOB в очереди TPQ получателя. Если это не так, обработка завершается. В противном случае аппаратно-программное обеспечение использует QAOB для пересылки данных. В частности, оно пересылает получателю данные, указанные QAOB, помещая данные в пустой буфер и помещая указатель теперь заполненного буфера во входную очередь получателя.

После этого аппаратно-программное обеспечение на шаге 520 указывает отправителю, что пересылка данных завершена. В одном из примеров в этом указании сообщается адрес QAOB, связанного с завершенной асинхронной пересылкой данных, в очереди 410 завершения (фиг.5Б) отправителя, и при необходимости генерируется прерывание 550, чтобы сообщить отправителю о завершенной пересылке данных. На этом этапе отправитель может повторно использовать в других целях память, связанную с завершенной операцией. QAOB, указанный в CQ, содержит информацию, касающуюся асинхронной обработки, включая, например, информацию о состоянии, коды завершения, коды ошибок и т.д.

В одном из конкретных примеров, когда в поступлении в очередь завершения указан адрес QAOB (т.е. адрес QAOB включен в SBALE в одно из поступлений в очередь завершения), аппаратно-программное обеспечение возвращает программе в QAOB следующую информацию, например:

код причин, отражающий результаты асинхронной операции ввода-вывода,

состояние буферов: "состояние очереди - буфера N (SQBN)" для асинхронной пересылки данных. Оно имеет такое же значение, которое было бы помещено в SLSB для синхронной пересылки данных. В SQBN содержится значение, указывающее текущее состояние QAOB. Значение переменной состояния содержит, например, две части: в первой части указано, принадлежит ли буфер аппаратно-программному обеспечению, а во второй части, указано текущее состояние процесса QAOB.

Хотя конкретный запрос выполняется асинхронно, другие запросы отправителя, адресованные другим получателям, могут выполняться синхронно, если только, например, прием данных конкретным получателем не задерживается. Кроме того, другие запросы, адресованные получателю отправителем, автоматически преобразуются в синхронные, если только снова не установлено, что прием данных получателем задерживается. Например, аппаратно-программное обеспечение пытается передать данные получателю, как описано выше, и, если получатель способен принять данные, они передаются синхронно. В одном из вариантов осуществления даже при взаимном преобразовании синхронной и асинхронной передачи, обработка данных осуществляется в порядке поступления как при передаче. Аппаратно-программное обеспечение переносит все ожидающие обслуживания QAOB в очередь TPQ 420 получателя до приема каких-либо будущих синхронных запросов от этого или любого другого отправителя. При попытке другой синхронной пересылки данных получателю, у которого QAOB уже помещены в его TPQ 420, она будет автоматически преобразована в асинхронный запрос аппаратно-программным обеспечением (если это разрешено отправителем) или окажется неудачной, и будет получен ответ "отсутствуют доступные буферы". Сохранение порядка позволяет избегать дорогостоящей обработки с целью переупорядочения, повышать эффективность стека протоколов TCP/IP получателя и общего использования ЦП.

Выше было подробное описано средство автоматического преобразования синхронной пересылки данных в асинхронную пересылку данных в ответ на установление процессором (например, аппаратно-программным обеспечением) того, что такое преобразование должно произойти. Например, преобразование осуществляется, если задерживается прием данных получателем (например, из-за отсутствия доступного буфера, медленного реагирования и т.д.). Кроме того, средство автоматически позволяет синхронно