Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеГруппа изобретений относится к области передачи данных и может быть использована для кодирования/декодирования с использованием кода LDPC. Техническим результатом является повышение устойчивости к ошибкам данных. Кодер LDPC выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2. Матрица Н проверки на четность кода LDPC выполнена посредством размещения элементов 1 информационной матрицы, определенных на основе таблицы исходного значения матрицы проверки на четность для матрицы Н проверки на четность, представляющей положения элементов 1 информационной матрицы в соответствии с длиной информации, длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбцов в период 72 столбца. 4 н. и 3 з.п. ф-лы, 146 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и к способу обработки данных, и, более конкретно, например, к устройству обработки данных и способу обработки данных, которые выполнены с возможностью повышения устойчивости к ошибке данных.

Уровень техники

Код LDPC (проверки на четность низкой плотности) имеет высокую способность коррекции ошибок и, в последнее время, например, началось его широкое использования для системы передачи, которая включает в себя спутниковую цифровую широковещательную передачу данных, такую как DVB (Цифровая широковещательная передача видеоданных)-S.2 (например, см. Непатентный документ 1), которая используется в Европе. Кроме того, пересматривается возможность использования кода LDPC для наземной цифровой широковещательной передачи следующего поколения.

В соответствии с последними исследованиями, можно понять, что при использовании кода LDPC, аналогично турбокоду и т.п., могут быть достигнуты возможности, близкие к пределу Шеннона, по мере увеличения длины кода. Кроме того, поскольку код LDPC имеет такое свойство, что минимальное расстояние представляет собой пропорцию длины кода, LDPC имеет хорошую характеристику относительно вероятности ошибки блоков и имеет преимущество, состоящее в том, что так называемое, явление нижнего уровня ошибки, которое наблюдается в характеристиках декодирования Турбо кода и т.п., в основном, не возникает.

Далее код LDPC будет описан более конкретно. Код LDPC представляет собой линейный код и здесь будет описан, как имеющий две размерности, что не является необходимым.

Код LDPC имеет отличительную характеристику, состоящую в том, что матрица проверки на четность, которая определяет код LDPC, является разреженной. Здесь разреженная матрица представляет собой матрицу, в которой число элементов "1" матрицы очень мало (матрица, в которой большая часть элементов представляют собой "0").

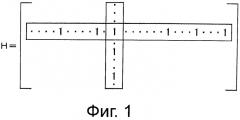

На фиг.1 иллюстрируется пример матрицы Н проверки на четность кода LDPC.

В матрице Н проверки на четность, показанной на фиг.1, вес (количество "1") (вес столбца) каждого столбца составляет "3", и вес (вес строки) каждой строки составляет "6".

При кодировании (кодировании LDPC) в соответствии с кодом LDPC, например, матрицу G генерирования генерируют на основе матрицы Н проверки на четность, и кодовое слово (код LDPC) генерируют путем умножения битов информации в двух размерностях на матрицу G генерирования.

Более конкретно, устройство кодирования, которое выполняет кодирование LDPC, вначале вычисляет матрицу G генерирования, которая удовлетворяет уравнению GHT=0 при HT, представляющей собой транспонированную матрицу для матрицы Н проверки на четность. Здесь, в случае, когда матрица G генерирования представляет собой матрицу К×N, устройство кодирования генерирует кодовое слово с (=uG), формируемое N битами, путем умножения матрицы G генерирования на строку битов (вектор u) битов информации, сформированных К битами. Кодовое слово (код LDPC), которое генерируется с помощью устройства кодирования, принимают на стороне приема через заданный канал связи.

Декодирование кода LDPC представляет собой алгоритм, предложенный Галлагером, который назвал его вероятностным декодированием, и может быть выполнено в соответствии с алгоритмом передачи сообщений, который основан на распространении доверия, о так называемом, графе Таннера, который сформирован переменным узлом (также называется узлом сообщения) и проверочным узлом. Ниже переменный узел и проверочный узел будут просто называться узлами, в соответствующих местах.

На фиг.2 иллюстрируется последовательность декодирования кода LDPC.

Ниже реальное значение (принятый LLR), который получают путем представления вероятности "0" для значения i-ого кодового бита для кода LDPC (одно кодовое слово), который принимают на стороне приема, как логарифмическое отношение правдоподобия, также будет называться принятым значением u0i, насколько это соответствует. Кроме того, сообщение, которое выводят из узла проверки, обозначено, как uj, и сообщение, которое выводят от переменного узла, обозначено, как vi.

Вначале, при декодировании кода LDPC, как показано на фиг.2, на этапе S11, код LDPC инициализирует сообщение (сообщение узла проверки) uj, переводя его в "0", переменную k, которая принимает целое число, как счетчик процесса повторения, инициализируют, сбрасывая ее в "0", и обработка переходит на этап S12. На этапе S12, на основе принятого значения u0i, которое получают путем приема кода LDPC, получают сообщение (сообщение переменного узла) vi, выполняя вычисление (вычисление переменного узла), представленное в Уравнении (1), и сообщение uj получают, выполняя вычисление (вычисление проверочного узла), представленное в Уравнении (2), на основе сообщения vi.

Уравнение 1

Уравнение 2

Здесь dv и dc, представленные в Уравнениях (1) и (2), представляют собой параметры, которые представляют количество "1" матрицы Н проверки на четность в вертикальном направлении (столбец) и в горизонтальном направлении (строка), которые могут быть выбраны произвольно, и, например, в случае кода (3, 6), dv=3 и dc=6.

Кроме того, при вычислении переменного узла в соответствии с Уравнением (1) и при вычислении проверочного узла в соответствии с Уравнением (2), каждое сообщение, вводимое из ответвления (ребра) (линия, соединяющая переменный узел и проверочный узел), в который должно быть выведено сообщение, не установлено, как цель вычисления, и, соответственно, диапазоны вычисления составляют от 1 до dv-1 и от 1 до dc-1. Вычисление проверочного узла, представленное в Уравнении (2), фактически выполняют путем комбинирования таблицы функции R (v1, v2), представленной в Уравнении (3), которая определена, как выход двух входов v1 и v2, заранее и последовательно (рекурсивно), используя таблицу, представленную в Уравнении (4).

Уравнение 3

Уравнение 4

Кроме того, на этапе S12, переменную k последовательно увеличивают на единицу, и обработка переходит на этап S13. На этапе S13 определяют, больше или нет переменная k заданного количества С повторений декодирования. На этапе S13, в случае, когда переменную k определяют, как не большую, чем С, обработка возвращается на этап S12, и ту же обработку повторяют.

С другой стороны, в случае, когда переменную k определяют, как превышающую С, на этапе S13, обработка переходит на этап S14, сообщение vi, как результат декодирования, который выводят в конечном итоге, получают, выполняя вычисление, представленное в Уравнении (5), и выводят, на чем обработка декодирования кода LDPC заканчивается.

Уравнение 5

Здесь вычисление, представленное в Уравнении (5), в отличие от вычисления переменного узла, представленного в Уравнении (1), выполняют, используя сообщение uj, подаваемое из всех ответвлений, которые соединены с переменным узлом.

На фиг.3 иллюстрируется пример матрицы Н проверки на четность для кода LDPC (3, 6) (скорость кодирования 1/2, длина кода 12).

В матрице Н проверки на четность, представленной на фиг.3, аналогично тому, что показано на фиг.1, вес столбца равен 3, и вес строки равен 6.

На фиг.4 иллюстрируется граф Таннера матрицы Н проверки на четность, представленной на фиг.3.

Здесь, на фиг.4, узел, который обозначен знаком "плюс" "+", представляет собой проверочный узел, и узел, который обозначен знаком "равенства" "=", представляет собой переменный узел. Проверочный узел и переменный узел соответствуют строке и столбцу матрицы Н проверки на четность. Линия, проведенная между проверочным узлом и переменным узлом, представляет собой ответвление (ребро) и соответствует "1" элемента матрицы проверки на четность.

Другими словами, в случае, когда элемент j-ой строки и i-ого столбца матрицы проверки на четность равен "1", на фиг.4, i-ый переменный узел (узел "=") сверху и j-ый проверочный узел (узел "+") сверху соединены ответвлением. Ответвление представляет, что кодовый бит, соответствующий переменному узлу, имеет ограниченное условие, соответствующее проверочному узлу.

Алгоритм суммы - произведения, представляет собой способ декодирования кода LDPC, в котором вычисление переменного узла и вычисление проверочного узла выполняются многократно.

На фиг.5 иллюстрируется вычисление переменного узла, которое выполняют на переменном узле.

В переменном узле сообщение vi, которое соответствует ответвлению, которое представляет собой цель вычисления, получают с помощью вычисления переменного узла, который представлен в Уравнении (1), используя сообщения u1 и u2, подаваемые из остальных ответвлений, соединенных с переменным узлом, и принятое значение u0i. Сообщения, которые соответствуют другим ответвлениям, получают таким же образом.

На фиг.6 иллюстрируется вычисление проверочного узла, которое выполняют в проверочном узле.

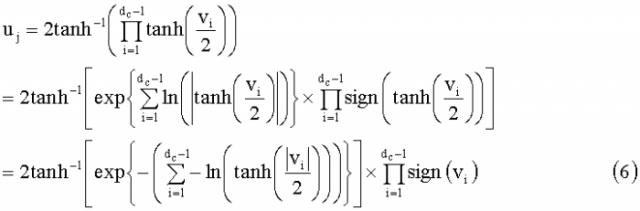

Здесь вычисление проверочного узла, представленное в Уравнении (2), может быть перезаписано в Уравнение (6), используя уравнения а×b=exp{ln(|а|)+ln(|b|)}×sign(a)×sign(b). Здесь, sign (х) представляет собой 1, когда х≥0, и представляет собой -1, когда х<0.

Уравнение 6

В случае, когда х≥0, когда функция φ(х) определена, как уравнение φ(х)=ln(tanh(х/2)), уравнение φ-1(х)=2tanh-1(e-x), удовлетворяется, и, соответственно. Уравнение (6) может быть преобразовано в Уравнение (7).

Уравнение 7

В проверочном узле вычисление проверочного узла, представленное в Уравнении (2), выполняют на основе Уравнения (7).

Другими словами, в проверочном узле, как представлено на фиг.6, сообщение uj, которое соответствует ответвлению, которое представляет собой цель вычисления, может быть получено путем вычисления проверочного узла, представленного в Уравнении (7), используя сообщения v1, v2, v3, v4 и v5, подаваемые из остальных ответвлений, соединенных с проверочным узлом. Сообщения, соответствующие другим ответвлениям, получают таким же образом.

Кроме того, функция ϕ(х), представленная в Уравнении (7), может быть представлена, как уравнение of ϕ(х)=ln((ex+1)/(ex-1)), и ϕ(х)=ϕ-1(х) for х>0. При выполнении функции ϕ(х) и ϕ-1(х) в аппаратных средствах, возникают случаи, когда функции воплощают, используя LUT (справочные таблицы), и LUT являются одинаковыми для обеих функций.

Список литературы

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302 307 VI. 1.2 (2006-06)

Раскрытие изобретения

Задачи, решаемые изобретением

Код LDPC используется в DVB-S.2, который представляет собой стандарт спутниковой цифровой широковещательной передачи, или DVB-T.2, который представляет собой стандарт наземной цифровой широковещательной передачи следующего поколения. Кроме того, код LDPC, как планируется, должен использоваться в DVB-C.2, который представляет собой стандарт цифровой широковещательной передачи CATV следующего поколения (кабельное телевидение).

В цифровой широковещательной передаче, которая соответствует стандарту DVB, такому, как DVB-S.2, код LDPC установлен (символизирован), как символ ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная манипуляция с фазовым сдвигом), и символ преобразуют на сигнальную точку и передают.

При символизации кода LDP обмен кодовыми битами кода LDPC выполняют в единицах по два или больше кодовых битов, и кодовые биты после обмена рассматриваются, как символьные биты.

Для обмена кодовыми битами для символизации кода LDPC, предложены различные системы, и, например, такие системы определены также в DVB-T.2.

Однако, DVB-T.2 представляет собой стандарт цифровой широковещательной передачи, который специализированно используют для фиксированных оконечных устройств, таких как телевизионные приемники, установленные в домах и т.п., и, может не соответствовать цифровой широковещательной передаче, которая специально используется для мобильных оконечных устройств.

Другими словами, размеры схемы мобильных оконечных устройств должны быть меньшими, чем у фиксированных оконечных устройств, и должно быть достигнуто меньшее потребление энергии мобильным оконечным устройством. В соответствии с этим, при цифровой широковещательной передаче, которая специально используется для мобильных оконечных устройств, для уменьшения нагрузки, необходимой для обработки, такой как декодирование кода LDPC и т.п. в мобильном оконечном устройстве, например, возникают случаи, когда количество повторений при декодировании кода LDPC (количество С повторений) или длина кода LDPC ограничены в большей степени, чем при цифровой широковещательной передачи, которая специально используется для фиксированных оконечных устройств.

Однако, даже при таких ограничениях, устойчивость к ошибкам должна поддерживаться в определенной степени.

Настоящее изобретение было разработано с учетом такой ситуации и предназначено для улучшения устойчивости к ошибке данных, таких как код LDPC.

Решения задач

В соответствии с первым аспектом настоящего изобретения, предложено устройство обработки данных или способ обработки данных, включающие в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, при этом матрица проверки на четность кода LDPC составлена путем размещения элементов 1 информационной матрицы, определенных на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующих длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбцов, с периодом 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

В соответствии со вторым аспектом настоящего изобретения, предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

В соответствии с третьим аспектом настоящего изобретения предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5 458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

1074 1353 1235 1391.

В соответствии с четвертым аспектом настоящего изобретения предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

В соответствии с пятым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

В соответствии с шестым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

В соответствии с седьмым аспектом настоящего изобретения, предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

1074 1353 1235 1391.

В соответствии с восьмым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 13 исходного значения 6 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

В соответствии с первым - четвертым аспектами настоящего изобретения, кодирование выполняют, используя код LDPC, имеющий длину кода 4320 битов и скорость кодирования 1/2, 7/12, 2/3 или 3/4.

В соответствии с пятым - восьмым аспектами настоящего изобретения, выполняют декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, 7/12, 2/3 или 3/4.

Матрицу проверки на четность кода LDPC выполняют путем размещения элементов 1 информационной матрицы, которые определены на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации, в соответствии с длиной кода и скоростью кодирования для каждых из 72 столбцов, в направлении столбцов за период 72 столбца, и таблицу исходного значения матрицы проверки на четность кода LDPC, имеющую скорость кодирования 1/2 формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

Кроме того, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 7/12, формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

Также, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 2/3, формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

107 41353 1235 1391.

Кроме того, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 3/4, формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

Здесь устройство обработки данных может представлять собой независимое устройство или внутренний блок, составляющий устройство.

Эффекты изобретения

В соответствии с первым - восьмым аспектами может быть повышена устойчивость к ошибкам.

Краткое описание чертежей

На фиг.1 показана схема, которая иллюстрирует матрицу Н проверки на четность кода LDPC.

На фиг.2 показана блок-схема последовательности операций, представляющая последовательность декодирования кода LDPC.

На фиг.3 показана схема, которая иллюстрирует пример матрицы проверки на четность кода LDPC.

На фиг.4 показана схема, которая иллюстрирует граф Таннера матрицы проверки на четность.

На фиг.5 показана схема, иллюстрирующая узел колебаний.

На фиг.6 показана схема, иллюстрирующая проверочный узел.

На фиг.7 показана схема, которая иллюстрирует пример конфигурации системы передачи в соответствии с вариантом осуществления настоящего изобретения.

На фиг.8 показана блок-схема, представляющая пример конфигурации устройства передачи 11.

На фиг.9 показана блок-схема, представляющая пример конфигурации перемежителя битов 116.

На фиг.10 показана схема, которая иллюстрирует матрицу проверки на четность.

На фиг.11 показана схема, иллюстрирующая матрицу четности.

На фиг.12 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, который определен в стандарте DVB-S.2.

На фиг.13 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, который определен в стандарте DVB-S.2.

На фиг.14 показана схема, которая иллюстрирует компоновку точек сигнала 16 QAM.

На фиг.15 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

На фиг.16 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

На фиг.17 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

На фиг.18 показана схема, которая иллюстрирует обработку демультиплексора 25.

На фиг.19 показана схема, которая иллюстрирует обработку демультиплексора 25.

На фиг.20 показана схема, которая иллюстрирует граф Таннера для декодирования кода LDPC.

На фиг.21 представлены схемы, которые поясняют матрицу HT четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT четности.

На фиг.22 показана схема, которая иллюстрирует матрицу HT четности матрицы Н проверки на четность, которая соответствует коду LDPC, после перемежения четности.

На фиг.23 показана схема, которая иллюстрирует преобразованную матрицу проверки на четность.

На фиг.24 показана схема, которая иллюстрирует процесс перемежителя 24 со скручиванием столбцов.

На фиг.25 показана схема, которая иллюстрирует запоминающее устройство 31 количества столбцов, которое требуется для перемежения со скручиванием столбцов, и адресов его начальных положений записи.

На фиг.26 показана схема, которая иллюстрирует запоминающее устройство 31 количества столбцов, которое требуется для перемежения со скручиванием столбцов, и адресов его начальных положений записи.

На фиг.27 показана блок-схема последовательности операций, представляющая обработку, выполняемую перемежителем 116 битов и кодером QAM 117.

На фиг.28 показана схема, которая иллюстрирует модель канала связи, используемую при моделировании.

На фиг.29 показана схема, которая иллюстрирует соотношение между коэффициентом ошибок и частотой fd Допплера дрожаний, полученное путем моделирования.

На фиг.30 показана схема, которая иллюстрирует соотношение между коэффициентом ошибок и частотой fd Допплера дрожаний, полученное путем моделирования.

На фиг.31 показана блок-схема, представляющая пример конфигурации кодера LDPC115.

На фиг.32 показана блок-схема последовательности операций, представляющая обработку кодера LDPC 115.

На фиг.33 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/4 и длину кода 16200.

На фиг.34 показана схема, которая иллюстрирует способ получения матрицы Н проверки на четность из таблицы исходного значения матрицы проверки на четность.

На фиг.35 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/4 и длину кода 4320.

На фиг.36 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/3 и длину кода 4320.

На фиг.37 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 5/12 и длину кода 4320.

На фиг.38 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/2 и длину кода 4320.

На фиг.39 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 7/12 и длину кода 4320.

На фиг.40 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 2/3 и длину кода 4320.

На фиг.41 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 3/4 и длину кода 4320.

На фиг.42 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 5/6 и длину кода 4320.

На фиг.43 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 11/12 и длину кода 4320.

На фиг.44 показана схема, которая иллюстрирует пример графа Таннера совокупности последовательности степени, имеющей вес столбца 3 и вес строки 6.

На фиг.45 показана схема, которая иллюстрирует пример графа Таннера совокупности с множеством ребер.

На фиг.46 показана схема, которая иллюстрирует минимальную длину цикла и порог возможностей матрицы проверки на четность кода LDPC, имеющего длину кода 4320.

На фиг.47 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, имеющего длину кода 4320.

На фиг.48 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, имеющего длину кода 4320.

На фиг.49 показана схема, которая иллюстрирует запоминающее устройства 31 количества столб