Физический уровень высокопроизводительного межсоединения

Иллюстрации

Показать всеГруппа изобретений относится к области компьютерной техники и может быть использована для разработки программного обеспечения, включающей координацию взаимозависимых систем с ограничениями. Техническим результатом является увеличение производительности при максимальном сбережении энергии. Устройство содержит синхронизирующий счетчик, предназначенный для локального выравнивания передачи сигналов определенным устройством с передачей сигналов в системе, содержащей одно или несколько других устройств, сопряженных, с возможностью обмена информацией, посредством межсоединения; и многоуровневый стек, содержащий логику физического уровня, логику канального уровня и логику уровня протокола, при этом логика физического уровня по меньшей мере частично выполнена в аппаратном средстве и предназначена для синхронизирования сброса синхронизирующего счетчика с некоторым внешним детерминированным сигналом, глобально поддерживаемым для системы; и синхронизирования с этим детерминированным сигналом вхождения в передающее состояние канала передачи данных на основании синхронизирующего счетчика. 4 н. и 21 з.п. ф-лы, 17 ил., 2 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее раскрываемое изобретение относится в общем к области компьютерных разработок, а более конкретно - к разработке программного обеспечения, включающей в себя координацию взаимозависимых систем с ограничениями.

Уровень техники

Успехи в обработке полупроводников и логическом проектировании позволили увеличить количество логических схем, которое может находиться на устройствах с интегральными схемами. Как следствие этого, конфигурации компьютерных систем эволюционировали от единственной или множественных интегральных схем в системе до множественных ядер, множественных аппаратных потоков обработки и множественных логических процессоров, находящихся на отдельных интегральных схемах, равно как и других интерфейсах, интегрируемых в пределах таких процессоров. Процессор или интегральная схема обычно содержат один физический кристалл процессора, причем этот кристалл процессора может включать в себя любое количество ядер, аппаратных потоков обработки, логических процессоров, интерфейсов, памяти, концентраторов-контроллеров и так далее.

В результате большей возможности вмещать больше вычислительной мощности в меньших по размеру корпусах, выросла популярность малых вычислительных устройств. Количество смартфонов, планшетных компьютеров, ультратонких ноутбуков и другого пользовательского оборудования росло по экспоненте. Однако эти меньшие по размеру устройства полагаются в отношении как хранения данных, так и сложной обработки данных, которая выходит за рамки возможностей этого форм-фактора, на серверы. Следовательно, спрос на рынке высокопроизводительных вычислений (то есть на серверное пространство) также увеличился. Например, в современных серверах обычно имеется не только одиночный процессор с множественными ядрами, но также и множественные физические процессоры (также именуемые как множественные панельки) для увеличения вычислительной мощности. Но по мере того как вместе с количеством устройств в вычислительной системе растут возможности по обработке данных, все более критически важной становится связь между панельками и другими устройствами.

В сущности, межсоединения проделали путь от более традиционных многоотводных шин, которые главным образом имели дело с электрической связью, до архитектур межсоединения, в их полном расцвете, которые облегчают быстрый обмен данными. К сожалению, поскольку от будущих процессоров требуется потреблять данные с еще более высокими скоростями, то соответствующее требование предъявляется и к возможностям существующих архитектур межсоединений.

Краткое описание чертежей

На фиг. 1 проиллюстрирована упрощенная структурная схема системы, включающая в себя двухточечное межсоединение последовательной передачи данных, подсоединяющее устройства ввода-вывода в вычислительной системе в соответствии с одним вариантом реализации изобретения.

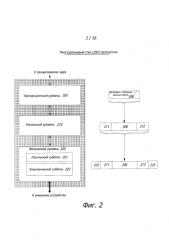

На фиг. 2 проиллюстрирована упрощенная блок-схема многоуровневого стека протоколов, соответствующего одному варианту реализации изобретения.

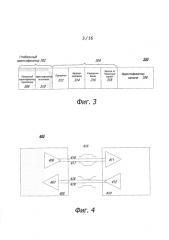

На фиг. 3 проиллюстрирован вариант реализации описателя транзакции.

На фиг. 4 проиллюстрирован вариант реализации двухточечного канала последовательной передачи данных.

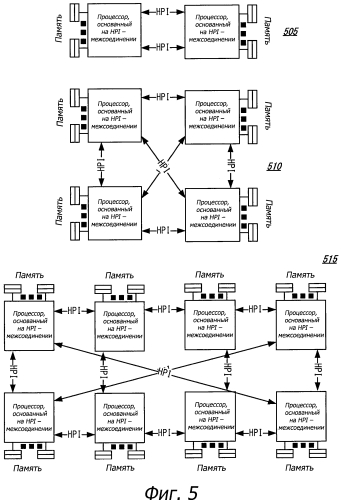

На фиг. 5 проиллюстрированы варианты реализации возможных конфигураций системы высокопроизводительных межсоединений (HΡΙ-межсоединений).

На фиг. 6 проиллюстрирован вариант реализации многоуровневого стека протоколов, связанного с HPI-межсоединением.

На фиг. 7 проиллюстрировано представление приводимого в качестве примера конечного автомата.

На фиг. 8 проиллюстрированы приводимые в качестве примера управляющие надпоследовательности.

На фиг. 9 проиллюстрирована схема последовательности операций, представляющая приводимое в качестве примера вхождение в передающее состояние с частичной шириной.

На фиг. 10 проиллюстрировано представление приводимого в качестве примера флита, отправленного по приводимому в качестве примера каналу передачи данных, имеющему двадцать путей передачи данных.

На фиг. 11 проиллюстрировано представление приводимого в качестве примера флита, отправленного по приводимому в качестве примера каналу передачи данных, имеющему восемь путей передачи данных.

На фиг. 12 проиллюстрирован вариант реализации структурной схемы для вычислительной системы, включающей в себя многоядерный процессор.

На фиг. 13 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы, включающей в себя многоядерный процессор.

На фиг. 14 проиллюстрирован вариант реализации структурной схемы для процессора.

На фиг. 15 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы, включающей в себя процессор.

На фиг. 16 проиллюстрирован вариант реализации блока для вычислительной системы, включающей в себя множественные сокеты процессоров.

На фиг. 17 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы.

Одинаковые ссылочные позиции и обозначения на различных чертежах указывают одинаковые элементы.

Подробное описание изобретения

В нижеследующем описании, в целях обеспечения глубокого понимания настоящего изобретения, приводятся многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и конфигураций системы, конкретных конструкций аппаратных средств, конкретных подробностей архитектуры и микроархитектуры, конкретных конфигураций регистров, конкретных типов команд, конкретных компонентов системы, конкретных стадий процессорного конвейера, конкретных слоев внутрисхемных соединений, конкретных конфигураций пакетов/транзакций, конкретных наименований транзакций, обменов данными по конкретным протоколам, конкретных ширин канала передачи данных, конкретных реализаций и функционирования и так далее. Однако специалисту в данной области техники может быть очевидно, что эти конкретные подробности не обязательно должны использоваться для осуществления на практике предмета настоящего раскрываемого изобретения. В других случаях, во избежание излишне затемнения сути настоящего раскрываемого изобретения, не приводится очень детализированное описание известных компонентов или способов, таких как специальные и альтернативные архитектуры процессора, конкретные логические схемы/код для описанных алгоритмов, конкретный микропрограммный код, функционирование межсоединений нижнего уровня, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные реализации компилятора, конкретное выражение алгоритмов в коде, конкретные технология/логика выключения и отпирания и другие подробности функционирования компьютерной системы.

Хотя нижеследующие варианты реализации изобретения могут быть описаны в отношении сохранения энергии, энергетической эффективности, эффективности обработки данных и так далее в специальных интегральных схемах, таких как в вычислительных платформах или микропроцессорах, другие варианты реализации изобретения применимы к другим типам интегральных схем и логических устройств. Технологии и идеи, аналогичные описанным здесь вариантам реализации изобретения, могут быть применены к другим типам схем или полупроводниковых устройств, которые также могут получить пользу от таких характеристик. Например, раскрытые варианты реализации изобретения не ограничены компьютерной системой сервера, настольными компьютерными системами, портативными компьютерами, компьютерами Ultrabooks™ (сверхтонкими "ноутбуками"), но могут также использоваться в других устройствах, таких как карманные устройства, "смартфоны", планшетные компьютеры, другие тонкие "ноутбуки", устройства "систем, встроенных в кристалл" (SOC-систем) и встраиваемые варианты применения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства, поддерживающие интернет-протокол, цифровые фотокамеры, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Здесь, технологии, аналогичные высокопроизводительному межсоединению могут быть применены для того, чтобы повысить производительность (или даже сберечь энергию) в межсоединении с низким энергопотреблением. Встроенные варианты применения обычно включают в себя микроконтроллер, процессор цифровой обработки сигналов (DSP-процессор), внутрикристальную систему, сетевые компьютеры (NetPC (сетевые персональные компьютеры)), телевизионные абонентские приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая может выполнять функции и операции, описываемые ниже. Кроме того, описываемые здесь аппараты, способы и системы не ограничены физическими вычислительными устройствами, но могут также относиться к программным оптимизациям для энергосбережения и эффективности. Как можно легко понять из приводимого ниже описания, варианты реализации способов, аппаратов и систем, описываемых здесь (будь то в отношении аппаратных средств, программно-аппаратных средств, программных средств или их сочетания), могут рассматриваться как существенно важные для будущего "зеленой технологии", сбалансированного с соображениями производительности.

По мере развития вычислительных систем компоненты этих систем становятся более сложными. Архитектура межсоединений для сопряжения компонентов и обмена данными между ними также усложняется таким образом, чтобы обеспечивать удовлетворение потребности в ширине полосы пропускания для оптимального функционирования компонентов. Кроме того, различным сегментам рынка требуются, для удовлетворения соответствующего рынка, различные аспекты архитектуры межсоединений. Например, серверам требуется более высокая производительность, в то время как в экосистеме мобильных устройств иногда можно пожертвовать общей производительностью ради сбережения энергии. Тем не менее, единая цель большинства структур заключается в том, чтобы обеспечить максимально возможную производительность при максимальном сбережении энергии. Кроме того, описываемый здесь предмет изобретения может потенциально принести пользу большому разнообразию различных межсоединений.

В соответствии с одним или более принципами, описываемыми здесь среди других примеров, потенциально может быть усовершенствована, среди других примеров, архитектура структуры межсоединения PCIe (Скоростное межсоединение PCI (межсоединение периферийных компонентов)) и архитектура структуры межсоединения QuickPath (межсоединением QPI (Межсоединением тракта быстрой передачи данных)). Например, основная цель межсоединения PCIe заключается в том, чтобы позволить компонентам и устройствам от различных поставщиков взаимодействовать в открытой архитектуре, охватывая множественные сегменты рынка; клиентов (настольные компьютеры и мобильные устройства), серверы (стандартные серверы и серверы предприятий) и встроенные устройства и устройства связи. Межсоединение PCI Express (Скоростное межсоединение периферийных компонентов) представляет собой высокопроизводительное межсоединение ввода-вывода общего назначения, определенное для широкого круга будущих платформ вычисления и связи. Некоторые атрибуты межсоединения PCI, такие как его модели использования, архитектура загрузки - хранения и программируемые интерфейсы, были сохранены при пересмотрах этого стандарта, тогда как существовавшие ранее реализации параллельной шины были заменены значительно расширяемым полностью последовательным интерфейсом. Более свежие версии межсоединения PCI Express используют достижения в области двухточечных межсоединений, технологии на основе переключателя, и пакетизированный протокол для того, чтобы предоставить новые уровни производительности и функциональных возможностей. Среди некоторых из усовершенствованных функциональных возможностей, поддерживаемых межсоединением PCI Express имеются: администрирование энергопотребления, качество обслуживания (QoS), поддержка Hot-Plug/Hot-Swap (подключения устройств без выключения системы/смены устройств без выключения системы), обеспечение целостности данных и обработка ошибок. Хотя основное обсуждение в данном описании относится к новой архитектуре высокопроизводительного межсоединения (HPI-межсоединения), аспекты описываемого здесь изобретения могут быть применены к другим архитектурам межсоединений, таким как PCIe - совместимой архитектуре, QPI - совместимой архитектуре, MIPI - совместимой архитектуре, высокопроизводительной архитектуре или другой известной архитектуре межсоединения.

Обратимся к фиг. 1, на которой проиллюстрирован вариант реализации структуры, составленной из двухточечных каналов передачи данных, которые соединяют между собой некоторый набор компонентов. Система (100) включает в себя процессор (105) и системную память (110), сопряженные с концентратором-контроллером (115). Процессор (105) может включать в себя любой процессорный элемент, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или другой процессор. Процессор (105) сопряжен с концентратором-контроллером (115) через управляющую шину (FSB-шину) (106). В одном варианте реализации изобретения FSB-шина (106) представляет собой двухточечное межсоединение последовательной передачи данных, которое описывается ниже. В другом варианте реализации изобретения канал (106) передачи данных включает в себя последовательную, дифференциальную архитектуру межсоединения, которая совместима со стандартом дифференциального межсоединения.

Системная память (110) включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (RAM), энергонезависимое (NV) запоминающее устройство или другое запоминающее устройство, доступное для устройств в системе (100). Системная память (110) сопряжена с концентратором-контроллером (115) через интерфейс (116) памяти. Примеры интерфейса памяти включают в себя интерфейс (DDR) памяти с удвоенной скоростью передачи данных, двухканальный интерфейс памяти с удвоенной скоростью передачи данных и интерфейс памяти динамического оперативного запоминающего устройства (DRAM).

В одном варианте реализации изобретения концентратор-контроллер (115) может включать в себя корневой концентратор, корневой комплекс или корневой контроллер, такие как в иерархии межсоединения PCIe. Примеры концентратора-контроллера (115) включают в себя набор микросхем, концентратор-контроллер (МСН) памяти, "северный мост", концентратор-контроллер (ICH) межсоединения, "южный мост" и корневой концентратор-контроллер. Часто термин "набор микросхем" относится к двум физически отдельным концентраторам-контроллерам, например, к концентратору-контроллеру (МСН) памяти, сопряженному с концентратором-контроллером (ICH) межсоединения. Отметим, что имеющиеся в настоящее время системы часто включают в себя концентратор-контроллер (МСН) памяти, интегрированный с процессором (105), в то время как контроллер (115) должен поддерживать связь с устройствами ввода-вывода способом, аналогичным тому, что описан ниже. В некоторых вариантах реализации изобретения, посредством корневого комплекса (115) дополнительно поддерживается одноранговая маршрутизация.

Здесь, концентратор-контроллер (115) сопряжен с переключателем/мостом (120) через канал (119) последовательной передачи данных. Модули (117) и (121) ввода/вывода, которые могут также упоминаться как интерфейсы/порты (117) и (121), могут включать в себя/реализовывать многоуровневый стек протоколов для обеспечения связи между концентратором-контроллером (115) и переключателем (120). В одном варианте реализации изобретения, с переключателем (120) способны сопрягаться множественные устройства.

Переключатель/мост (120) осуществляет маршрутизацию пакетов/сообщений от устройства (125) по восходящему потоку (данных), то есть вверх по иерархии по направлению к корневому комплексу, к концентратору-контроллеру (115), и по нисходящему потоку (данных), то есть вниз по иерархии в направлении от корневого контроллера, от процессора (105) или системной памяти (110) к устройству (125). Переключатель (120), в одном варианте реализации изобретения, упоминается как логический узел множественных виртуальных мостовых устройств "PCI-c-PCI". Устройство (125) включает в себя любое внутреннее или внешнее устройство или компонент, подлежащий сопряжению с электронной системой, такое как устройство ввода/вывода, сетевой интерфейсный контроллер (NIC-контроллер), расширительная плата, процессор обработки звукового сигнала, сетевой процессор, накопитель на жестких магнитных дисках, запоминающее устройство, CD/DVD ROM (постоянное запоминающее устройство на компакт-дисках/универсальных цифровых дисках), монитор, принтер, "мышь", клавиатура, маршрутизатор, портативное запоминающее устройство, устройство Firewire, устройство с универсальной последовательной шиной (USB-шиной), сканер и другие устройства ввода/вывода. Часто в терминологии стандарта PCIe, такого рода устройство упоминается как "конечная точка". Устройство (125) может включать в себя, хотя это особо и не показано, мост (например, мост от PCIe к PCI/PCI - X) для поддержания преемственности или других версий устройств или структур межсоединения, поддерживаемых такими устройствами.

С концентратором-контроллером (115) через канал (132) последовательной передачи данных может также быть сопряжен графический ускоритель (130). В одном варианте реализации изобретения, графический ускоритель (130) сопряжен с концентратором-контроллером (МСН) памяти, который сопряжен с концентратором-контроллером (ICH) межсоединения. Переключатель (120), и, соответственно устройство ввода/вывода (125), в таком случае сопрягаются с концентратором-контроллером (ЮН) межсоединения. Модули ввода-вывода (131) и (118) должны также реализовывать многоуровневый стек протоколов для поддержания связи между графическим ускорителем (130) и концентратором-контроллером (115). Аналогично тому, что было сказано выше в отношении концентратора - контроллера (МСН) памяти, сам графический контроллер или графический ускоритель (130) может быть интегрирован в процессор (105).

Обратимся к фиг. 2, на которой проиллюстрирован вариант реализации многоуровневого стека протоколов. Многоуровневый стек (200) протоколов может включать в себя любую форму многоуровневого стека протоколов связи, такую как стек QPI, стек PCIe, стек для межсоединения следующего поколения для высокопроизводительного вычисления (HPI-стек) или другой многоуровневый стек. В одном варианте реализации изобретения, стек (200) протоколов может включать в себя транзакционный уровень (205), канальный уровень (210) и физический уровень (220). Интерфейс, такой как интерфейсы (117), (118), (121), (122), (126) и (131), показанные на фиг. 1, могут быть представлены как стек (200) протоколов связи. Представление в виде стека протоколов связи может также упоминаться как модуль или интерфейс, реализующий/включающий в себя стек протоколов.

Для обмена информацией между компонентами могут использоваться пакеты. Пакеты могут быть сформированы на транзакционном уровне (205) и уровне (210) канала передачи данных для того, чтобы переносить информацию от передающего компонента к принимающему компоненту. Поскольку передаваемые пакеты проходят через другие уровни, то они дополняются дополнительной информацией, используемой для обработки пакетов на этих уровнях. На стороне приема происходит обратный процесс, и пакеты преобразуются из их представления физического уровня (220) в представление уровня канала передачи данных и, наконец (для пакетов транзакционного уровня), в форму, которая может быть обработана на транзакционном уровне (205) принимающего устройства.

В одном варианте реализации изобретения, транзакционный уровень (205) может обеспечивать интерфейс между ядром обработки данных в устройстве и архитектурой межсоединения, такой как уровень (210) канала передачи данных и физический уровень (220). Отметим в этой связи, что основная обязанность транзакционного уровня (205) может включать в себя сборку и разборку пакетов (то есть пакетов транзакционного уровня или TLP-пакетов). Трансляционный уровень (205) может также администрировать управление потоками для TLP-пакетов, основанное на "кредитах" (разрешениях на передачу некоторого количества данных). В некоторых вариантах осуществления изобретения могут, среди других примеров, использоваться "разделенные" транзакции, то есть транзакции с запросом и ответом, разделенными временем, что позволяет каналу передачи данных передавать другой трафик в то время, пока целевое устройство собирает данные для ответа.

Управление потоками, основанное на "кредитах", может быть использовано для того, чтобы реализовывать виртуальные каналы и сети, использующие эту структуру межсоединения. В одном примере, устройство может объявлять некоторое начальное количество "кредитов" для каждого из приемных буферов на транзакционном уровне (205). Внешнее устройство на противоположном конце канала передачи данных, такое как концентратор-контроллер (115), показанный на фиг. 1, может подсчитывать количество "кредитов", потребляемое каждым TLP-пакетом. Транзакция может быть передана в том случае, если транзакция не превышает предел "кредитов". После получения ответа количество "кредита" восстанавливается. Один пример преимущества, среди других потенциальных преимуществ, такой схемы с "кредитами" заключается в том, что время задержки возвращения "кредита" не влияет на производительность при том условии, что предел "кредитов" не нарушен.

В одном варианте реализации изобретения, четыре транзакционных адресных пространства могут включать в себя адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщений. Транзакции пространства памяти включают в себя один или более запросов чтения и запросов записи для передачи данных в отображенные в памяти места. В одном варианте реализации изобретения, транзакции пространства памяти способны использовать два различных формата адреса, например, короткий формат адреса, такой как 32-разрядный адрес, или длинный формат адреса, такой как 64-разрядный адрес. Транзакции пространства конфигурации могут быть использованы для того, чтобы получать доступ к пространству конфигурации различных устройств, подсоединяемых к межсоединению. Транзакции в отношении пространства конфигурации могут включать в себя запросы чтения и запросы записи. Транзакции пространства сообщений (или просто сообщения) могут также быть определены таким образом, чтобы поддерживать внутриполосную связь между агентами межсоединения. Следовательно, в одном приводимом в качестве примера варианте реализации, транзакционный уровень (205) может осуществлять сборку заголовка/полезных данных (206) пакета.

Быстро рассмотрим фиг. 3, на которой проиллюстрирован приводимый в качестве примера вариант реализации дескриптора пакета транзакционного уровня. В одном варианте реализации изобретения, дескриптор (300) транзакции может представлять собой механизм для передачи информации о транзакции. В этом отношении отметим, что дескриптор (300) транзакции поддерживает идентификацию транзакций в системе. Другие потенциальные варианты использования включают в себя отслеживание изменений упорядочивания транзакции по умолчанию и ассоциативную привязку транзакции к каналам. Например, дескриптор (300) транзакции может включать в себя поле (302) глобального идентификатора, поле (304) атрибутов и поле (306) идентификатора канала. В проиллюстрированном примере поле (302) глобального идентификатора изображено содержащим поле (308) локального идентификатора транзакции и поле (310) идентификатора источника. В одном варианте реализации изобретения, глобальный идентификатор (302) транзакции является уникальным для всех невыполненных запросов.

В соответствии с одним вариантом осуществления изобретения, поле (308) локального идентификатора транзакции представляет собой поле, сгенерированное запрашивающим агентом, и может быть уникальным для всех невыполненных запросов, которые требуют своего завершения для этого запрашивающего агента. Кроме того, в этом примере, идентификатор (310) источника уникальным образом определяет запрашивающего агента в пределах иерархии межсоединений. Соответственно, вместе с идентификатором (310) источника, поле (308) локального идентификатора транзакции обеспечивают глобальную идентификацию транзакции в пределах домена иерархии.

Поле (304) атрибутов определяет характеристики и связи транзакции. В этом отношении отметим, что поле (304) атрибутов потенциально используется для того, чтобы предоставлять дополнительную информацию, которая позволяет изменять обработку транзакций по умолчанию. В одном варианте реализации изобретения, поле (304) атрибутов включает в себя поле (312) приоритета, зарезервированное поле (314), поле (316) упорядочивания и поле (318) защиты от "прослушивания". Здесь, подполе (312) приоритета может быть изменено инициатором для задания приоритета транзакции. Зарезервированное поле (314) атрибутов оставлено зарезервированным для будущего использования или использования, определенного поставщиком оборудования. С использованием зарезервированного поля (314) атрибутов могут быть воплощены возможные модели использования, использующие приоритет или атрибуты секретности.

В этом примере, поле (316) атрибута упорядочивания используется для предоставления дополнительной информации, сообщающей тип упорядочивания, который может изменять правила упорядочивания по умолчанию. В соответствии с одним примером варианта осуществления изобретения, атрибут упорядочивания, составляющий "0", означает то, что должны быть применены правила упорядочивания по умолчанию, тогда как атрибут упорядочивания, составляющий "1", означает смягченное упорядочивание, при котором записи могут обгонять записи в том же самом направлении, а завершения чтения могут обгонять записи в том же самом направлении. Поле (318) атрибута "прослушивания" используется для определения того, не "прослушиваются" ли транзакции. Как показано на фигуре, поле (306) идентификатора канала идентифицирует канал, с которым связана транзакция.

Возвращаясь к обсуждению фиг. 2, отметим, что канальный уровень (210), также именуемый как уровень (210) канала передачи данных, может действовать в качестве промежуточной стадии между транзакционным уровнем (205) и физическим уровнем (220). В одном варианте реализации изобретения, обязанность уровня (210) канала передачи данных заключается в обеспечении надежного механизма для обмена пакетами транзакционного уровня (TLP-пакетами) между двумя компонентами по каналу передачи данных. Одна сторона уровня (210) канала передачи данных принимает TLP-пакеты, собранные на транзакционном уровне (205), применяет идентификатор (211) последовательности пакетов, то есть идентификационный номер или номер пакета, вычисляет и применяет код обнаружения ошибок, то есть циклический избыточный код (212), и представляет измененные TLP-пакеты на физический уровень (220) для передачи на физическом уровне внешнему устройству.

В одном примере, физический уровень (220) включает в себя логический субблок (221) и электрический субблок (222) для физической передачи пакета на внешнее устройство. Здесь, логический субблок (221) ответствен за "цифровые" функции физического уровня (221). В этом отношении отметим, что логический субблок может включать в себя секцию передатчика, предназначенную для подготовки исходящей информации к передаче физическим субблоком (222), и секцию приемника, предназначенную для идентификации и подготовки принятой информации перед передачей ее на канальный уровень (210).

Физический блок (222) включает в себя передатчик и приемник. Логический субблок (221) снабжает передатчик символами, которые трансмиттер преобразовывает в последовательную форму и передает на внешнее устройство. Приемник снабжается преобразованными в последовательную форму символами, поступающими от внешнего устройства, и преобразовывает принятые сигналы в поток битов. Поток битов преобразуется из последовательной формы в параллельную и подается на логический субблок (221). В одном приводимом в качестве примера варианте реализации изобретения используется код передачи 8 битов/10 битов, при котором передаются/принимаются десятибитовые символы. При этом для того чтобы кадрировать пакет кадрами (223) используются специальные символы. В дополнение к этому, в одном примере приемник также обеспечивает синхронизацию символа, восстанавливаемую из поступающего последовательного потока данных.

Как было сказано выше, хотя в отношении конкретного варианта реализации стека протоколов (такого как стек протоколов стандарта PCIe) рассмотрены транзакционный уровень (205), канальный уровень (210) и физический уровень (220), многоуровневый стек (200) протоколов этим не ограничен. Фактически, любой многоуровневый протокол может быть включен сюда/реализован и наделен обсуждаемыми здесь признаками. В качестве примера, порт/интерфейс, который представлен как многоуровневый протокол, может включать в себя: (1) первый уровень для сборки пакетов, то есть транзакционный уровень; второй уровень для создания последовательности пакетов, то есть канальный уровень; и третий уровень для передачи пакетов, то есть физический уровень. В качестве конкретного примера используется многоуровневый протокол высокопроизводительного межсоединения, который описан в данном описании.

Обратимся далее к фиг. 4, на которой проиллюстрирован приводимый в качестве примера вариант реализации структуры двухточечного канала последовательной передачи данных. Двухточечный канал последовательной передачи данных может включать в себя любой тракт передачи данных, предназначенный для передачи последовательно передаваемых данных. В показанном варианте реализации изобретения, канал передачи данных может включать в себя две сигнальные пары низкого напряжения с дифференциальным возбуждением: передающую пару (406)/(411) и принимающую пару (412)/(407). Соответственно, устройство (405) включает в себя передающую логическую схему (406) для передачи данных на устройство (410) и принимающую логическую схему (407) для приема данных от устройства (410). Другими словами, в состав некоторых вариантов осуществления канала передачи данных входят два передающих тракта, то есть тракты (416) и (417), и два принимающих тракта, то есть тракты (418) и (419).

Термин "тракт передачи данных" относится к любому тракту для передачи данных, такому как линия передачи данных, медная линия, оптическая линия, канал беспроводной связи, канал связи в инфракрасном диапазоне или другой тракт связи. Соединение между двумя устройствами, такими как устройство (405) и устройство (410), именуется как канал передачи данных, такой как канал (415) передачи данных. Канал передачи данных может поддерживать один путь передачи данных - каждый путь передачи данных представляет набор дифференциальных сигнальных пар (одна пара для передачи, одна пара для приема). Для масштабирования ширины полосы пропускания канал передачи данных может объединять множественные пути передачи данных, обозначаемые как xN, где N представляет собой любую поддерживаемую ширину канала передачи данных, такую как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальная пара может относиться к двум трактам передачи данных, таким как линии (416) и (417), для передачи разностных сигналов. В качестве примера, когда линия (416) переключается с низкого уровня напряжения на высокий уровень напряжения, то есть при нарастающем фронте, линия (417) переводится с высокого логического уровня на низкий логический уровень, то есть на падающий фронт. Разностные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, то есть перекрестное взаимодействие, "выброс" напряжения вверх/вниз, "звон", среди других приводимых в качестве примера преимуществ. Это делает возможным лучшее окно синхронизации, которое делает возможным более высокие частоты передачи.

В одном варианте реализации изобретения предлагается новое высокопроизводительное межсоединение (HPI-межсоединение). HPI-межсоединение может включать в себя кэш-когерентное основанное на канале передачи данных межсоединение следующего поколения. В качестве одного примера, HPI-межсоединение может быть использовано на высокопроизводительных вычислительных платформах, таких как рабочие станции или серверы, включая сюда системы, где для соединения процессоров, ускорителей, устройств ввода/вывода и тому подобного обычно используются протокол PCIe (Скоростного межсоединения периферийных компонентов) или другой протокол межсоединения. Однако HPI-межсоединение этим не ограничено. Вместо этого, HPI-межсоединение может быть использовано в любой из описываемых здесь систем или платформ. Кроме того, отдельные разработанные идеи могут быть применены к другим межсоединениям и платформам, таким как PCIe, MIPI, QPI и так далее.

Для поддержания множественных устройств, в одном приводимом в качестве примера варианте осуществления изобретения, HPI-межсоединение может включать в себя агностика архитектуры набора команд (то есть HPI-межсоединение может быть реализовано во множественных различных устройствах). В другом сценарии HPI-межсоединение может также быть использовано для подсоединения высокопроизводительных устройств ввода/вывода, а не только процессоров или ускорителей. Например, высокопроизводительное устройство стандарта PCIe может быть подсоединено к HPI-межсоединению через соответствующий мост преобразования (то есть из HPI в PCIe). Кроме того, каналы передачи данных HPI-межсоединения могут быть использованы многими устройствами, основанными на HPI-межсоединении, такими как процессорами, различными способами (например, звездами, кольцами, многоугольниками и так далее). На фиг. 5 проиллюстрированы приводимые в качестве примера варианты осуществления множественных потенциальных многосокетных конфигураций. Двухсокетная конфигурация (505), как изображено на фигуре, может включать в себя два HPI-канала передачи данных (канала передачи данных по HPI-межсоединению); однако в других вариантах осуществления изобретения может использоваться один HPI-канал передачи данных. Для более крупных топологий может быть использована любая конфигурация до тех пор, пока может быть присвоен идентификатор (ID) и есть некоторая форма виртуального тракта, среди других дополнительных признаков или заменяющих признаков. Как показано на фигуре, в одном примере, четырехсокетная конфигурация (510) имеет HPI-канал передачи данных, идущий от каждого процессора к другому. Но на восьмисокетном варианте осуществления изобретения, который показан на конфигурации (515), не каждый сокет напрямую соединен друг с другом через HPI-канал передачи данных. Однако если между процессорами существует некоторый виртуальный тракт или канал, то эта конфигурация поддерживается. Диапазон поддерживаемых процессоров включает в себя 2-32 в собственном домене. Более высокие количества процессоров могут быть достигнуты, среди других примеров, посредством использования множественных доменов или других межсоединений между контроллерами узлов.

Архитектура HPI-межсоединения включает в себя определение многоуровневую архитектуру протоколов, включающую в себя, в некоторых примерах, уровни протоколов (когерентный, некогерентный и, по желанию, другие основанные на памяти протоколы), уровень маршрутизации, канальный уровень и физический уровень. Кроме того, HPI-межсоединение может, среди других примеров, дополнительно включать в себя расширения, связанные с администраторами энергопотребления (такими как звенья управления энергопотреблением (PCU-звенья)), конструкцией для тестирования и отладки (DFT-конструкцией), устранением неисправностей, регистрами, безопасностью. На фиг. 5 проиллюстрирован вариант реализации приводимого в качестве примера многоуровневого стека протоколов HPI-межсоединения. В некоторых вариантах осуществления изобретения, по меньшей мере, некоторые из уровней, проиллюстрированных на фиг. 5, могут быть необязательными. Каждый уровень имеет дело со своим собственным уровнем гранулярности или кв