Адаптивный интеллектуальный логический регулятор, работающий в условиях нечетко заданной информации

Иллюстрации

Показать всеИзобретение относится к области управления сложными объектами, которые не удается представить математической моделью в виде систем линейных дифференциальных уравнений, и быстродействующими технологическими процессами и касается нефтехимической, машиностроительной и нефтеперерабатывающей промышленностей. Технический результат - повышение быстродействия и точности управления. Адаптивный интеллектуальный логический регулятор, работающий в условиях нечетко заданной информации, состоит из фаззификатора, блока логического вывода, дефаззификатора, исполнительного органа, объекта управления, датчика обратной связи, ПИД-регулятора, сумматора, блока базы правил подстройки коэффициентов ПИД-регулятора, блока адаптации коэффициентов ПИД-регулятора и блока идентификации технологического процесса. 3 ил.

Реферат

Изобретение относится к области управления сложными объектами, которые не удается представить математической моделью в виде систем линейных дифференциальных уравнений, и быстродействующими технологическими процессами и касается нефтехимической, машиностроительной и нефтеперерабатывающей промышленностей.

Известны пропорционально-интегрально-дифференциальные (ПИД) регуляторы. Например, ПИД-регулятор, состоящий из блока сравнения, пропорционального блока, интегратора, дифференциатора, сигналы которых идут на вход сумматора, являющегося выходом ПИД-регулятора (Патент РФ №2234116, кл. G05B 11/36. Пропорционально-интегрально-дифференциальный регулятор, 2002).

К недостаткам данного ПИД-регулятора можно отнести то, что сигнал регулируемой величины находится в сильной взаимозависимости от возмущений параметров на входе объекта, что приводит к снижению качества регулирования и неустойчивой работе всей системы.

Известны также пропорционально-интегрально-дифференциальные регуляторы: ПИД-регулятор, содержащий последовательно соединенные блок сравнения, блок умножения, пропорциональный блок, сумматор, а также блок выделения модуля, дифференциатор и интегратор, подключенные к выходу блока сравнения, а выходом связанные соответственно с блоком умножения и сумматором, выход которого является выходом регулятора (Голант А.И., Альперович Л.С, Васин В.М. Системы цифрового управления в химической промышленности. М., Химия, 1985, с. 60).

Недостатками данного регулятора являются: низкая чувствительность коэффициента усиления системы к малым отклонениям регулируемой величины, усложнение конструкции регулятора и ограничение увеличения выходного сигнала с выхода дифференциатора из-за наличия дополнительных сумматоров, ограничителей, пропорциональных блоков, дифференциаторов, блоков умножения и нелинейных блоков с зонами нечувствительности, а также возможность потери устойчивости системы при больших изменениях параметров.

Управление сложными технологическими процессами возможно на основе регуляторов с нечеткой логикой (Патент JP №3110442, кл. G05D 23/13, опубл. в 2000 г.), включающий сравнивающее устройство, блок интегрирования и дифференцирования, фаззификатор, блок нечеткого логического вывода, дефаззификатор, исполнительный орган, объект управления и датчик обратной связи.

К недостаткам регуляторов с нечеткой логикой можно отнести: повышенное время отклика, значительная погрешность в управлении и, вследствие этого, низкая точность управления в масштабе времени технологического процесса.

Наиболее близким к заявленному техническому решению (прототип) является четкий логический регулятор для управления технологическими процессами (Каяшев А.И., Муравьева Е.А., Габитов Р.Ф. Патент РФ №2445669, кл. G05B 13/02, 2010).

Основными недостатками прототипа являются: разработчик (эксперт) четкого логического регулятора должен располагать методикой настройки продукционных правил и исключительным опытом работы технологического процесса (невозможность получения экспертной настройки четкого регулятора при возмущениях на входе и на выходе объекта управления может в значительной мере снизить качество регулирования и область устойчивой работы регулятора), увеличение стоимости управляющей системы в связи с расширенными интеллектуальными свойствами регулятора.

Задачей изобретения является повышение чувствительности работы ПИД-регулятора к изменению параметров управляемого объекта благодаря использованию четкой логики, снижение стоимости и трудоемкости выполняемых процессов настройки регуляторов для быстродействующих и не требовательных к заданному циклу управления технологических процессов.

Поставленная задача решается способом интеллектуальной адаптации логического регулятора в условиях нечетко заданной информации. Структура предлагаемого регулятора состоит из фаззификатора, блока логического вывода, дефаззификатора, исполнительного органа, объекта управления, датчика обратной связи, ПИД-регулятора, сумматора, блока базы правил подстройки коэффициентов ПИД-регулятора (в дальнейшем блок базы правил), выходы которого соединены с фаззификатором, дефаззификатором и блоком логического вывода, имеющим прямую и обратную связь с блоком базы правил, и дополнительно включает блок адаптации коэффициентов ПИД-регулятора, а также блок идентификации технологического процесса, соединенных таким образом, что первый вход фаззификатора соединен с выходом исполнительного органа, второй вход фаззификатора соединен с выходом датчика обратной связи, а выход фаззификатора соединен с входом блока логического вывода, выход блока логического вывода соединен с входом дефаззификатора и выходом блока базы правил, выход дефаззификатора соединен с входом блока адаптации коэффициентов ПИД-регулятора, выход которого соединен с ПИД-регулятором, выход ПИД-регулятора соединен с входом исполнительного органа, выход которого соединен с входом объекта управления, выход объекта управления соединен с входом датчика обратной связи, при этом выходные дискретные параметры объекта управления подаются на сумматор, а также на вход блока идентификации технологического процесса, а выход объекта управления соединен с входом блока идентификации технологического процесса, по линии связи передаются входные дискретные параметры объекта управления, а выход блока идентификации технологического процесса соединен с входом блока базы правил для подстройки коэффициентов ПИД-регулятора путем внесения корректировок в базу правил его коэффициентов.

Согласно изобретению для расширения управляющих свойств логического регулятора дискретные входные (X) и выходные (Y) переменные от объекта управления соединены с дополнительными входами блока логического вывода, число которых равно общему количеству переменных X и Y, а для снижения времени отклика, уменьшения погрешности регулирования и совместного использования в антецедентах продукционных правил термов дискретных входных и выходных переменных объекта управления с термами регулирующих и регулируемых параметров регулятора с целью расширения его управляющих свойств, регулирующие и регулируемые параметры представлены совокупностью четких термов (их функция принадлежности имеет прямоугольную форму).

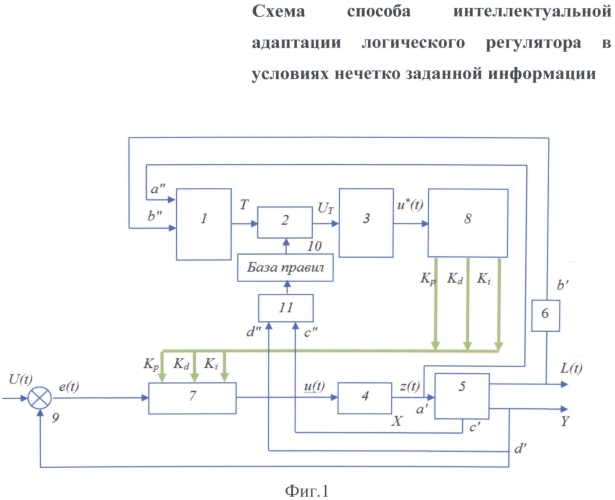

На фиг. 1 изображена структурная схема предлагаемого способа интеллектуальной адаптации логического регулятора в условиях нечетко заданной информации.

На фиг. 2 представлены функции принадлежности четких термов L1, L2, L3, L4 … L10 регулируемой переменной L(t).

На фиг. 3 представлена система продукционных правил блока логического вывода.

Схема предлагаемого способа интеллектуальной адаптации логического регулятора в условиях нечетко заданной информации на фиг. 1 для управления технологическими процессами, в котором входные и выходные переменные представлены совокупностью четких термов, т.е. таких термов, функция принадлежности которых равна единице на заданном отрезке универсальной числовой оси и равна нулю на всех остальных участках этой оси, содержит: фаззификатор 1, блок логического вывода 2, дефаззификатор 3, исполнительный орган 4, объект управления 5, датчик обратной связи 6, ПИД-регулятор 7, блок адаптации коэффициентов ПИД-регулятора 8, сумматор 9, блок базы правил 10, а также блок идентификации технологического процесса 11.

Для параметров на фиг. 1 введены следующие обозначения: U(t) - значение задания, e(t) - ошибка регулирования, ∫e(t)/dt - интеграл ошибки регулирования, e(t)/dt - производная ошибки регулирования, u*(t) - текущее значение параметра на выходе дефаззификатора 3, u(t) - текущее значение регулирующего параметра на выходе ПИД-регулятора 7, z(t) - усиленное текущее значение регулирующего параметра на выходе исполнительного органа 4, L(t) - текущее значение регулируемого параметра, Т - вектор четких термов регулируемого L(t) и регулирующего z(t) параметров, UT - вектор термов на выходе блока логического вывода 2, X - вектор входных дискретных параметров объекта управления 5, Y - вектор выходных дискретных параметров объекта управления 5.

Выход ПИД-регулятора 7 соединен с входом исполнительного органа 4 (по линии связи u(t)), выход которого соединен с входом объекта управления 5 (по линии связи z(t)), выход объекта управления 5 соединен с входом датчика обратной связи 6 (по линии связи b′-b″), при этом выходные дискретные параметры объекта управления 5 подаются на сумматор 9, а также на вход блока идентификации технологического процесса 11 (по линии связи d′-d″), а выход объекта управления 5 соединен с входом блока идентификации технологического процесса 11, по линии связи (с′-с″) передаются входные дискретные параметры объекта управления 5, а выход блока идентификации технологического процесса 11 соединен с входом блока базы правил 10 для подстройки коэффициентов ПИД-регулятора 7 путем внесения корректировок в блок базы правил 10 его коэффициентов.

На фиг. 2 представлены функции принадлежности четких термов L1, L2, L3, L4 … L10 регулируемой переменной L(t), которые равны логической единице на отрезках 0≤L(t)<L1, L1≤L(t)<L2, L2≤L(t)<L3, L3≤L(t)<L4, L4≤L(t)<L5 соответственно универсальной числовой оси L. Функции принадлежности переменных L(t) и z(t) хранятся в блоке базы правил 10 нечеткого логического регулятора.

Логический регулятор, в котором входные и выходные переменные представлены совокупностью четких термов, для управления технологическими процессами функционирует следующим образом.

На входах а″ и b″ фаззификатора 1 устанавливается четкое значение величины сигналов, идентифицирующих следующие фиксированные значения L1, L2, L3, L4 … L10 регулируемой переменной L(t). При этом предполагается, что текущее значение регулируемой величины находится в пределах допустимых значений.

Микропроцессор с заданной периодичностью непрерывно сканирует систему правил (фиг. 3). В зависимости от текущего значения регулируемой величины L(t) фаззификатор 1 преобразует его в один из термов лингвистической переменной L. Например, если значение регулируемой величины L(t) находится в диапазоне 0≤L(t)<L1, то его четкое значение преобразуется в терм Т1. Если L1≤L(t)<L2, то L(t) преобразуется в терм Т2. Аналогично, при условии L2≤L(t)<L3 L(t) преобразуется в терм Т3, при L3≤L(t)<L4 - в терм Т4, а при L4≤L(t)<L5 - в терм Т5 и т.д.

Таким образом, в любой момент времени с выхода фаззификатора 1 на вход блока логического вывода 2 поступает один терм регулируемой величины L(t). Поскольку в этой системе в любой момент времени условная часть истинна только в одном продукционном правиле и ложна во всех остальных правилах этой системы, то в каждом цикле сканирования системы нечетких правил обрабатывается не вся система (это имеет место в известных нечетких регуляторах), а только та ее часть, которая в системе (фиг. 3) расположена выше сработавшего в текущем цикле сканирования продукционного правила.

Если в системе (фиг. 3) сработало первое продукционное правило, например регулируемая переменная находится в интервале 0≤L(t)<L1 универсальной числовой оси на фиг. 2, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму T1.

Если в системе (фиг. 3) сработало второе продукционное правило, то текущее значение регулируемой переменной находится в интервале L1≤L(t)<L2 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т2.

Если в системе (фиг. 3) сработало третье продукционное правило, то текущее значение регулируемой переменной находится в интервале L2≤L(t)<L3 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т3.

Если в системе (фиг. 3) сработало четвертое продукционное правило, то текущее значение регулируемой переменной находится в интервале L3≤L(t)<L4 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т4.

Если в системе (фиг. 3) сработало пятое продукционное правило, то текущее значение регулируемой переменной находится в интервале L4≤L(t)<L5 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму T5.

Если в системе (фиг. 3) сработало шестое продукционное правило, то текущее значение регулируемой переменной находится в интервале L5≤L(t)<L6 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т6.

Если в системе (фиг. 3) сработало седьмое продукционное правило, то текущее значение регулируемой переменной находится в интервале L6≤L(t)<L7 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т7.

Если в системе (фиг. 3) сработало восьмое продукционное правило, то текущее значение регулируемой переменной находится в интервале L7≤L(t)<L8 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму T8.

Если в системе (фиг. 3) сработало девятое продукционное правило, то текущее значение регулируемой переменной находится в интервале L8≤L(t)<L9 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т9.

Если в системе (фиг. 3) сработало десятое продукционное правило, то текущее значение регулируемой переменной находится в интервале L9≤L(t)<L10 универсальной оси, то с выхода блока адаптации коэффициентов ПИД-регулятора 8 на ПИД-регулятор 7 подаются значения коэффициентов согласно текущему терму Т10.

В случае выхода значения регулируемого параметра L(t) за пределы отрезков (0÷L10) универсальной оси управление передается блоку 10 для отработки аварийных ситуаций, который выставляет сообщение об аварии, обнуляет значение регулируемого параметра L(t) и блокирует сканирование системы продукционных правил (фиг. 3).

В блоке логического вывода 2 происходит непрерывное сканирование системы правил (фиг. 3). Из-за использования в системе (фиг. 3) четких термов в любой момент времени имеется только одно правило с истинной условной частью. Поэтому система (фиг. 3) без потери адекватности управления сканируется не полностью, а только до продукционного правила с истинной условной частью, после чего микропроцессор переходит к отработке следующего цикла сканирования. Это приводит к снижению времени отклика предлагаемого нечеткого регулятора. Причем этот эффект проявится в большей степени, если продукционные правила с наибольшей частотой срабатывания поместить в начало системы правил (фиг. 3).

Таким образом, в результате непрерывного сканирования системы (фиг. 3) и вследствие того, что в ней в любой момент времени имеется только одно продукционное правило, условная часть которого истинна, в предлагаемом способе интеллектуальной адаптации логического регулятора в условиях нечетко заданной информации значение регулируемой величины L(t) с высоким быстродействием поддерживается около номинального уровня.

Интеллектуальная адаптация логического регулятора в условиях нечетко заданной информации, представление которой в операционной среде предложенного логического регулятора осуществляется в виде четких термов, аналогично представлению информации совокупностью аргументов двузначной логики позволяет существенно повысить точность регулирования по сравнению с известными нечеткими регуляторами. В известных нечетких регуляторах и ПИД-регуляторах снижение точности является следствием следующих причин:

- в известных нечетких регуляторах на вход дефаззификатора 1 поступает терм регулируемой переменной со сложной формой функции принадлежности (например, треугольник, усеченный конус или пирамида и др.);

- с увеличением факторов, влияющих на регулируемую переменную, возрастает и сложность обработки термов со сложной формой функции принадлежности, что понижает точность дефаззификации.

В предлагаемом логическом регуляторе ограничения на учет числа указанных факторов принципиально не существует, потому что при любой сложности структуры антецедента продукционного правила результатом вывода будет один из четких термов регулирующей функции логического регулятора, который указан в заключительной части (консеквенте) этого продукционного правила. Например, если в системе (фиг. 3) сработало третье продукционное правило, то коэффициентам ПИД-регулятора 7 присваивается соответствующий набор значений коэффициентов. Точность предлагаемого логического регулятора определяется шириной терма L и элементной базой, на которой построен логический регулятор.

Результат логического вывода в виде одного из термов регулирующей переменной и u(t) с выхода блока логического вывода 2 подается на вход дефаззификатора 3, в котором преобразуется в четкий формат и передается на блок адаптации коэффициентов ПИД-регулятора 8 и на ПИД-регулятор 7, а затем на исполнительный орган 4 для усиления и совершения управляющих воздействий на объекте управления 5 с помощью функции z(t).

Использование данного изобретения позволит снизить время отклика существующих логических регуляторов, используемых для управления сложными быстродействующими технологическими объектами с быстро протекающими процессами, которые описываются нелинейными интегро-дифференциальными уравнениями высокого порядка. Такие системы управления находят все большее применение в машиностроении (станкостроение, авиастроение, робототехника, космическая и автомобильная отрасли), пищевой, нефтяной и газовой промышленности в тех случаях, когда объект управления не имеет приемлемой математической модели.

Техническим результатом является повышение быстродействия и точности управления. Благодаря использованию четкой логики предлагаемый регулятор позволяет управлять быстродействующими технологическими процессами, а также процессами, которые не требовательны к заданному циклу управления.

Адаптивный интеллектуальный логический регулятор, работающий в условиях нечетко заданной информации, состоящий из фаззификатора, блока логического вывода, дефаззификатора, исполнительного органа, объекта управления, датчика обратной связи, отличающийся тем, что включает ПИД-регулятор, сумматор, блок базы правил подстройки коэффициентов ПИД-регулятора, выходы которого соединены с фаззификатором, дефаззификатором и блоком логического вывода, имеющим прямую и обратную связь с блоком базы правил, блок адаптации коэффициентов ПИД-регулятора, а также блок идентификации технологического процесса, соединенных таким образом, что первый вход фаззификатора соединен с выходом исполнительного органа, второй вход фаззификатора соединен с выходом датчика обратной связи, а выход фаззификатора соединен с входом блока логического вывода, выход блока логического вывода соединен с входом дефаззификатора и выходом блока базы правил, выход дефаззификатора соединен с входом блока адаптации коэффициентов ПИД-регулятора, выход которого соединен с ПИД-регулятором, выход ПИД-регулятора соединен с входом исполнительного органа, выход которого соединен с входом объекта управления, выход объекта управления соединен с входом датчика обратной связи, при этом выходные дискретные параметры объекта управления подаются на сумматор, а также на вход блока идентификации технологического процесса, а выход объекта управления соединен с входом блока идентификации технологического процесса, по линии связи передаются входные дискретные параметры объекта управления, а выход блока идентификации технологического процесса соединен с входом блока базы правил для подстройки коэффициентов ПИД-регулятора путем внесения корректировок в базу правил его коэффициентов, а также и тем, что дискретные входные и выходные переменные от объекта управления соединены с дополнительными входами блока логического вывода, число которых равно общему количеству переменных, а в антецедентах продукционных правил термов дискретных входных и выходных переменных объекта управления с термами регулирующих и регулируемых параметров регулятора регулирующие и регулируемые параметры представлены совокупностью четких термов (их функция принадлежности имеет прямоугольную форму).