Устройство для определения значения характеристик готовности изделия к применению

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в опытно-конструкторских работах и практике эксплуатации, где требуется определять оптимальные периоды контроля и технического обслуживания изделий, обеспечивающие требуемую их готовность к применению. Технический результат заключается в повышении точности устройства. Устройство содержит блок памяти, двенадцать вентилей, мультивибратор, пять сумматоров, схему ИЛИ, три триггера, четыре блока нелинейностей, два накапливающих сумматора, пять блоков умножения, два компаратора, два вычитателя, два интегратора, пять элементов задержки, элемент памяти, блок деления и поляризованное реле. 2 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам контроля. Оно может использоваться в научных исследованиях и практике эксплуатации для определения оптимальных сроков технического обслуживания изделий периодического применения и соответствующих значений показателей готовности изделий к применению по назначению.

Известны устройства [3, 4, 5, 6], позволяющие определять периоды обслуживания, обеспечивающие получение экстремальных значений критериальных функций. Общим недостатком указанных устройств является ограниченная функциональная возможность. Они не позволяют определять интервал времени, когда оперативная готовность изделия к применению является не менее требуемой.

Устройство [7] позволяет определять оптимальную по критерию готовности к применению изделия периодичность технического обслуживания и интервал времени, на котором оперативная готовность изделия к применению будет не менее заданной. Область применения данного устройства ограничена изделиями непрерывного использования.

Наиболее близким по технической сущности к заявляемому изобретению является устройство [8], содержащее блок памяти, тринадцать вентилей, два сумматора, мультивибратор, схему ИЛИ, три триггера, два блока нелинейностей, два накапливающих сумматора, три блока умножения, два компаратора, два вычитателя, два интегратора, пять элементов задержки, элемент памяти, делитель, поляризованное реле. Его недостатком является низкая точность определения значений выходных величин, т.к. не позволяет учитывать изменение скорости расходования надежностного потенциала изделия на этапе его обслуживания.

Целью заявляемого технического решения является повышение точности определения значений выходных величин. Цель достигается путем учета различия значения интенсивности отказов изделия соответственно изменению режима его функционирования.

Каждое изделие непрерывно расходует свой надежностный потенциал, причем скорость расходования зависит от режима его использования [1]. Изменение режима проявляется в изменении интенсивности отказов.

Процесс применения многих изделий имеет циклический характер. Каждый цикл может включать работу изделия в номинальном режиме, в облегченном режиме, а также в режиме отдыха. Диаграмма процесса применения показана на фигуре 1, где отражены следующие величины:

τ - длительность цикла применения изделия (например, одни сутки);

t1 - длительность применения изделия в номинальном режиме с коэффициентом нагрузки kн=1. При этом интенсивность отказов имеет значение λ1.

На интервале t2=τ-t1 различные изделия, в зависимости от технологии их применения и реальной нагрузки, могут находиться в одном из следующих режимов:

а) облегченный режим, в связи с уменьшением нагрузки;

б) отдых после применения.

В связи с этим на интервале времени t2 интенсивность отказов λ2 будет иметь разные значения λ2=λ1·kн в соответствии с изменением коэффициента kн нагрузки. Отметим, что, согласно [2], в случае облегченного режима работы изделия kн<1, а в режиме отдыха, согласно [1], 0<kн □ 1.

Для поддержания изделия в работоспособном состоянии периодически проводится его техническое обслуживание и затрачивается время τобс. При этом выполняется углубленный контроль состояния в течении времени τk1, проведение профилактических работ и восстановление работоспособности в случае обнаружения отказа, на что расходуется время τΒ. По окончании этих работ проводится контрольная проверка состояния изделия в течение времени τk2.

Отметим, что контроль технического состояния выполняется в условиях номинального режима работы изделия. Поэтому на интервалах времени τk1 и τk2 интенсивность отказов равна λ1. Для проведения профилактических и ремонтно-восстановительных работ изделие переводится в режим отдыха, что соответствует интенсивности отказов λ2. В связи с этим продолжительность технического обслуживания выражается так:

или

где Р(Т), Р(τk1+τk2), Р(τB) - вероятность безотказной работы изделия на соответствующем интервале времени.

Период обслуживания T включает в себя множество i = 1, n ¯ циклов применения изделия длительностью τ каждый, т.е.

где

Продолжительность Тц цикла обслуживания изделия с учетом (1) составляет

Вероятность безотказной работы изделия на интервале времени Τ определяется соотношением

Для многих изделий характерным является преобладание внезапных отказов и применим экспоненциальный закон распределения времени их возникновения. При этом имеет место следующее:

Время работоспособного состояния изделия на интервале τ одного цикла применения определяется по формуле

а на интервале времени T его значение будет

Комплексными показателями качества изделия являются коэффициенты готовности KГ и оперативной готовности KОГ.

Коэффициент готовности обслуживаемого изделия с учетом (1), (4), (10) выражается следующим соотношением:

Из (11) видно, что коэффициент готовности существенно зависит от периода T обслуживания изделия. Как показывают исследования, функция KГ(Т) при некотором (оптимальном) значении T* имеет глобальный экстремум.

В связи с изложенным, задачу определения оптимального периода технического обслуживания изделия запишем в следующем виде:

При планировании проведения особо важных работ в некотором интервале времени ξ<T* важно знать, что оперативная готовность изделия к применению будет не менее требуемой (заданной). Это выражается значением коэффициента оперативной готовности в следующем виде:

где

P(ξ) - вероятность безотказной работы изделия, вычисляемая подобно величине P(T).

Задачу определения максимального допустимого интервала времени ξдоп, когда KОГ будет не менее заданного, запишем в следующем виде:

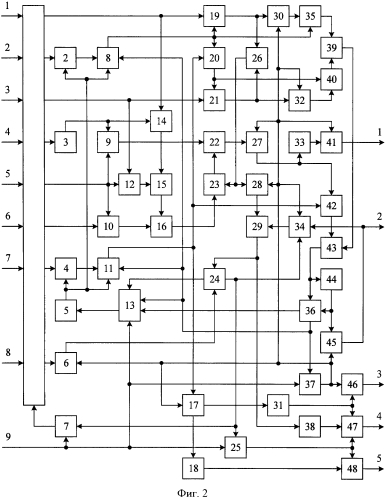

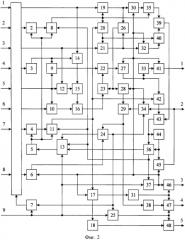

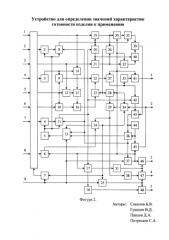

Предложенная математическая модель может быть реализована с помощью заявляемого устройства, схема которого показана на фигуре 2.

Устройство содержит: блок памяти 1, вентили 2, 4, 6, 27, 28, 30, 32, 41, 45, 46, 47, 48, мультивибратор 5, работающий в ждущем режиме, триггеры 7, 25, 37, накапливающие сумматоры 8, 11 (схема и работа представлены в [3]), сумматоры 3, 9, 10, 39, 42, блоки нелинейностей 12, 14, 19, 21, схему ИЛИ 13, блоки умножения 15, 16, 23, 26, 29, поляризованное реле 17, элементы задержки 18, 31, 33, 38, 44, вычитатели 20, 22, компараторы 24, 36, элемент памяти 34, интеграторы 35, 40, блок деления 43.

Перед началом работы устройства исходные данные λ1, t1, λ2, τK1, τB, τK2, τ, K О Г з а д вводятся в блок памяти 1 через его входы с первого по восьмой соответственно.

В работе устройства проявляются два этапа. Вначале определяется оптимальное значение периода T* согласно (12), а затем вычисляется величина ξдоп в соответствии с (15).

Устройство работает следующим образом. По сигналу «Пуск», поступающему с девятого входа устройства, второй 25 и третий 37 триггеры устанавливаются в нулевое состояние. При этом вентили 6, 28, 41, 45, 46, 47, 48 закрываются, а вентили 27, 30, 32 открываются, первый триггер 7 переводится в единичное состояние, обеспечивая этим поступление на выходы блока памяти 1 значений хранимых данных. Кроме того, сигнал «Пуск», пройдя через схему ИЛИ 13, поступает на вход мультивибратора 5. По выходному (одиночному) сигналу мультивибратора 5 открываются первый 2 и второй 4 вентили. Это обеспечивает однократное поступление значения параметра t1 со второго выхода блока памяти 1 в первый накапливающий сумматор 8, а значения параметра τ - с седьмого выхода блока памяти 1 во второй накапливающий сумматор 11. Одиночный сигнал мультивибратора 5 поступает также на управляющие входы первого 2 и второго 11 накапливающих сумматоров, обеспечивая реализацию ими процесса накопления и передачи результирующих данных, полученных в соответствии с (2) и (3), в сопряженные с ними элементы схемы устройства. В то же время, с первого выхода блока памяти 1 значение параметра λ1 передается на первые входы второго 14 и третьего 19 блоков нелинейностей, а с третьего выхода блока памяти 1 значение параметра λ2 поступает на первые входы первого 12 и четвертого 21 блоков нелинейностей.

Рассмотрим первый цикл работы устройства по определению оптимального значения периода T*, выраженного соотношением (12).

Выходной сигнал Т1=t1 первого накапливающего сумматора 8 поступает на вторые входы третьего блока нелинейности 19, первого вычитателя 20 и первого интегратора 35. В блоке нелинейности 19, согласно (6), вычисляется значение P1(t1) и передается на первый вход четвертого блока умножения 26 непосредственно, а через открытый шестой вентиль 30 - на первый вход первого интегратора 35. Значение параметра T=τ с выхода второго накапливающего сумматора 11 через нормально замкнутые контакты реле 17 поступает на вход второго элемента задержки 31, а непосредственно - на второй вход пятого сумматора 42 и на первый вход первого вычитателя 20. Разностный потенциал T2=t2 с выхода вычитателя 20 передается на вторые входы четвертого блока нелинейности 21 и второго интегратора 40. В блоке нелинейности 21 согласно (7) вычисляется значение P2(t2) и передается на второй вход четвертого блока умножения 26 непосредственно, а через открытый седьмой вентиль 32 - на первый вход второго интегратора 40. В первом 35 и втором 40 интеграторах формируются значения времени работоспособного состояния изделия Тф1=tф1 и Тф2=tф2 соответственно. Выходной сигнал первого интегратора 35 передается на первый вход, а выходной сигнал второго интегратора 40 - на второй вход четвертого сумматора 39. Результат сложения, вычисленный согласно (10), с выхода сумматора 39 передается на первый вход блока деления 43.

Одновременно с изложенным происходит вычисление значения величины τобс в соответствии с соотношением (1). При этом, с четвертого выхода блока памяти 1 на первый вход первого сумматора 3 передается значение величины τk1. С пятого выхода блока памяти 1 значение величины τB поступает на первые входы первого блока нелинейности 12, второго 9 и третьего 10 сумматоров. С шестого выхода блока памяти 1 на вторые входы первого 3 и третьего 10 сумматоров передается значение величины τk2. Выходной сигнал (τk1+τk2) первого сумматора 3 поступает на вторые входы второго сумматора 9 и второго блока нелинейности 14. В блоках нелинейностей 12 и 14 формируются значения величин P(τB) и P(τk1+τk2) соответственно. Выходные сигналы блоков нелинейностей 12 и 14 передаются раздельно на первый и второй входы первого блока умножения 15. Результат перемножения Р(τB)·P(τk1+τk2) из блока 15 поступает на второй вход второго блока умножения 16. В третьем сумматоре 10 реализуется сложение величин τB и τk2. Полученный результат передается на первый вход второго блока умножения 16. Выходной сигнал блока 16 поступает на первый вход третьего блока умножения 23, на второй вход которого от четвертого блока умножения 26 приходит сигнал, соответствующий величине P(τ). В третьем блоке умножения 23 реализуется произведение его входных величин (τB+τk2)P(τ)·P(τB)·P(τk1+τk2) и передается на второй вход второго вычитателя 22. Выходной сигнал второго сумматора 9 (τk1+τB+τk2) поступает во второй вычитатель 22 через его первый вход. В вычитателе 22 формируется значение величины τобс, отображаемое соотношением (1), и передается через открытый четвертый вентиль 27 в третий элемент задержки 33 и на первый вход пятого сумматора 42. Сигнал, соответствующий сумме (τ+τобс), с выхода сумматора 42 передается в блок деления 43. Результат деления, соответствующий вычисленному согласно (11) значению KГ коэффициента готовности, с выхода блока деления 43 поступает через пятый элемент задержки 44 на второй вход, а непосредственно - на первый вход второго компаратора 36.

На начальном этапе работы устройства, т.е. при малых значениях периода обслуживания T, функция KГ(T) является монотонно возрастающей. В связи с этим, при сравнении текущего KГ(Ti) и задержанного пятым элементом задержки 44 на один цикл вычислений KГ(Ti-1) значений, управляющий сигнал появится на первом выходе компаратора 36 и через схему ИЛИ 13 поступит на вход мультивибратора 5. Одиночный выходной импульс мультивибратора 5 откроет первый 2 и второй 4 вентили. В результате этого значения выходных величин первого 8 и второго 11 накапливающих сумматоров увеличится на величины t1 и τ соответственно. Далее процесс вычисления всех рассмотренных величин и сравнение предыдущего значения KГ(Ti-1) с текущим KГ(Ti) повторится. Число циклов вычислений будет увеличиваться пока будет сохраняться неравенство KГ(Ti)≥KГ(Ti-1). В каждом очередном цикле содержание накапливающих сумматоров 8 и 11 будет увеличиваться на величины t1 и τ соответственно и сохраняться в этих сумматорах до очередного цикла вычислений. Это увеличение сопровождается изменением значений других расчетных величин.

Как только в компараторе 36 окажется, что KГ(Ti)<KГ(Ti-1), управляющий сигнал появится на его втором выходе. По этому сигналу первый 8 и второй 11 накапливающие сумматоры обнуляются, третий триггер 37 переключится в единичное состояние. Его выходной потенциал поступит на первый управляющий вход элемента памяти 34, на управляющий вход реле 17, откроет третий 6, пятый 28, восьмой 41, девятый 45 и десятый 46 вентили, а четвертый 27, шестой 30 и седьмой 32 вентили закроет. Вычисленное значение τобс с выхода третьего элемента задержки 33 через восьмой вентиль 41 поступит на первый выход устройства. Максимальное значение K Г = K Г i − 1 с выхода пятого элемента задержки 44 через девятый вентиль 45 поступит в элемент памяти 34 и на второй выход устройства. Оптимальное значение периода технического обслуживания T*=Ti-1 с выхода второго элемента задержки 31 через десятый вентиль 46 поступит на третий выход устройства. Реле 17 переключит выход второго накапливающего сумматора 11 на вход первого элемента задержки 18, разорвав связь сумматора 11 с входом второго элемента задержки 31. В то же время, управляющий сигнал со второго выхода второго компаратора 36, пройдя через схему ИЛИ 13, поступит на вход мультивибратора 5 и начнется второй этап работы устройства.

Мультивибратор 5 генерирует одиночные импульсы и передает их в сопряженные с ним блоки 2, 4, 8, 11. Совокупность блоков 19, 20, 21 и 26 обеспечивает вычисление значения величины Ρ(ξ1=τ) подобно тому, как эти блоки функционировали на первом этапе работы устройства. Выходной сигнал Ρ(ξ1) четвертого блока умножения 26 через открытый пятый вентиль 28 поступит на первый вход пятого блока умножения 29. На его второй вход с выхода элемента памяти 34 приходит значение KГ(T*). В блоке умножения 29 вычисляется значение коэффициента оперативной готовности KOΓ(ξ1) в соответствии с (13) и передается на первый вход первого компаратора 24, на второй вход которого с восьмого выхода блока памяти 1 через третий вентиль 6 поступает заданное значение K О Г з а д . В компараторе 24 осуществляется сравнение вычисленного и заданного значений коэффициента оперативной готовности. В начале второго этапа работы устройства (при корректном задании значения K О Г з а д ) вычисленное значение K О Г в ы ч будет больше заданного. Поэтому управляющий сигнал первого компаратора 24 с первого его выхода через схему ИЛИ 13 поступит на вход мультивибратора 5. Далее процесс вычисления значения KОГ и сравнение его с заданным K О Г з а д повторится, но при новом ξi>ξi-1 значении времени ξ, возрастающем согласно (14). Каждое вычисленное значение K О Г i с выхода пятого блока умножения 29 передается в четвертый элемент задержки 38, а значение величины ξi с выхода второго накапливающего сумматора 11 через реле 17 поступает в первый элемент задержки 18.

Как только при сравнении в первом компараторе 24 окажется, что K О Г в ы ч < K О Г з а д , управляющий сигнал возникнет на его втором выходе и поступит на второй вход второго триггера 25, переводя его в единичное состояние. Выходной потенциал триггера 25 поступит на разрешающие входы одиннадцатого 47 и двенадцатого 48 вентилей. В связи с этим, вычисленное значение K О Г в ы ч = K О Г i − 1 с выхода четвертого элемента задержки 38 через вентиль 47 поступит на четвертый выход устройства. С выхода первого элемента задержки 18 через вентиль 48 допустимое значение величины ξдоп=ξi-1 поступит на пятый выход устройства.

Управляющий сигнал со второго выхода первого компаратора 24 поступит также на вторые управляющие входы первого триггера 7 и элемента памяти 34. Триггер 7 переключится в нулевое состояние и его выходной потенциал, поступив на девятый вход блока памяти 1, закроет все его выходы. Элемент памяти 34 обнулится. На этом работа устройства заканчивается.

Положительный эффект, который может быть получен от использования предлагаемого технического решения, состоит в получении расчетных значений оптимального периода обслуживания и соответствующих ему значений коэффициента готовности, времени необходимого на техническое обслуживание изделия, а также допустимого интервала времени после проведения обслуживания, в котором оперативная готовность изделия к применению будет не менее заданной. Вычисленные значения выходных величин позволяют обоснованно планировать применение и техническую эксплуатацию изделия.

При разработке схемы устройства использованы функциональные элементы, описанные в [9].

Источники информации

1. Седякин Н.М. Об одном физическом принципе теории надежности. - Изд. Известия АН СССР, ОТН, Техническая кибернетика, 1966, №3.

2. Половко A.M. Основы теории надежности. - М.: Наука, 1964.

3. Гришин В.Д., Зиновьев С.В., Соколов Б.В., Майданович О.В. Патент RU 2452027, МПК G07C 3/08, 1012.

4. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Цивирко Е.Г. Патент RU 2476934, МПК G07C 3/08, 2013.

5. Соколов Б.В., Стародубов В.А., Гришин В.Д., Цивирко Е.Г. Патент RU 2476935, МПК G07C 3/08, 2013.

6. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Майданович О.В. Патент RU 2479041, МПК G07C 3/08, 2013.

7. Соколов Б.В., Гришин В.Д., Зиновьев С.В., Майданович О.В., Зеленцов В.А. Решение о выдаче патента от 16.12.2013 по заявке №2012149898, МПК G07C 3/08, G06F 17/00, 2012.

8. Соколов Б.В., Гришин В.Д., Зиновьев С.В., Зеленцов В.А., Цивирко Е.Г. Решение о выдаче патента от 16.12.2013 по заявке №2012149896, МПК G07C 3/08, G06F 17/00, 2012.

9. Тетельбаум И.М., Шрейдер Ю.Р. 400 схем для ABM. - М.: Энергия, 1978.

Устройство для определения значений характеристик готовности изделия к применению, содержащее третий блок умножения, блок памяти, первый, второй, третий, седьмой, восьмой входы которого являются одноименными входами устройства, девятый вход которого соединен с первыми входами второго и третьего триггеров, схемы ИЛИ и первого триггера, первый выход которого подключен к девятому входу блока памяти, а второй вход - ко второму выходу первого компаратора, ко второму входу элемента памяти и ко второму входу второго триггера, выход которого соединен с управляющими входами одиннадцатого вентиля и двенадцатого вентиля, выход которого является пятым выходом устройства, а информационный вход через первый элемент задержки подключен ко второму выходу реле, первый выход которого через второй элемент задержки соединен с информационным входом десятого вентиля, выход которого является третьим выходом устройства, а управляющий вход подключен к выходу третьего триггера, к первому входу элемента памяти, к управляющим входам четвертого, пятого, шестого, седьмого и восьмого вентилей, а также ко второму входу реле и к управляющему входу третьего вентиля, информационный вход которого соединен с восьмым выходом блока памяти, а выход - со вторым входом первого компаратора, первый выход которого подключен к четвертому входу схемы ИЛИ, третий вход которой соединен со вторым выходом второго компаратора, со вторым входом третьего триггера, с входами «сброс в ноль» первого и второго накапливающих сумматоров, второй вход схемы ИЛИ подключен к первому выходу второго компаратора, а выход через мультивибратор соединен с управляющими входами первого и второго вентилей, первого накапливающего сумматора и второго накапливающего сумматора, информационный вход которого через второй вентиль подключен к седьмому выходу блока памяти, а выход соединен с первым входом реле, со вторым входом пятого сумматора и с первым входом первого вычитателя, второй вход которого вместе со вторыми входами первого интегратора и третьего блока нелинейности связан с выходом первого накапливающего сумматора, вход которого через первый вентиль подключен ко второму выходу блока памяти, третий выход которого соединен с первым входом четвертого блока нелинейности, второй вход которого связан с выходом первого вычиталеля и со вторым входом второго интегратора, а выход соединен с информационным входом седьмого вентиля, выход которого подключен к первому входу второго интегратора, выход которого соединен со вторым входом четвертого сумматора, первый вход которого подключен к выходу первого интегратора, первый вход которого соединен с выходом шестого вентиля, информационный вход которого через третий блок нелинейности подключен к первому выходу блока памяти, а непосредственно - к первому входу четвертого блока умножения, второй вход которого соединен с выходом четвертого блока нелинейности, а выход подключен к информационному входу пятого вентиля, выход которого соединен с первым входом пятого блока умножения, второй вход которого подключен к выходу элемента памяти, а выход непосредственно связан с первым входом первого компаратора и через четвертый элемент задержки - с информационным входом одиннадцатого вентиля, выход которого является четвертым выходом устройства, первый выход которого через восьмой вентиль соединен с выходом третьего элемента задержки, а второй выход устройства связан с информационным входом элемента памяти и с выходом девятого вентиля, информационный вход которого соединен со вторым входом второго компаратора и с выходом пятого элемента задержки, вход которой связан с первым входом второго компаратора и с выходом блока деления, второй вход которого подключен к выходу пятого сумматора, а первый вход - к выходу четвертого сумматора, отличающееся тем, что в него введены первый, второй и третий сумматоры, первый и второй блоки нелинейностей, первый и второй блоки умножения, причем четвертый, пятый и шестой входы устройства являются одноименными входами блока памяти, первый выход которого соединен с первым входом второго блока нелинейности, второй вход которого связан со вторым входом второго сумматора и с выходом первого сумматора, первый вход которого соединен с четвертым выходом блока памяти, пятый выход которого подключен к первым входам второго и третьего сумматоров и к первому входу первого блока нелинейности, второй вход которого связан с третьим выходом устройства, а выход соединен с первым входом первого блока умножения, второй вход которого подключен к выходу второго блока нелинейности, а выход соединен со вторым входом второго блока умножения, шестой выход блока памяти связан со вторым входом первого сумматора и вторым входом третьего сумматора, выход которого подключен к первому входу второго блока умножения, выход которого соединен с первым входом третьего блока умножения, второй вход которого связан с выходом четвертого блока умножения, а выход соединен со вторым входом второго вычитателя, первый вход которого подключен к выходу второго сумматора, а выход соединен с информационным входом четвертого вентиля, выход которого подключен к входу третьего элемента задержки и к первому входу пятого сумматора.