Устройство, система и способ улучшения коррекции задаваемым аппаратурой алгоритмом

Иллюстрации

Показать всеИзобретение относится к области обучения и коррекции линии связи. Техническим результатом является эффективная коррекция линии связи. Система и способ, в которых, в ответ на коррекцию первого компонента и партнерского по линии связи компонента, первый компонент служит для передачи первого набора данных партнерскому по линии связи компоненту. Первый компонент может содержать по меньшей мере один приемник для приема первого набора корректирующих данных. Первый компонент может дополнительно содержать память, соединенную с приемником, для хранения корректирующих данных. Помимо этого, может иметь место логика коэффициентов, соединенная с памятью коэффициентов, для генерирования первого набора коэффициентов на основе первого набора корректирующих данных. Первый компонент предназначен для отправки первого набора коэффициентов партнерскому по линии связи компоненту. 4 н. и 18 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к вычислительной системе и, в частности (но не исключительно) к методам улучшения процедуры обучения и коррекции линии связи.

Краткое описание чертежей

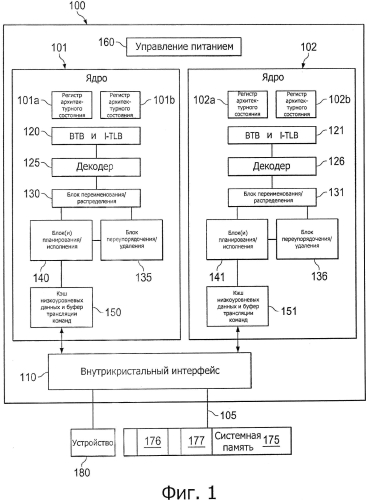

Фиг. 1 является условной схемой, иллюстрирующей вариант осуществления блок-схемы для вычислительной системы, включающей многоядерный процессор.

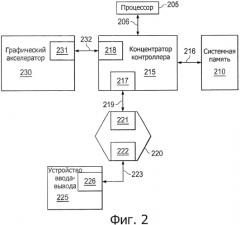

Фиг. 2 является условной схемой, иллюстрирующей вариант осуществления вычислительной системы, включающей в себя архитектуру, совместимую с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ) (PCIe).

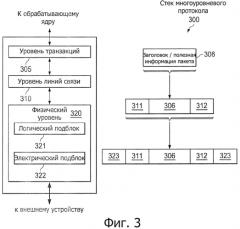

Фиг. 3 является условной схемой, иллюстрирующей вариант осуществления архитектуры межсоединений, совместимый с РВПКЭ, включающей в себя многоуровневую стековую память.

Фиг. 4 является условной схемой, иллюстрирующей вариант осуществления запроса или пакета, совместимого с РВПКЭ, подлежащего приему или передаче в архитектуре межсоединений.

Фиг. 5 является условной схемой, иллюстрирующей вариант осуществления последовательного двухточечного оптоволокна РВПКЭ.

Фиг. 6 является условной схемой, иллюстрирующей глазковую диаграмму частоты ошибочных битов (ЧОБ) (BER) с наилучшей предустановкой и глазковую диаграмму ЧОБ с оптимизированными коэффициентами передачи.

Фиг. 7 является условной схемой, иллюстрирующей вариант осуществления нулевого этапа процедуры обучения и коррекции линии связи.

Фиг. 8 является условной схемой, иллюстрирующей вариант осуществления первого этапа процедуры обучения и коррекции линии связи.

Фиг. 9 является условной схемой, иллюстрирующей таблицу, перечисляющую набор исходных и конечных коэффициентов, которые могут быть применены для установки передатчика или приемника.

Фиг. 10 является условной схемой, иллюстрирующей вариант осуществления второго этапа процедуры обучения и коррекции линии связи.

Фиг. 11 является условной схемой, иллюстрирующей вариант осуществления третьего этапа процедуры обучения и коррекции линии связи.

Фиг. 12 показывает способ для обучения и коррекции линии связи, совместимый с вариантом осуществления настоящего изобретения.

Фиг. 13 показывает другой способ для обучения и коррекции линии связи, совместимый с вариантом осуществления настоящего изобретения.

Подробное описание

В нижеследующем описании изложены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные аппаратные структуры, конкретные подробности архитектуры и микроархитектуры, конкретные конфигурации регистров, конкретные типы команд, конкретные системные компоненты, конкретные измерения (высоты), конкретные ступени и операции процессорного конвейера и т.п., чтобы обеспечить детальное понимание настоящего изобретения. Для специалиста будет, однако, ясно, что эти конкретные подробности не обязательны при практическом применении настоящего изобретения. В иных случаях, общеизвестные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы или коды для описанных алгоритмов, конкретный микропрограммный код, конкретная операция межсоединения, конкретные логические конфигурации, конкретные методы изготовления и материалы, конкретные воплощения компилятора, конкретные выражения алгоритмов в коде, конкретные методы или логика отключения или отпирания питания и прочие конкретные подробности компьютерной системы не описаны в деталях, чтобы избежать ненужного запутывания настоящего изобретения.

Хотя нижеследующие варианты осуществления могут описываться со ссылкой на экономию энергии и энергетическую эффективность в конкретных интегральных схемах, таких как вычислительные платформы или микропроцессоры, другие варианты осуществления применимы к иным типам интегральных схем и логических устройств. Методы и пояснения, аналогичные описанным здесь вариантам осуществления, могут применяться к другим типам схем или полупроводниковых устройств, которые могут также получать выгоду от энергетической эффективности и экономии энергии. Например, раскрытые варианты осуществления не ограничены настольными компьютерными системами или системами Ultrabooks™. Они могут также использоваться в других устройствах, таких как карманные устройства, планшеты, иные тонкие ноутбуки, устройства на интегральных схемах и встроенные приложения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства Интернет-протокола, цифровые камеры, персональные цифровые ассистенты (ПЦА) (PDA) и карманные персональные компьютеры (ПК) (PC). Встроенные приложения, как правило, включают в себя микроконтроллер, цифровой сигнальный процессор (ЦСП) (DSP), систему на кристалле, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любую иную систему, которая может выполнять функции и операции, поясненные ниже. Кроме того, описанные здесь устройства, способы и системы не ограничены физическими вычислительными устройствами, но могут также относиться к программным оптимизациям для экономии энергии и энергетической эффективности. Как станет сразу ясно из нижеследующего описания, варианты осуществления описанных здесь способов, устройств и систем (касается ли это аппаратного обеспечения, встроенных программ, программного обеспечения или их комбинации) актуальны для будущего «зеленой технологии», сбалансированного с соображениями производительности.

По мере развития вычислительных систем их компоненты становятся все более сложными. В результате сложность архитектуры межсоединений для стыковки и осуществления связи между этими компонентами тоже увеличивается, чтобы гарантировать удовлетворение требований по ширине полосы пропускания для оптимальной работы компонентов. Далее, различные сегменты рынка требуют различных аспектов архитектур межсоединений, чтобы отвечать рыночным нуждам. Например, серверы требуют более высокой производительности, тогда как мобильная экосистема иногда способна жертвовать общей производительностью ради экономии мощности. Кроме того, единственное назначение большинства оптических волокон состоит в обеспечении наивысшей возможной производительности с максимальной экономией мощности. Ниже обсуждаются несколько межсоединений, которые будут иметь потенциальную выгоду из аспектов описанного здесь изобретения.

На фиг. 1 показан вариант осуществления блок-схемы для вычислительной системы, включающей в себя многоядерный процессор. Процессор 100 включает в себя любой процессор или устройство обработки, такое как микропроцессор, встроенный процессор, цифровой сигнальный процессор (ЦСП), сетевой процессор, карманный процессор, прикладной процессор, сопроцессор, система на кристалле (SoC) или иное устройство для исполнения кода. Процессор 100 в одном варианте осуществления включает в себя по меньшей мере два ядра: ядро 101 и 102, которые могут включать в себя асимметричные ядра или симметричные ядра (проиллюстрированный вариант осуществления). Однако процессор 100 может включать в себя любое число элементов обработки, которые могут быть симметричными или асимметричными.

В одном варианте осуществления элемент обработки относится к аппаратному обеспечению или логике для поддержания программного потока. Примеры аппаратных элементов обработки включают в себя: потоковый блок, потоковый слот, поток, блок обработки, контекст, контекстный блок, логический процессор, аппаратный поток, ядро и (или) любой иной элемент, который способен удерживать состояние для процессора, такое как исполняемое состояние или архитектурное состояние. Иными словами, элемент обработки в одном варианте осуществления относится к любой аппаратуре, способной независимо ассоциироваться с кодом, такой как программный поток, операционная система, приложение или иной код. Физическим процессором (или процессорной панелью) обычно называют интегральную схему, которая потенциально включает в себя любое число других элементов обработки, таких как ядра или аппаратные потоки.

Ядром часто именуют логику, расположенную на интегральной схеме, способной поддерживать независимое архитектурное состояние, причем каждое независимо поддерживаемое архитектурное состояние ассоциируется с по меньшей мере некоторыми выделенными источниками исполнения. В противоположность ядрам аппаратный поток обычно относится к любой логике, расположенной на интегральной схеме, способной поддерживать независимое архитектурное состояние, причем эти независимо поддерживаемые архитектурное состояния совместно обращаются к источникам исполнения. Как видно, когда некоторые ресурсы используются совместно, а прочие выделены архитектурному состоянию, протягивается линия между номенклатурой аппаратного потока и ядром. Зачастую, ядро и аппаратный поток рассматриваются операционной системой как отдельные логические процессоры, где операционная система способна по отдельности планировать операции на каждом логическом процессоре.

Физический процессор 100, как показано на фиг. 1, включает два ядра: ядро 101 и ядро 102. Ядро 100 и ядро 102 считаются симметричными ядрами, т.е. ядрами с одинаковыми конфигурациями, функциональными блоками и (или) логикой. В другом варианте осуществления ядро 101 включает в себя особенное процессорное ядро, тогда как ядро 102 включает в себя обычное процессорное ядро. Однако ядра 101 и 102 могут по отдельности выбираться из любого типа ядер, таких как собственное ядро, программно-управляемое ядро, ядро, приспособленное для исполнения собственной структуры системы команд (ССК) (ISA), ядро, приспособленное для исполнения транслированной структуры системы команд, совместно разработанное ядро или иное известное ядро. В среде гетерогенных ядер (т.е. симметричных ядер) некоторая форма трансляции, такая как двоичная трансляция, может использоваться для составления графика или для исполнения кода в одном или обоих ядрах. В продолжение обсуждения, проиллюстрированные в ядре 101 функциональные блоки описаны более подробно ниже, а блоки в ядре 102 в описанном варианте осуществления работают аналогично.

Как показано, ядро 101 включает в себя два аппаратных потока 101а и 101b, которые могут также именоваться как аппаратные потоковые слоты 101а и 101b. Поэтому программные элементы, такие как операционная система, в одном варианте осуществления потенциально рассматривают процессор 100 как четыре раздельных процессора, т.е. четыре логических процессора или элемента обработки, способных одновременно исполнять четыре программных потока. Как упомянуто выше, первый поток ассоциируется с регистрами 101а архитектурного состояния, второй поток ассоциируется с регистрами 101b архитектурного состояния, третий поток может ассоциироваться с регистрами 102а архитектурного состояния, а четвертый поток может ассоциироваться с регистрами 102b архитектурного состояния. Здесь каждый из регистров (101а, 101b, 102а и 102b) архитектурного состояния может пониматься как элементы обработки, потоковые слоты или потоковые блоки, как описано выше. Как показано, регистры 101a архитектурного состояния повторяются в регистрах 101b архитектурного состояния, так что отдельные архитектурные состояния (контексты) способны сохраняться для логического процессора 101а и логического процессора 101b. В ядре 101 другие меньшие ресурсы, такие как указатели команд и логика переименования в блоке 130 распределения и переименования, также могут дублироваться для потоков 101a и 101b. Некоторые ресурсы, такие как переупорядочивающие буферы в блоке 135 переупорядочения/удаления, буфер 120 трансляции команд (БТК) (ITLB), буферы загрузки/хранения и очереди могут совместно использоваться посредством распределения. Другие ресурсы, такие как универсальные внешние регистры, базовый(-ые) регистр(ы) таблицы переадресации страниц, кэш низкоуровневых данных и буфер 150 трансляции данных, функциональный(-ые) модуль(-и) 140 и части особенного блока 135 потенциально являются полностью совместно используемыми.

Процессор 100 зачастую включает в себя другие ресурсы, которые могут быть полностью совместно используемыми, совместно используемыми посредством распределения, или выделяться элементами либо элементам обработки. На фиг. 1 показан вариант осуществления чисто примерного процессора с проиллюстрированными логическими блоками/ресурсами процессора. Отметим, что процессор может включать в себя или опускать любые из этих функциональных блоков, а также включать в себя любые иные непоказанные известные функциональные блоки, логику или встроенное программное обеспечение. Как показано, ядро 101 включает в себя упрощенное характерное особенное процессорное ядро. Но в отличных вариантах осуществления может использоваться обычный процессор. Особенное ядро включает в себя целевой буфер 120 ветвлений для предсказания ветвлений, подлежащих исполнению/получению, и буфер 120 трансляции команд (БТК) (I-TLB) для хранения входных данных трансляции адреса для команд.

Ядро 101 далее включает в себя декодирующий модуль 125, связанный с блоком 120 выборки, для декодирования выбранных элементов. Логика выборки в одном варианте осуществления включает в себя отдельные последовательности, ассоциированные с потоковыми слотами 101а, 101b, соответственно. Обычно ядро 101 ассоциируется с первой структурой системы команд (ССК), которая определяет/конкретизирует команды, исполняемые в процессоре 100. Часто команды машинного кода, которые являются частью первой ССК, включают в себя часть команды (именуемую кодом операции), которая ссылается на (конкретизирует) команду или операцию, подлежащую выполнению. Декодирующая логика 125 включает в себя схему, которая распознает эти команды из их кодов операции и пропускает декодированные команды в конвейер для обработки, как определено первой ССК. Например, как более подробно описано ниже, декодеры 125 в одном варианте осуществления включают в себя логику, разработанную или приспособленную для распознавания конкретных команд, таких как команда транзакции. В результате распознавания декодерами 125 архитектура или ядро 101 воспринимает конкретные заранее заданные действия для выполнения задач, связанных с соответствующей командой. Важно отметить, что любые из описанных здесь задач, блоков, операций и способов могут выполняться в ответ на единственную команду или множество команд, некоторые из которых могут быть новыми или старыми командами. Отметим, что декодеры 126 в одном варианте осуществления распознают одну и туже ССК (или ее поднабор). Альтернативно, в среде гетерогенных ядер декодеры 126 распознают вторую ССК (либо поднабор первой ССК, либо отличную ССК).

В одном примере блок 130 распределения и переименования включает в себя распределитель для резервных ресурсов, таких как регистровые файлы, для хранения результатов обработки команд. Однако потоки 101а и 101b потенциально способны к особенному исполнению, когда блок 130 распределения и переименования также резервирует другие ресурсы, такие как буферы переупорядочения, чтобы прослеживать результаты команд. Блок 130 может также включать в себя переименователь регистров для переименования регистров ссылок на программы/команды в другие регистры, внутренние для процессора 100. Блок 135 переупорядочения/удаления включает в себя такие компоненты как упомянутые выше буферы переупорядочения, буферы загрузки и буферы хранения для поддержания особенного исполнения и последующего обычного удаления команд особенного исполнения.

Блок 140 планировщика и функционального(-ых) модуля(-ей) в одном варианте осуществления включает в себя блок планировщика для планирования команд/операций в функциональных модулях. Например, команда с плавающей запятой планируется в части функционального модуля, который имеет доступный функциональный модуль с плавающей запятой. Регистровые файлы, ассоциированные с функциональными модулями, также включены для хранения результатов обработки информационных команд. Примерные функциональные модули включают в себя функциональный модуль с плавающей запятой, функциональный модуль целых чисел, функциональный модуль операции перехода, функциональный модуль загрузки, функциональный модуль хранения и другие известные функциональные модули.

Кэш низкоуровневых данных и буфер 150 трансляции команд (БТК) (D-TLB) соединен с функциональным(и) модулем(-ями). Кэш данных предназначен для хранения недавно использованных/работавших данных в элементах, таких как операнды данных, которые потенциально удерживаются в связных состояниях памяти. БТК предназначен для хранения недавних трансляций адреса из виртуального/линейного в физический. В качестве конкретного примера процессор может включать в себя структуру таблицы переадресации страниц для разбиения физической памяти на множество виртуальных страниц.

Здесь ядра 101 и 102 совместно обращаются к высокоуровневому или еще более высокому кэшу, такому как кэш второго уровня, связанный с внутрикристальным интерфейсом 110. Отметим, что высокоуровневый или еще более высокий относится к уровням кэша, увеличивающим или дающим дальнейший путь от функциональных модулей. В одном варианте осуществления высокоуровневый кэш представляет собой кэш данных последнего уровня, последний кэш в иерархии памяти в процессоре 100, такой как кэш данных второго или третьего уровня. Однако кэш более высокого уровня не имеет такого ограничения, т.к. он может быть связан с кэшем команд или включать его. Вместо этого кэш трасс - тип кэша команд - может быть связан с декодером 135 для хранения недавно декодированных трасс. Здесь командой потенциально называется макрокоманда (т.е. общая команда, распознанная декодерами), которую можно декодировать в несколько микрокоманд (микроопераций).

В показанной конфигурации процессор 100 также включает в себя модуль 110 внутрикристального интерфейса. Исторически контроллер памяти, который более подробно описан ниже, включен в вычислительную систему, внешнюю для процессора 100. В этом сценарии внутрикристальный интерфейс 110 служит для связи с устройствами, внешними для процессора 100, такими как системная память 175, набор микросхем (часто включающий в себя концентратор контроллера памяти для соединения с памятью 175 и концентратор контроллера ввода-вывода для соединения с периферийными устройствами), концентратор контроллера памяти, северный мост или другую интегральную схему. И в этом сценарии шина 105 может включать в себя любое известное межсоединение, такое как многоточечная шина, двухточечное межсоединение, последовательное межсоединение, параллельная шина, согласованная (к примеру, согласованная с кэшем) шина, архитектура многоуровневого протокола, разностная шина и GTL шина.

Память 175 может быть назначена процессору 100 или совместно использоваться с другими устройствами в системе. Общие примеры типов памяти 175 включают в себя динамическое оперативное запоминающее устройство (ДОЗУ) (DRAM), статическое оперативное запоминающее устройство (СОЗУ) (SRAM), энергонезависимая память и другие известные запоминающие устройства. Отметим, что устройство 180 может включать в себя графический ускоритель, процессор и карту, связанные с концентратором контроллера памяти, накопитель данных, связанный с концентратором контроллера ввода-вывода, беспроводный приемопередатчик, устройство флэш-памяти, аудио контроллер, сетевой контроллер или иное известное устройство.

Однако в последнее время, по мере того, как все больше логики и устройств интегрируются на едином кристалле, таком как интегральная схема, каждое из этих устройств может быть встроено в процессор 100. Например, в одном варианте осуществления концентратор контроллера памяти находится в одном корпусе и (или) кристалле с процессором 100. Здесь часть ядра (часть в ядре) 110 включает в себя один или несколько контроллеров для взаимодействия с другими устройствами, такими как память 175 или графическое устройство. Конфигурация, включающая в себя межсоединение и контроллеры для взаимодействия с такими устройствами, часто именуется резидентной (или конфигурацией un-core). В качестве примера, внутрикристальный интерфейс 110 включает в себя кольцевое межсоединение для внутрикристальной связи и высокоскоростную последовательную двухточечную линию 105 связи для связи вне кристалла. Далее, в среде интегральной схемы даже больше устройств, таких как сетевой интерфейс, сопроцессоры, память 175, графический процессор 180 и любые иные известные компьютерные устройства или интерфейсы могут быть встроены в единственный кристалл или интегральную схему, чтобы обеспечить малые конструктивные параметры при высокой функциональности и низком потреблении мощности.

В одном варианте осуществления процессор 100 способен исполнять код 177 компилятора, оптимизатора и (или) транслятора для компиляции, трансляции и (или) оптимизации прикладного кода 176, чтобы поддерживать описанные здесь устройство и способ или интерфейс к ним. Компилятор часто включает в себя программу или набор программ для трансляции исходного текста/кода в выходной текст/код. Обычно компиляция программного/прикладного кода компилятором происходит во множестве стадий и проходов для преобразования кода высокоуровневого языка программирования в код низкоуровневого машинного или ассемблерного языка. Далее, для простой компиляции могут по-прежнему использоваться компиляторы единственного прохода. Компилятор может использовать любые известные методы компиляции и выполнять любые известные операции компилятора, такие как лексический анализ, предварительная обработка, синтаксический анализ, семантический анализ, генерирование кода, преобразование кода и оптимизация кода.

Более крупные компиляторы часто используют множество стадий, но чаще всего эти стадии включены в два общих этапа: (1) предварительный, т.е. в общем, когда могут иметь место синтаксическая обработка, семантическая обработка и кое-что из преобразования/оптимизации, и (2) завершающий, т.е. в общем, когда имеют место анализ, преобразования, оптимизации и генерирование кода. Некоторые компиляторы именуются средними, что иллюстрирует размывание границы между предварительным и завершающим компиляторами. В результате ссылка на введение, ассоциирование, генерирование или иную операцию могут иметь место в любых из вышеупомянутых стадий или проходов, а также в любых иных стадиях или проходах компилятора. В качестве иллюстративного примера, компилятор потенциально вводит операции, вызовы, функции и т.п.в одной или нескольких стадиях компиляции, как введение вызовов/операций в предварительной стадии компиляции, а затем преобразование этих вызовов/операций в низкоуровневый код во время стадии преобразования. Отметим, что в ходе динамической компиляции код компилятора или код динамической оптимизации может вводить такие операции/вызовы, а также оптимизировать код для исполнения во время прогона. В качестве конкретного иллюстративного примера, двоичный код (уже компилированный код) может динамически оптимизироваться во время прогона. Здесь, программный код может включать в себя код динамической оптимизации, двоичный код или их комбинацию.

Аналогично компилятору транслятор, такой как двоичный транслятор, транслирует код либо статически, либо динамически, для оптимизации и (или) трансляции кода. Поэтому ссылка на исполнение кода, прикладной код, программный код или иную программную среду может быть сделана на: (1) исполнение компилированных(-ой) программ(ы), оптимизатора кода оптимизации или транслятора либо динамически, либо статически, чтобы компилировать программный код для сохранения программных структур, выполнения других операций, оптимизации кода или трансляции кода; (2) исполнение основного программного кода, включающего в себя операции/вызовы, такие как прикладной код, который оптимизирован/компилирован; (3) исполнение другого программного кода, такого как библиотеки, связанного с основным программным кодом, для сохранения программных структур, выполнения другого программного обеспечения, относящегося к операциям, или для оптимизации кода; или (4) их комбинацию.

Одна архитектура межсоединительного оптического волокна включает в себя архитектуру с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ) (PCIe). Первичная цель РВПКЭ состоит в том, чтобы дать возможность компонентам и устройствам от разных поставщиков взаимодействовать в открытой архитектуре, перекрывая множество сегментов рынка: клиентам (настольным и мобильным устройствам), серверам (стандартным и предпринимательским) и встроенным и связным устройствам. РВПК Экспресс является высокопроизводительным универсальным входным-выходным межсоединением для широкого разнообразия будущих вычислительных и связных платформ. Некоторые атрибуты РВПК, такие как модель использования, архитектура загрузки-хранения и программные интерфейсы, поддерживаются посредством их пересмотра, тогда как предыдущие воплощения параллельной шины заменены сильно расширяемым полностью последовательным интерфейсом. Самые последние версии РВПК Экспресс получают преимущество от улучшений двухточечных межсоединений, технологии на основе коммутаций и пакетированного протокола для доставки новых уровней качества и свойств. Среди некоторых из улучшенных свойств, поддерживаемых РВПК Экспресс, управление энергопотреблением, качество сервиса, поддержка горячего включения / горячей замены, целостность данных и обработка ошибок.

На фиг. 2 показан вариант осуществления оптического волокна, составленного из двухточечных линий связи, которые соединяют между собой набор компонентов. Система 200 включает в себя процессор 205 и системную память 210, соединенную с концентратором 215 контроллера. Процессор 205 включает в себя любой элемент обработки, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 205 соединен с концентратором 215 контроллера посредством внешней шины (ВШ) (FSB) 206. В одном варианте осуществления ВШ 206 является последовательным двухточечным межсоединением, как описано ниже. В другом варианте осуществления линия 206 связи включает в себя последовательную разностную межсоединительную архитектуру, которая совместима со стандартом разностного межсоединения.

Системная память 210 включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (ОЗУ) (RAM), энергонезависимая память или другая память, к которой могут обращаться устройства в системе 200. Системная память 210 соединена с концентратором 215 контроллера посредством интерфейса 216 памяти. Примеры интерфейса памяти включают в себя интерфейс памяти с двойной скоростью данных (ДСД) (DDR), двухканальный интерфейс памяти ДСД и интерфейс памяти динамического ОЗУ (ДОЗУ) (DRAM).

В одном варианте осуществления концентратор 215 контроллера является корневым концентратором, корневым комплексом или корневым контроллером в иерархии межсоединений с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ). Примеры концентратора 215 контроллера включают в себя набор микросхем, концентратор контроллера памяти (ККП) (МСН), северный мост, концентратор контроллера межсоединений (ККМ) (ICH), южный мост и корневой контроллер/концентратор. Зачастую термин «набор микросхем» относится к двум физически раздельным концентраторам контроллера, т.е. к концентратору контроллера памяти (ККП), соединенному с концентратором контроллера межсоединений (ККМ). Отметим, что нынешние системы часто включают в себя ККП, интегрированный с процессором 205, тогда как контроллер 215 служит для связи с устройствами ввода-вывода таким же образом, как описано ниже. В некоторых вариантах осуществления одноранговая маршрутизация опционально поддерживается посредством корневого сложного устройства.

Здесь, концентратор 215 контроллера связан с коммутатором/мостом 220 посредством последовательной линии 219 связи. Модули 217 и 218 ввода-вывода, которые могут также именоваться интерфейсами/портами 217 и 218, включают/воплощают стек многоуровневого протокола, чтобы обеспечить связь между концентратором 215 контроллера и коммутатором 220. В одном варианте осуществления множество устройств способны соединяться с коммутатором 220.

Коммутатор/мост 220 маршрутизирует пакеты/сообщения от устройства 225 в восходящем направлении, т.е. вверх по иерархии в направлении корневого комплекса, к концентратору 215 контроллера и в нисходящем направлении, т.е. вниз по иерархии в направлении от корневого контроллера, от процессора 205 или системной памяти 210 к устройству 225. Коммутатором 220 в одном варианте осуществления называется логическая сборка из множества виртуальных мостовых устройств РВПК-РВПК.

Устройство 225 включает в себя любое внутреннее или внешнее устройство или компонент для соединения с электронной системой, такое как устройство ввода-вывода, контроллер сетевого интерфейса (КСИ) (NIC), расширительная плата, аудио процессор, сетевой процессор, жесткий дисковод, запоминающее устройство, CD/DVD ROM, монитор, принтер, мышь, клавиатура, маршрутизатор, портативное запоминающее устройство, устройство сверхбыстродействующей передачи, устройство универсальной последовательной шины (УПШ) (USB), сканер и другие устройства ввода-вывода. Часто на профессиональном жаргоне РВПКЭ такое устройство называется оконечным устройством. Хотя это не показано конкретно, устройство 225 может включать в себя мост от РВПКЭ к РВПК/РВПК-Х для поддержки устаревшей или другой версии устройств РВПК. Оконечные устройства в РВПКЭ часто классифицируются как устаревшие, РВПКЭ или корневые комплексные интегрированные оконечные устройства.

Графический акселератор 230 также связан с концентратором 215 контроллера посредством последовательной линии 232 связи. В одном варианте осуществления графический акселератор 230 соединен с ККП, который соединен с ККМ. Коммутатор 220 и, соответственно, устройство 225 ввода-вывода соединены далее с ККМ. Модули 231 и 218 ввода-вывода также предназначены для воплощения стека многоуровневого протокола для осуществления связи между графическим акселератором 230 и концентратором 215 контроллера. Аналогично обсуждавшемуся выше ККП графический контроллер или графический акселератор 235 может быть сам интегрирован с процессором 205.

На фиг. 3 проиллюстрирован вариант осуществления стека многоуровневого протокола. Стек 300 многоуровневого протокола включает в себя любой вид стека многоуровневой связи, такой как стек быстрого соединения трасс (БСТ) (QPI), стек РВПКЭ, стек межсоединений высокопроизводительных вычислений следующего поколения или другой многоуровневый стек. Хотя непосредственно нижеследующее обсуждение со ссылками на фиг. 2-5 относится к стеку РВПКЭ, те же самые идеи могут быть применены и к иным стекам межсоединений. В одном варианте осуществления стек 300 протокола представляет собой стек протокола РВПКЭ, включающий в себя уровень 305 транзакций, уровень 310 линий связи и физический уровень 320. Интерфейс, такой как интерфейсы 317, 318, 321, 322, 326 и 331 на фиг. 3, могут быть представлены как стек 300 протокола связи. Представление в качестве стека протокола связи может также относиться к модулю или интерфейсу, воплощающему/включающему стек протокола.

РВПК Экспресс использует пакеты для передачи информации между компонентами. Пакеты формируются в уровне 305 транзакций и уровне 310 линий данных для переноса информации от передающего компонента к приемному компоненту. По мере того, как переданные пакеты проходят через другие уровни, они расширяются дополнительной информацией, необходимой для обработки пакетов в этих уровнях. На приемной стороне происходит обратный процесс, и пакеты преобразуются из их представления в физическом уровне 320 в представление в уровне 310 линий данных и, наконец (для пакетов уровня транзакций), в форму, которую можно обрабатывать уровнем 305 транзакций приемного устройства.

Уровень транзакций

В одном варианте осуществления уровень 305 транзакций служит для обеспечения интерфейса между ядром обработки устройства и архитектурой межсоединений, такими как уровень 310 линий данных и физический уровень 320. В этом отношении первичная обязанность уровня 305 транзакций состоит в ассемблировании и дезассемблировании пакетов (т.е. пакетов уровня транзакций, или ПУТ (TLP)). Уровень 305 транзакций, как правило, руководит управлением перемещения на основе кредита для ПУТ. РВПКЭ воплощает разделение транзакций, т.е. транзакций с запросом и откликом, разделенных по времени, разрешая линии связи переносить другой трафик, пока целевое устройство собирает данные для отклика.

В дополнение к этому, РВПКЭ использует управление перемещением на основе кредита. В этой схеме устройство сообщает исходное значение кредита для каждого из приемных буферов в уровне 305 транзакций. Внешнее устройство на противоположном конце линии связи, такое как концентратор 115 контроллера по фиг. 1, подсчитывает число кредитов, потребленных каждым ПУТ. Транзакция может быть передана, если эта транзакция не превышает предел кредита. При приеме отклика значение кредита восстанавливается. Преимущество кредитной схемы заключается в том, что запаздывание возврата кредита не влияет на производительность при том условии, что предел кредита не достигается.

В одном варианте осуществления четыре пространства адресов транзакций включают в себя пространство адресов конфигурации, пространство адресов памяти, пространство адресов ввода-вывода и пространство адресов сообщений. Транзакции пространства памяти включают в себя один или несколько запросов чтения и запросов записи для переноса данных в отображаемое в памяти местоположение или из него. В одном варианте осуществления транзакции пространства памяти способны использовать два различных формата адресов, к примеру, формат короткого адреса, такого как 32-разрядный адрес, или формат длинного адреса, такого как 64-разрядный адрес. Транзакции пространства конфигурации используются для обращения к пространству конфигурации устройств РВПКЭ. Транзакции пространства конфигурации включают в себя запросы чтения и запросы записи. Транзакции пространства сообщений (или просто сообщения) определяются для поддержки связи через сеть между агентами РВПКЭ.

Поэтому в одном варианте осуществления уровень 305 транзакций ассемблирует заголовок / полезную информацию 306 пакета. Формат для заголовков / полезных данных текущего пакета можно найти в спецификации РВПКЭ на сайте спецификаций РВПКЭ.

На фиг. 4 показан вариант осуществления описателя транзакции РВПКЭ. В одном варианте осуществления описатель 400 транзакций представляет собой механизм для переноса информации транзакций. В этом отношении описатель 400 транзакций поддерживает идентификацию транзакций в системе. Прочие потенциальные использования включают в себя прослеживание модификаций в упорядочении транзакций по умолчанию и ассоциирование транзакции с каналами.

Описатель 400 транзакций включает в себя поле 402 глобального идентификатора, поле 404 атрибутов и поле 406 канального идентификатора. В проиллюстрированном примере поле 402 глобального идентификатора показано содержащим поле 408 местного идентификатора транзакции и поле 410 идентификатора ресурса. В одном варианте осуществления глобальный идентификатор 402 транзакции является единственным для всех ожидающих выполнения запросов.

Согласно одной реализации, поле 408 местного идентификатора транзакции представляет собой поле, генерируемое запрашивающим агентом, и оно является единственным для всех ожидающих выполнения запросов, которые требуют завершения для этого запрашивающего агента. Далее, в данном примере идентификатор 410 ресурса однозначно идентифицирует запрашивающий агент в иерархии РВПКЭ. Соответственно, вместе с идентификатором 410 ресурса поле 408 местного идентификатора транзакции обеспечивает глобальную идентификацию транзакции в сфере иерархии.

Поле 404 атрибутов конкретизирует характеристики и соотношения транзакции. В этом отношении поле 404 атрибутов потенциально используется для обеспечения дополнительной информаци