Способ для возбуждения устройства фиксации изображений, способ для коррекции цифрового сигнала, устройство фиксации изображений, способ для возбуждения системы захвата изображений и система захвата изображений

Иллюстрации

Показать всеИзобретение относится к области обработки изображений. Технический результат - обеспечение уменьшения смещения, включенного в цифровой сигнал, которое возникает вследствие разности между временем, когда потенциал опорного сигнала начинает изменяться во времени, и временем, когда счетчик начинает подсчет синхросигнала. Способ для возбуждения устройства фиксации изображений, которое содержит: пиксель для вывода пиксельного сигнала и средство аналого-цифрового преобразования для преобразования аналогового сигнала в цифровой сигнал; причем средство аналого-цифрового преобразования содержит: средство сравнения для вывода сигнала (СМР) результата сравнения, получаемого посредством сравнения аналогового сигнала с опорным сигналом, потенциал которого изменяется с течением времени, и средство подсчета для подсчета синхросигнала; причем способ содержит: формирование первого цифрового сигнала (DN1); формирование второго цифрового сигнала (DN2); формирование третьего цифрового сигнала; корректировку третьего цифрового сигнала на основе первого цифрового сигнала (DN1) и второго цифрового сигнала (DN2). 6 н. и 16 з.п. ф-лы, 16 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к устройству фиксации (pickup) изображений и системе захвата (capture) изображений, которые включают в себя модуль аналого-цифрового (AD) преобразования, сконфигурированный так, чтобы преобразовывать пиксельный сигнал, выводимый посредством пикселя, в цифровой сигнал.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Предлагаются устройства фиксации изображений, включающие в себя модуль аналого-цифрового преобразования, сконфигурированный так, чтобы преобразовывать пиксельный сигнал, выводимый посредством пикселя, в цифровой сигнал. Модуль аналого-цифрового преобразования, описанный в выложенном патентном документе (Япония) номер 2011-211535, включает в себя модуль подачи опорных сигналов. Модуль подачи опорных сигналов выводит первый опорный сигнал, потенциал которого изменяется на первую величину в единицу времени, и второй опорный сигнал, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину. Модуль аналого-цифрового преобразования, описанный в выложенном патентном документе (Япония) номер 2011-211535, дополнительно включает в себя модуль сравнения. Модуль сравнения сравнивает пиксельный сигнал с первым опорным сигналом и вторым опорным сигналом. Модуль сравнения также сравнивает потенциал на основе шумового сигнала с первым опорным сигналом и вторым опорным сигналом.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Аспект настоящего изобретения предоставляет способ для возбуждения устройства фиксации изображений, включающего в себя пиксель, сконфигурированный так, чтобы выводить пиксельный сигнал, и модуль аналого-цифрового преобразования, сконфигурированный так, чтобы преобразовывать аналоговый сигнал в цифровой сигнал, причем модуль аналого-цифрового преобразования включает в себя модуль сравнения, сконфигурированный так, чтобы выводить сигнал результата сравнения, полученный посредством сравнения аналогового сигнала с опорным сигналом, потенциал которого изменяется во времени. Способ включает в себя формирование, с использованием модуля аналого-цифрового преобразования, первого цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала с первым опорным сигналом, потенциал которого изменяется на первую величину в единицу времени; формирование, с использованием модуля аналого-цифрового преобразования, второго цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала со вторым опорным сигналом, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину; формирование, с использованием модуля аналого-цифрового преобразования, третьего цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения сигнала на основе пиксельного сигнала с первым опорным сигналом или вторым опорным сигналом; и корректировку третьего цифрового сигнала на основе первого цифрового сигнала и второго цифрового сигнала.

[0004] Другой аспект настоящего изобретения предоставляет способ коррекции цифрового сигнала, который формируется в качестве результата выполнения модулем аналого-цифрового преобразования аналого-цифрового преобразования в отношении аналогового сигнала. Способ включает в себя формирование, с использованием модуля аналого-цифрового преобразования, первого цифрового сигнала на основе результата, полученного посредством сравнения первого аналогового сигнала с первым опорным сигналом, потенциал которого изменяется на первую величину в единицу времени; формирование, с использованием модуля аналого-цифрового преобразования, второго цифрового сигнала на основе результата, полученного посредством сравнения первого аналогового сигнала со вторым опорным сигналом, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину; и коррекцию цифрового сигнала, сформированного с использованием модуля аналого-цифрового преобразования, на основе первого цифрового сигнала и второго цифрового сигнала.

[0005] Еще один другой аспект настоящего изобретения предоставляет способ для возбуждения системы захвата изображений, включающей в себя устройство фиксации изображений, включающее в себя пиксель, сконфигурированный так, чтобы выводить пиксельный сигнал, и модуль аналого-цифрового преобразования, сконфигурированный так, чтобы преобразовывать аналоговый сигнал в цифровой сигнал, причем модуль аналого-цифрового преобразования включает в себя модуль сравнения, сконфигурированный так, чтобы выводить сигнал результата сравнения, полученный посредством сравнения аналогового сигнала с опорным сигналом, потенциал которого изменяется во времени; и процессор (модуль обработки) сигналов, сконфигурированный так, чтобы обрабатывать сигнал, выводимый из устройства фиксации изображений. Способ включает в себя формирование, с использованием модуля аналого-цифрового преобразования, первого цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала с первым опорным сигналом, потенциал которого изменяется на первую величину в единицу времени; формирование, с использованием модуля аналого-цифрового преобразования, второго цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала со вторым опорным сигналом, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину; формирование, с использованием модуля аналого-цифрового преобразования, третьего цифрового сигнала на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения сигнала на основе пиксельного сигнала с первым опорным сигналом или вторым опорным сигналом; и коррекцию третьего цифрового сигнала на основе первого цифрового сигнала и второго цифрового сигнала.

[0006] Дополнительный аспект настоящего изобретения предоставляет устройство фиксации изображений, включающее в себя пиксель, сконфигурированный так, чтобы выводить пиксельный сигнал, модуль аналого-цифрового преобразования, сконфигурированный так, чтобы преобразовывать аналоговый сигнал в цифровой сигнал, модуль подачи опорных сигналов, сконфигурированный так, чтобы подавать опорный сигнал, потенциал которого изменяется во времени, в модуль аналого-цифрового преобразования, и модуль коррекции. Модуль аналого-цифрового преобразования включает в себя модуль сравнения, сконфигурированный так, чтобы выводить сигнал результата сравнения, полученный посредством сравнения аналогового сигнала с опорным сигналом, и запоминающее устройство, сконфигурированное так, чтобы хранить первый цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала с первым опорным сигналом, потенциал которого изменяется на первую величину в единицу времени, второй цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала со вторым опорным сигналом, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину, и третий цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения сигнала на основе пиксельного сигнала с первым опорным сигналом или вторым опорным сигналом. Модуль коррекции сконфигурирован так, чтобы корректировать третий цифровой сигнал на основе первого цифрового сигнала и второго цифрового сигнала.

[0007] Еще один дополнительный аспект настоящего изобретения предоставляет систему захвата изображений, включающую в себя устройство фиксации изображений, включающее в себя пиксель, сконфигурированный так, чтобы выводить пиксельный сигнал, модуль аналого-цифрового преобразования, сконфигурированный так, чтобы преобразовывать аналоговый сигнал в цифровой сигнал, и модуль подачи опорных сигналов, сконфигурированный так, чтобы подавать опорный сигнал, потенциал которого изменяется во времени, в модуль аналого-цифрового преобразования; процессор сигналов, сконфигурированный так, чтобы обрабатывать сигнал, выводимый из устройства фиксации изображений; и модуль коррекции. Модуль аналого-цифрового преобразования включает в себя модуль сравнения, сконфигурированный так, чтобы выводить сигнал результата сравнения, полученный посредством сравнения аналогового сигнала с опорным сигналом, и запоминающее устройство, сконфигурированное так, чтобы хранить первый цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала с первым опорным сигналом, потенциал которого изменяется на первую величину в единицу времени, второй цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения первого аналогового сигнала со вторым опорным сигналом, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину, и третий цифровой сигнал на основе сигнала результата сравнения, выводимого посредством модуля сравнения в качестве результата сравнения модулем сравнения сигнала на основе пиксельного сигнала с первым опорным сигналом или вторым опорным сигналом. Модуль коррекции сконфигурирован так, чтобы корректировать третий цифровой сигнал на основе первого цифрового сигнала и второго цифрового сигнала.

[0008] Дополнительные признаки настоящего изобретения должны становиться очевидными из нижеприведенного описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0009] Фиг. 1A является схемой, иллюстрирующей пример конфигурации устройства фиксации изображений.

[0010] Фиг. 1B является схемой, иллюстрирующей пример подробной конфигурации части устройства фиксации изображений.

[0011] Фиг. 2 является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0012] Фиг. 3A является схемой, иллюстрирующей пример операции битового сдвига, выполняемой в отношении цифрового сигнала.

[0013] Фиг. 3B является схемой, иллюстрирующей пример операций модуля подачи опорных сигналов и счетчика.

[0014] Фиг. 4A является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0015] Фиг. 4B является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0016] Фиг. 5A является схемой, иллюстрирующей пример конфигурации устройства фиксации изображений.

[0017] Фиг. 5B является схемой, иллюстрирующей пример подробной конфигурации части устройства фиксации изображений.

[0018] Фиг. 6A является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0019] Фиг. 6B является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0020] Фиг. 7 является схемой, иллюстрирующей пример системы захвата изображений.

[0021] Фиг. 8A является схемой, иллюстрирующей пример конфигурации части устройства фиксации изображений.

[0022] Фиг. 8B является схемой, иллюстрирующей пример работы устройства фиксации изображений.

[0023] Фиг. 9A является схемой, иллюстрирующей пример системы захвата изображений.

[0024] Фиг. 9B является схемой, иллюстрирующей пример конфигурации процессора цифровых сигналов (DSP) устройства фиксации изображений.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0025] В устройстве фиксации изображений, раскрытом в выложенном патентном документе (Япония) номер 2011-211535, можно вызывать смещение между значениями сигналов цифровых сигналов, полученных посредством преобразования аналоговых сигналов, имеющих идентичное значение сигнала, с использованием первого и второго опорных сигналов. Для устройства фиксации изображений, раскрытого в выложенном патентном документе (Япония) номер 2011-211535, уменьшение смещения, включенного в цифровой сигнал, не поясняется.

[0026] Способ для возбуждения устройства фиксации изображений, способ для коррекции цифрового сигнала, устройство фиксации изображений, способ для возбуждения системы захвата изображений и система захвата изображений, описанные ниже, устраняют недостаток, описанный выше.

ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0027] Ниже описывается устройство фиксации изображений согласно первому варианту осуществления со ссылкой на чертежи.

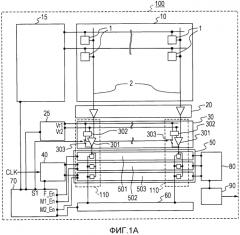

[0028] Фиг. 1A является принципиальной схемой устройства 100 фиксации изображений согласно первому варианту осуществления. Компоненты устройства 100 фиксации изображений, проиллюстрированного на фиг. 1A, сформированы на одной полупроводниковой подложке.

[0029] Устройство 100 фиксации изображений включает в себя пиксельный модуль 10, в котором пиксели 1 размещены в нескольких строках и нескольких столбцах. Каждый из пикселей 1 выводит пиксельный сигнал в модуль 20 усиления в ответ на сканирование, выполняемое посредством схемы 15 вертикального сканирования. Каждый из пикселей 1 включает в себя часть фотоэлектрического преобразования, в котором происходит фотоэлектрическое преобразование падающего света. Пиксельный сигнал включает в себя шумовой сигнал и сигнал фотоэлектрического преобразования, который выводится на основе зарядов, возникающих в результате фотоэлектрического преобразования падающего света. Схема 15 вертикального сканирования выполняет сканирование в отношении пикселей 1 построчно в соответствии с сигналом, выводимым из генератора тактовых импульсов (в дальнейшем в этом документе, сокращенно называемого TG) 70. Модуль 20 усиления усиливает каждый пиксельный сигнал и выводит усиленный пиксельный сигнал в соответствующую схему 301 компаратора, включенную в модуль 30 сравнения. Модуль 20 усиления расположен в электрическом пути между модулем 30 сравнения и пикселями 1. Модуль 25 подачи опорных сигналов выводит несколько опорных сигналов в селекторные схемы 302 в соответствующих столбцах. Каждая из схем 301 компаратора выводит сигнал SEL выбора в соответствующую селекторную схему 302 через переключатель 303 на основе сигнала результата сравнения, который указывает результат, полученный посредством сравнения сигнала, выводимого посредством модуля 20 усиления, с пороговым сигналом. На основе сигнала SEL выбора, каждая из селекторных схем 302 выбирает опорный сигнал, который должен быть выведен в соответствующую схему 301 компаратора, из нескольких опорных сигналов. Каждая из схем 301 компаратора выводит сигнал результата сравнения, который указывает результат, полученный посредством сравнения сигнала, выводимого посредством модуля 20 усиления с опорным сигналом, в запоминающее устройство 50 и соответствующую селекторную схему 302. Запоминающее устройство 50 включает в себя запоминающие устройства 501 флагов, первые запоминающие устройства 502 и вторые запоминающие устройства 503. TG 70 выводит сигнал F_En в запоминающие устройства 501 флагов. Счетчик 40 выводит сигнал значения счетчика, который представляет подсчитанное значение синхросигнала CLK, в первые запоминающие устройства 502 и вторые запоминающие устройства 503. TG 70 выводит сигналы M1_En и M2_En в первые запоминающие устройства 502 и вторые запоминающие устройства 503, соответственно. Схема 60 горизонтального сканирования инструктирует цифровым сигналам, хранимым посредством запоминающих устройств 501 флагов, первых запоминающих устройств 502 и вторых запоминающих устройств 503 в соответствующих столбцах, последовательно вводиться в процессор 80 цифровых сигналов (DSP). DSP 80 обрабатывает сигналы, выводимые из запоминающих устройств 501 флагов, первых запоминающих устройств 502 и вторых запоминающих устройств 503 в соответствующих столбцах, и выводит обработанные сигналы в выходную схему 90. Выходная схема 90 выводит сигналы за пределы устройства 100 фиксации изображений в соответствии с сигналом, выводимым посредством TG 70.

[0030] В устройстве 100 фиксации изображений, проиллюстрированном на фиг. 1A, каждый из модулей 110 аналого-цифрового преобразования в соответствующем столбце включает в себя модуль 30 сравнения и запоминающее устройство 50. Кроме того, каждый из модулей 110 аналого-цифрового преобразования предоставляется для соответствующего столбца пикселей 1.

[0031] Далее описывается конфигурация DSP 80 со ссылкой на фиг. 1B. DSP 80 включает в себя модуль 801 сдвига уровня, сконфигурированный так, чтобы сдвигать биты сигнала, хранимого в первом запоминающем устройстве 502, по направлению к старшему биту (MSB) на два бита, когда значение сигнала, хранимое во запоминающем устройстве 501 флагов, имеет низкий уровень. Когда выполняется операция коррекции, проиллюстрированная на фиг. 4B, модуль 801 сдвига уровня выводит результирующий сигнал в модуль 802 извлечения значений коррекции. Сигнал также выводится в модуль 802 извлечения значений коррекции из второго запоминающего устройства 503. Значение коррекции, сформированное посредством модуля 802 извлечения значений коррекции, выводится в модуль 803 вычисления коррекции. Модуль 803 вычисления коррекции корректирует сигнал, выводимый посредством модуля 801 сдвига уровня, и выводит скорректированный сигнал в S-N-модуль 804. S-N-модуль 804 определяет разность между сигналом, выводимым посредством модуля 803 вычисления коррекции, и сигналом, выводимым посредством второго запоминающего устройства 503, и выводит результирующий сигнал в выходную схему 90. DSP 80 служит в качестве модуля коррекции в этом варианте осуществления.

[0032] Ссылаясь на фиг. 2, описывается работа устройства 100 фиксации изображений, проиллюстрированного на фиг. 1A. На фиг. 2, Out_Amp обозначает сигнал, выводимый посредством модуля 20 усиления. Vr1 и Vr2 обозначают опорные сигналы, выводимые посредством модуля 25 подачи опорных сигналов. Опорный сигнал Vr1 служит в качестве первого опорного сигнала, потенциал которого изменяется на первую величину в единицу времени. Опорный сигнал Vr2 служит в качестве второго опорного сигнала, потенциал которого изменяется на вторую величину в единицу времени, причем вторая величина превышает первую величину. Vr_Cmp обозначает опорный сигнал, выводимый в схему 301 компаратора в качестве результата выбора селекторной схемой 302 одного из опорных сигналов Vr1 и Vr2. CMP обозначает сигнал результата сравнения, который указывает результат, полученный посредством схемы 301 компаратора посредством сравнения сигнала Out_Amp с опорным сигналом Vr_Cmp. S1 обозначает сигнал для управления проводимостью переключателя 303. Высокий уровень (в дальнейшем в этом документе, называемый H-уровнем) активирует проводимость переключателя 303. Когда сигнал F_En задается равным H-уровню, запоминающее устройство 501 флагов хранит сигнал CMP результата сравнения. Первое запоминающее устройство 502 хранит сигнал значения счетчика, когда значение сигнала для сигнала CMP результата сравнения изменяется в состоянии, в котором сигнал M1_En имеет H-уровень. Второе запоминающее устройство 503 хранит сигнал значения счетчика, когда значение сигнала для сигнала CMP результата сравнения изменяется в состоянии, в котором сигнал M2_En имеет H-уровень.

[0033] Во время t1 сигнал CMP результата сравнения и сигналы S1, F_En, M1_En и M2_En имеют низкий уровень (в дальнейшем в этом документе, называемый L-уровнем). Сигнал SEL выбора имеет H-уровень.

[0034] Во время t2 пиксель 1 выводит шумовой сигнал. Модуль 20 усиления выводит сигнал, полученный посредством усиления шумового сигнала.

[0035] Во время t3, модуль 25 подачи опорных сигналов начинает изменение потенциала опорного сигнала Vr1 во времени. Когда сигнал SEL выбора имеет H-уровень, селекторная схема 302 выводит опорный сигнал Vr1, из опорных сигналов Vr1 и Vr2, в схему 301 компаратора. Кроме того, TG 70 задает сигнал M2_En равным H-уровню.

[0036] Во время t4, соотношение абсолютных величин между сигналом Out_Amp, выводимым посредством модуля 20 усиления, и опорным сигналом Vr_Cmp меняется на противоположное, и, следовательно, изменяется значение сигнала для сигнала CMP результата сравнения. В это время второе запоминающее устройство 503 хранит сигнал значения счетчика.

[0037] Во время t5 модуль 25 подачи опорных сигналов прекращает изменение потенциала опорного сигнала Vr1 во времени и возвращает потенциал опорного сигнала Vr1 к потенциалу времени t3. Кроме того, TG 70 задает сигнал M2_En равным L-уровню.

[0038] Во время t6 пиксель 1 выводит сигнал фотоэлектрического преобразования. Модуль 20 усиления выводит сигнал, полученный посредством усиления сигнала фотоэлектрического преобразования, в схему 301 компаратора.

[0039] Во время t7 модуль 25 подачи опорных сигналов задает потенциал опорного сигнала Vr1 равным потенциалу порогового сигнала VREF. Потенциал порогового сигнала VREF почти равен потенциалу опорного сигнала Vr1, во время t11, описанное ниже. Если сигнал Out_Amp, выводимый посредством модуля 20 усиления, превышает пороговый сигнал VREF, схема 301 компаратора выводит сигнал CMP результата сравнения для L-уровня. Наоборот, если пороговый сигнал VREF превышает сигнал Out_Amp, выводимый посредством модуля 20 усиления, схема 301 компаратора выводит сигнал CMP результата сравнения H-уровня. Здесь, описание приводится при условии, что сигнал CMP результата сравнения, выводимый посредством схемы 301 компаратора имеет L-уровень. TG 70 задает сигнал S1 равным H-уровню. Следовательно, сигнал CMP результата сравнения для L-уровня времени t7 выводится в качестве сигнала SEL выбора в селекторную схему 302. Селекторная схема 302 выбирает опорный сигнал, который должен быть выведен в схему 301 компаратора во время и после времени t9, в соответствии со значением сигнала для сигнала SEL выбора времени t7. Описывается взаимосвязь между работой селекторной схемы 302 и значением сигнала для сигнала SEL выбора от времени t7 до времени t9. После того, как сигнал SEL выбора переключается на L-уровень во время t7, селекторная схема 302 продолжает выводить опорный сигнал Vr1 в схему 301 компаратора от времени t7 до времени t8. Селекторная схема 302 выбирает опорный сигнал, который должен быть выведен во время и после времени t9, в соответствии со значением сигнала для сигнала SEL выбора. Кроме того, во время t7 TG 70 задает сигнал F_En равным H-уровню. Следовательно, запоминающее устройство 501 флагов хранит сигнал CMP результата сравнения времени t7, т.е. сигнал CMP результата сравнения для L-уровня.

[0040] Во время t8 модуль 25 подачи опорных сигналов возвращает потенциал опорного сигнала Vr1 к потенциалу времени t3. Кроме того, TG 70 задает сигнал F_En равным L-уровню.

[0041] Во время t9, модуль 25 подачи опорных сигналов начинает изменение потенциалов опорных сигналов Vr1 и Vr2 во времени. Селекторная схема 302 выводит опорный сигнал Vr2 в схему 301 компаратора в соответствии с сигналом SEL выбора L-уровня. TG 70 задает сигнал M1_En равным H-уровню.

[0042] Во время t10, соотношение абсолютных величин между сигналом Out_Amp, выводимым посредством модуля 20 усиления, и опорным сигналом Vr_Cmp меняется на противоположное, и, следовательно, изменяется значение сигнала для сигнала CMP результата сравнения. В это время первое запоминающее устройство 502 хранит сигнал значения счетчика.

[0043] Во время t11 модуль 25 подачи опорных сигналов прекращает изменение потенциалов опорных сигналов Vr1 и Vr2 во времени и возвращает потенциал опорного сигнала Vr1 к потенциалу времени t3. TG 70 задает сигнал M1_En равным L-уровню.

[0044] После времени t11 схема 60 горизонтального сканирования последовательно выполняет сканирование в отношении запоминающего устройства 50 на основе столбцов, с тем чтобы инструктировать цифровым сигналам, хранимым во запоминающих устройствах 501 флагов, первых запоминающих устройствах 502 и вторых запоминающих устройствах 503 в соответствующих столбцах, выводиться в DSP 80.

[0045] Ссылаясь далее на фиг. 3A, описывается работа модуля 801 сдвига уровня DSP 80. На фиг. 3A, DN обозначает цифровой сигнал, хранимый посредством второго запоминающего устройства 503. DS-1 обозначает цифровой сигнал, хранимый посредством первого запоминающего устройства 502 и полученный посредством сравнения сигнала Out_Amp, выводимого посредством модуля 20 усиления, с опорным сигналом Vr1. DS2 обозначает цифровой сигнал, хранимый посредством первого запоминающего устройства 502 в столбце, отличающемся от столбца первого запоминающего устройства 502, которое хранит вышеуказанный цифровой сигнал DS-1, и полученный посредством сравнения сигнала Out_Amp, выводимого посредством модуля 20 усиления, с опорным сигналом Vr2. Цифровой сигнал, хранимый посредством второго запоминающего устройства 503, имеет длину в 10 битов, тогда как цифровой сигнал, хранимый посредством первого запоминающего устройства 502, имеет длину в 12 битов. Фиг. 3A иллюстрирует пример, в котором величина изменения потенциала опорного сигнала Vr2 в единицу времени в четыре раза превышает величину изменения потенциала опорного сигнала Vr1. Соответственно, необходимо инструктировать цифровому сигналу DS-2 иметь значение сигнала, которое в четыре раза превышает значение сигнала для цифрового сигнала DS-1. Поскольку Log24=2, биты цифрового сигнала DS-2 сдвигаются к MSB-стороне на два бита с тем, чтобы формировать сигнал ED_DS-2. S-N-модуль 804 вычитает цифровой сигнал DN из цифрового сигнала DS-1, задает значения сигналов Data 12 и Data 13 равными нулю с тем, чтобы формировать 14-битовый сигнал, и выводит 14-битовый сигнал в выходную схему 90. S-N-модуль 804 также задает значения сигналов Data 0 и Data 1 цифрового сигнала ED_DS-2 равными нулю и затем вычитает цифровой сигнал DN из результирующего сигнала. Таким образом, цифровой сигнал, выводимый из DSP 80, становится 14-битовым сигналом, состоящим из Data 0-Data 13. Следует отметить, что то, какой из опорных сигналов Vr1 и Vr2 использован для того, чтобы получать цифровой сигнал, хранимый посредством первого запоминающего устройства 502, может быть определено на основе сигнала, хранимого посредством запоминающего устройства 501 флагов. В частности, что касается операции, проиллюстрированной на фиг. 2, если сигнал, хранимый посредством запоминающего устройства 501 флагов, имеет H-уровень, сигнал, хранимый посредством первого запоминающего устройства 502, является сигналом, полученным с использованием опорного сигнала Vr1. Аналогично, если сигнал, хранимый посредством запоминающего устройства 501 флагов, имеет L-уровень, сигнал, хранимый посредством первого запоминающего устройства 502, является сигналом, полученным с использованием опорного сигнала Vr2.

[0046] Ссылаясь на фиг. 3B, дополнительно описываются операции модуля 25 подачи опорных сигналов и счетчика 40. Фиг. 3B является принципиальной схемой, иллюстрирующей случаи, в которых сигнал Out_Amp, имеющий определенное значение сигнала, сравнивается с опорными сигналами Vr1 и Vr2. Во время t20, модуль 25 подачи опорных сигналов начинает изменение потенциалов опорных сигналов Vr1 и Vr2 во времени. Предполагается, что счетчик 40 начинает подсчет синхросигнала во время t21, которое находится после начала изменения потенциалов опорных сигналов Vr1 и Vr2.

[0047] Когда сигнал Out_Amp сравнивается с опорным сигналом Vr2, сигнал CMP результата сравнения изменяется во время t22. Когда сигнал Out_Amp сравнивается с опорным сигналом Vr1, сигнал CMP результата сравнения изменяется во время t23. Во время t24 модуль 25 подачи опорных сигналов прекращает изменение потенциалов опорных сигналов Vr1 и Vr2 во времени, и счетчик 40 прекращает подсчет синхросигнала.

[0048] Теперь описывается цифровой сигнал, хранимый посредством первого запоминающего устройства 502. Сначала описывается случай использования опорного сигнала Vr1. Период L1 от момента, когда потенциал опорного сигнала Vr1 начинает изменяться во времени, до момента, когда изменяется значение сигнала для сигнала CMP результата сравнения, выражается следующим образом:

L1=t23-t20 (1).

[0049] Период LS1 от момента, когда счетчик 40 начинает подсчет синхросигнала, до момента, когда изменяется значение сигнала для сигнала CMP результата сравнения, выражается следующим образом:

LS1=t23-t21 (2).

[0050] Дополнительно, период L0 от момента, когда потенциал опорного сигнала Vr1 начинает изменяться во времени, до момента, когда счетчик 40 начинает подсчет, выражается следующим образом:

L0=t21-t20 (3).

[0051] Период LS1 выражается с использованием периодов L1 и L0 следующим образом:

LS1=L1-L0 (4).

[0052] Сигнал значения счетчика, соответствующий периоду LS1, является цифровым сигналом, сформированным с использованием опорного сигнала Vr1.

[0053] Аналогично, описывается случай использования опорного сигнала Vr2. Период L2 от момента, когда потенциал опорного сигнала Vr2 начинает изменяться во времени, до момента, когда изменяется значение сигнала для сигнала CMP результата сравнения, выражается следующим образом:

L2=t22-t20 (5).

[0054] Период LS2 от момента, когда счетчик 40 начинает подсчет синхросигнала, до момента, когда изменяется значение сигнала для сигнала CMP результата сравнения, выражается следующим образом:

LS2=t22-t21 (6).

[0055] Период LS2 выражается с использованием периодов L2 и L0 следующим образом:

LS2=L2-L0 (7).

[0056] Сигнал значения счетчика, соответствующий периоду LS2, является цифровым сигналом, сформированным с использованием опорного сигнала Vr2.

[0057] В данном документе предполагается, что величина изменения потенциала опорного сигнала Vr2 в единицу времени в четыре раза превышает величину изменения потенциала опорного сигнала Vr1. В этом случае, соотношение:

L1=4×L2 (8)

сохраняется между периодами L1 и L2.

[0058] Как проиллюстрировано на фиг. 3A, биты цифрового сигнала, сформированного с использованием опорного сигнала Vr2, сдвигаются к MSB-стороне на два бита. Результирующий цифровой сигнал имеет значение сигнала, эквивалентное сигналу значения счетчика, который получается в течение периода, в четыре раза превышающего период LS2. Период 4LS2 выражается с использованием периодов LS1 и L0 следующим образом:

4LS2=4L2-4L0=L1-4L0=LS1-3L0 (9).

[0059] На фиг. 3B, сигнал, имеющий определенное значение сигнала, выводимый посредством модуля 20 усиления, преобразуется в цифровые сигналы с использованием опорных сигналов Vr1 и Vr2. Таким образом, сигнал, возникающий в результате сдвига цифрового сигнала, полученного с использованием опорного сигнала Vr2, к MSB-стороне на два бита в идеале имеет значение сигнала, равное значению сигнала для цифрового сигнала, полученного с использованием опорного сигнала Vr1. Тем не менее, как указано посредством уравнения (9), когда время, в которое опорные сигналы Vr1 и Vr2 начинают изменяться во времени, отличается от времени, в которое счетчик 40 начинает подсчет синхросигнала, вызывается смещение 3L0.

[0060] Это смещение описывается с использованием фиг. 4A. Фиг. 4A иллюстрирует цифровой сигнал, выводимый посредством DSP 80 в случае, если не выполняется коррекция согласно первому варианту осуществления (описан ниже). Ссылаясь на фиг. 4A, горизонтальная ось обозначает количество света, которое падает на часть фотоэлектрического преобразования пикселя 1, тогда как вертикальная ось обозначает значение цифрового сигнала, выводимого посредством DSP 80. Кроме того, (X) обозначает цифровой сигнал, полученный, когда аналого-цифровое преобразование выполняется с использованием опорного сигнала Vr1, тогда как (Y) обозначает цифровой сигнал, полученный, когда аналого-цифровое преобразование выполняется с использованием опорного сигнала Vr2. I-L обозначает диапазон, для которого сигнал Out_Amp, выводимый посредством модуля 20 усиления, сравнивается с опорным сигналом Vr1. I-H обозначает диапазон, для которого сигнал Out_Amp, выводимый посредством модуля 20 усиления, сравнивается с опорным сигналом Vr2. IO обозначает границу между диапазонами I-L и I-H. График в виде сплошной линии обозначает взаимосвязь между количеством падающего света и цифровым сигналом, сформированным через аналого-цифровое преобразование с использованием опорного сигнала Vr1 в диапазоне I-L и опорного сигнала Vr2 в диапазоне I-H. График в виде пунктирной линии обозначает взаимосвязь между количеством падающего света и цифровым сигналом, сформированным через аналого-цифровое преобразование с использованием опорного сигнала Vr1 в диапазоне I-H. Смещение 3L0 вызывается при количестве света на границе IO между диапазонами I-L и I-H. В первом варианте осуществления, операция коррекции выполняется для того, чтобы уменьшать разность между значениями сигналов для цифровых сигналов (X) и (Y) для определенного количества падающего света.

[0061] Фиг. 4B является схемой, иллюстрирующей операцию коррекции согласно первому варианту осуществления. В течение периода операции коррекции, проиллюстрированной на фиг. 4B, пиксель 1 выводит шумовой сигнал.

[0062] Во время t30 сигнал SEL выбора имеет H-уровень, а сигналы M1_En и M2_En имеют L-уровень.

[0063] Во время t31, модуль 25 подачи опорных сигналов начинает изменение потенциала опорного сигнала Vr1 во времени. Кроме того, TG 70 задает сигнал M2_En равным H-уровню. Во время t32, которое находится после времени t30 на период L0, счетчик 40 начинает подсчет синхросигнала.

[0064] Во время t33, изменяется значение сигнала для сигнала CMP результата сравнения. В это время второе запоминающее устройство 503 хранит сигнал значения счетчика. Этот сигнал значения счетчика, хранимый посредством второго запоминающего устройства 503, упоминается в качестве цифрового сигнала DN1. Цифровой сигнал DN1 служит в качестве первого цифрового сигнала, сформированного посредством модуля 110 аналого-цифрового преобразования на основе сигнала CMP результата сравнения, который выводится посредством модуля 30 сравнения в качестве результата сравнения первого аналогового сигнала с первым опорным сигналом.

[0065] Во время t34 модуль 25 подачи опорных сигналов прекращает изменение потенциала опорного сигнала Vr1 во времени.

[0066] В течение периода от времени t34 до времени t35, сигнал SEL выбора изменяется с H-уровня на L-уровень.

[0067] Во время t35, модуль 25 подачи опорных сигналов начинает изменение потенциала опорного сигнала Vr2 во времени. Кроме того, TG 70 задает сигнал M1_En равным H-уровню. Во время t36, которое находится после времени t35 на период L0, счетчик 40 начинает подсчет синхросигнала.

[0068] Во время t37, изменяется значение сигнала для сигнала CMP результата сравнения. В это время первое запоминающее устройство 502 хранит сигнал значения счетчика. Этот сигнал значения счетчика, хранимый посредством первого запоминающего устройства 502, упоминается в качестве цифрового сигнала DN2. Цифровой сигнал DN2 служит в качестве второго цифрового сигнала, сформированного посредством модуля 110 аналого-цифрового преобразования на основе сигнала CMP результата сравнения, который выводится посредством модуля 30 сравнения в качестве результата сравнения первого аналогового сигнала со вторым опорным сигналом.

[0069] Во время t38 модуль 25 подачи опорных сигналов прекращает изменение потенциала опорного сигнала Vr2 во времени.

[0070] Далее описывается работа модуля 802 извлечения значений коррекции.

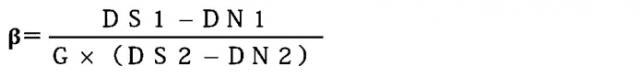

[0071] Модуль 801 сдвига уровня сдвигает биты цифрового сигнала DN2, хранимого посредством первого запоминающего устройства 502, к MSB-стороне на два бита. Результирующий цифровой сигнал DN2, полученный посредством битового сдвига к MSB-стороне на два бита, затем выводится в модуль 802 извлечения значений коррекции. Модуль 802 извлечения значений коррекции извлекает значение α коррекции с использованием нижеприведенного уравнения (10):

α=DN1-4×DN2 (10),

где DN1 обозначает значение сигнала для цифрового сигнала DN1, а 4×DN2 обозначает значение сигнала для цифрового сигнала, полученное посредством сдвига битов цифрового сигнала DN2 к MSB-стороне на два бита.

[0072] Модуль 802 извлечения значений коррекции выводит извлеченное значение α коррекции в модуль 803 вычисления коррекции. Биты цифрового сигнала, хранимого посредством первого запоминающего устройства 502 в столбце, в кото