Цифровой вычислительный синтезатор частотно-модулированных сигналов

Иллюстрации

Показать всеИзобретение относится к электронно-вычислительной технике и радиотехнике. Технический результат заключается в повышении быстродействия и возможности формирования многочастотных частотно-модулированных сигналов. Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит: эталонный генератор, блок формирования и задержки, три регистра памяти, четыре цифровых накопителя, делитель с переменным коэффициентом деления, два функциональных преобразователя код x - sin x, два инверсных фильтра sin х/х, коммутатор, два цифроаналоговых преобразователя. Цифровыми входами ЦВС ЧM сигналов являются входы первого, второго и третьего регистров памяти, а его аналоговыми выходами являются выходы первого и второго ЦАП. 2 ил.

Реферат

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для формирования многочастотных частотно-модулированных сигналов и может использоваться в радиолокации, навигации и современных системах связи.

Известны цифровые синтезаторы частотно- и фазомодулированных сигналов, содержащие эталонный генератор, блок задержки, блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь (ЦАП), фильтр нижних частот, ждущий мультивибратор, реверсивный счетчик с предварительной установкой, схему сравнения [1].

Наиболее близким техническим решением (прототипом) является цифровой синтезатор) частотно- и фазомодулированных сигналов, содержащий эталонный генератор, блок задержки, первый регистр памяти, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, сумматор, преобразователь кодов, ЦАП, фильтр нижних частот, третий регистр памяти, делитель частоты с переменным коэффициентом деления, четвертый регистр памяти, третий цифровой накопитель [2].

Однако у известных цифровых синтезаторов нет возможности формирования многочастотных частотно-модулированных сигналов.

Положительный эффект - повышение быстродействия и возможность формирования многочастотных частотно-модулированных сигналов - достигается за счет того, что в цифровой вычислительный синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый, второй и третий регистры памяти, выход последнего подключен к входу делителя с переменным коэффициентом деления; первый, второй и третий цифровые накопители; первый цифроаналоговый преобразователь (ЦАП); цифровым входом ЦВС является вход третьего регистра памяти; выход делителя с переменным коэффициентом деления подключен к входу последовательного переноса первого цифрового накопителя, а выходы блока формирования и задержки подключены к тактовым входам первого, второго и третьего цифровых накопителей и первого ЦАП, причем новым является то, что введены последовательно соединенные первый функциональный преобразователь и первый инверсный sin х/х фильтр; последовательно соединенные второй функциональный преобразователь и второй инверсный sin х/х фильтр; коммутатор; выходы первого и второго инверсных sin х/х фильтров подключены к первому и второму входам коммутатора соответственно, вход коммутации которого подсоединен с выходом блока формирования и задержки; второй ЦАП, вход которого подключен ко второму выходу коммутатора, а первый выход коммутатора подключен к входу первого ЦАП; выходы блока формирования и задержки подключены к тактовым входам четвертого цифрового накопителя и второго ЦАП; выход делителя с переменным коэффициентом деления подключен к входу последовательного переноса третьего цифрового накопителя; цифровыми входами ЦВС являются входы первого и второго регистров памяти, а его аналоговыми выходами являются выходы первого и второго ЦАП.

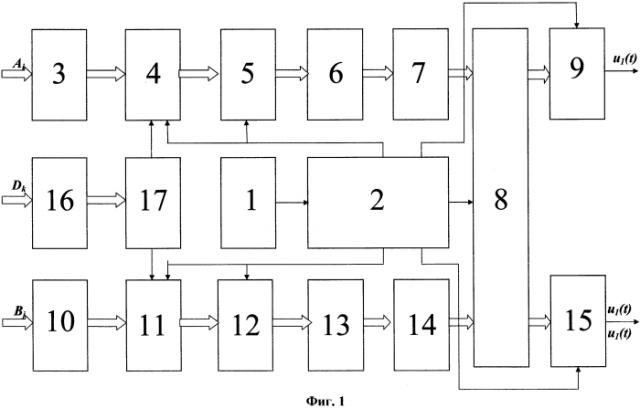

На фиг. 1 приведена структурная схема ЦВС частотно-модулированных сигналов.

Цифровой вычислительный синтезатор частотно-модулированных сигналов (по фиг. 1) содержит эталонный генератор 1, блок формирования и задержки 2 первый регистр памяти 3, первый и второй цифровые накопители 4 и 5, первый функциональный преобразователь код x - sin x 6, первый инверсный sin х/х фильтр 7, коммутатор 8 первый ЦАП 9, второй регистр памяти 10, третий и четвертый цифровые накопители 11 и 12, второй функциональный преобразователь код x - sin x 13, первый инверсный sin х/х фильтр 14, второй ЦАП 15, третий регистр памяти 16, делитель с переменным коэффициентом деления 17. Цифровыми входами ЦВС 4M сигналов являются входы первого, второго и третьего регистров памяти, а его аналоговыми выходами являются выходы первого и второго ЦАП.

ЦВС содержит последовательно соединенные эталонный генератор 1, блок формирования и задержки 2; последовательно соединенные первый регистр памяти 3, первый и второй цифровые накопители 4 и 5, первый функциональный преобразователь код x - sin x 6, первый инверсный sin х/х фильтр 7, первый вход коммутатора 8, первый выход которого соединен с информационным входом первого ЦАП 9; последовательно соединенные второй регистр памяти 10, третий и четвертый цифровые накопители 11 и 12, второй функциональный преобразователь код x - sin x 13, второй инверсный sin х/х фильтр 14, второй вход коммутатора 8, второй выход последнего подключен к информационному входу второго ЦАП 15; последовательно соединенные третий регистр памяти 16 и делитель с переменным коэффициентом деления 17, выход которого подключен к входам последовательного переноса первого и третьего цифровых накопителей 4 и 11; выходы блока формирования и задержки 2 подключены к тактовым входам первого, второго, третьего и четвертого цифровых накопителей 4, 5, 11 и 12, а также тактовым входам первого и второго ЦАП 9 и 15 и управляющему входу коммутатора 8. Цифровыми входами ЦВС являются входы первого, второго и третьего регистров памяти, 3, 10, 16 а его аналоговыми выходами являются выходы первого и второго ЦАП 9 и 15.

Цифровой вычислительный синтезатор частотно-модулированных сигналов работает следующим образом.

Эталонный генератор 1 вырабатывает синусоидальный сигнал опорной частоты, из которого в блоке формирования и задержки 2 формируются последовательности прямоугольных импульсов формы «меандр», служащие для синхронизации работы основных узлов ЦВС. Они поступают на тактовые входы первого, второго, третьего и четвертого цифровых накопителей 4, 5, 11 и 12, тактовые входы первого и второго ЦАП 9 и 15 и управляющий вход коммутатора 8.

По первому тактовому импульсу в момент времени t1 код Ai записывается из первого регистра памяти 3 в первый цифровой накопитель 4, код Bj из второго регистра памяти 10 - в третий цифровой накопитель 11, код Dk из третьего регистра памяти 16 - в делитель с переменным коэффициентом деления 17. В момент t12 по второму тактовому импульсу код Ai из первого цифрового накопителя 4 записывается во второй цифровой накопитель 5, а код Bj из третьего цифрового накопителя 11 записывается в четвертый цифровой накопитель 12 Код Dk будет определять скорость изменения частоты в первом и третьем цифровых накопителях, чем больше значение кода Dk, тем ниже скорость изменения информации в первом и третьем цифровых накопителях.

Далее с каждым последующим тактовым импульсом информация в первом тактовым импульсом в первом цифровом накопителе будет изменяться по формуле

В третьем цифровом накопителе информация будет изменяться по формуле

Информация во втором и четвертом цифровых накопителях будет описываться следующими формулами:

В функциональных преобразователях 6 и 13 происходит сопоставление кодов Ф1 и Ф2 в коды sin(Ф)1 и sin (Ф2)

Далее коды sin Ф поступают через инверсные фильтры 7 и 14 на коммутатор 8, а оттуда на информационные входы первого и второго ЦАП 9, 15. Инверсные фильтры 7 и 14 служат для выравнивания АЧХ на высоких частотах.

Если ввести обозначения

f1=Ai; f2=Bj; ; T=Δt, то сигналы на выходах ЦАП можно описать следующими выражениями:

Форма сигнала на выходе первого ЦАП 9 приведена на фиг. 2. Таким образом цифровой вычислительный синтезатор формирует два двухчастотных частотно-модулированных сигнала, описываемые формулами (5) и (6).

Литература

1. Патент №2204197 Российской Федерации МПК H03L 7/18. Цифровой синтезатор частотно-модулированных сигналов / Рябов И.В., Рябов В.И., Заявл. 06.04.2001. Опубл. 10.05.2003. Бюл. №13. 5 с.

2. Патент №2358384 Российской Федерации МПК H03L 7/18. Цифровой синтезатор частотно- и фазомодулированных сигналов / Рябов И.В., Юрьев П.М. Заявл. 31.05.2007. Опубл. 10.06.2009. Бюл. №16. 6 с.

Цифровой вычислительный синтезатор (ЦВС) частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый, второй и третий регистры памяти, выход последнего подключен к входу делителя с переменным коэффициентом деления; первый, второй и третий цифровые накопители; первый цифроаналоговый преобразователь (ЦАП); цифровым входом ЦВС является вход третьего регистра памяти; выход делителя с переменным коэффициентом деления подключен к входу последовательного переноса первого цифрового накопителя, а выходы блока формирования и задержки подключены к тактовым входам первого, второго и третьего цифровых накопителей и первого ЦАП, отличающийся тем, что введены последовательно соединенные первый функциональный преобразователь и первый инверсный sin x/x фильтр; последовательно соединенные второй функциональный преобразователь и второй инверсный sin x/x фильтр; коммутатор; выходы первого и второго инверсных sin x/x фильтров подключены к первому и второму входам коммутатора соответственно, вход коммутации которого подсоединен с выходом блока формирования и задержки; второй ЦАП, вход которого подключен ко второму выходу коммутатора, а первый выход коммутатора подключен к входу первого ЦАП; выходы блока формирования и задержки подключены к тактовым входам четвертого цифрового накопителя и второго ЦАП; выход делителя с переменным коэффициентом деления подключен к входу последовательного переноса третьего цифрового накопителя; цифровыми входами ЦВС являются входы первого и второго регистров памяти, а его аналоговыми выходами являются выходы первого и второго ЦАП.