Интегрирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

258369

Союэ Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено В.XI I.1967 (№ 1201727!26-9) с присоединением заявки №вЂ”

Приоритет

Кл. 21ат, 13/04

Комитет по делам ивобретений и открытий лри Совете Министров

СССР

МПК Н 04l

УДК 621.394.662.2 (088.8) Опубликовано ОЗ.XII.1969. Бюллетень ¹ 1 за 1970

Дата опубликования описания 24.IV.1970

Автор изобретения

А. И. Захаров

Заявитель

ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

Известны интегрирующие устройства систем тактовой си нхрон изации, обеспечивающие постоянный коррекционный эффект, и устройства, обеспечивающие, пропорциональное регулиро,ван,ие.

Од пако устройства, обеспечивающие постоянный коррекционный эффект, обладая хорошей помехоустойчивостью, не обеспечивают малое время установления синфазности, а устройства с пропорциональным регул ированиевт имеют малое время установления синфазности, но неустойчивы к воздействию случайных помех.

Предлагаемое интегрирующее устройство систем тактовой синхронизации за счет введения дополнительных элементов — ячеек «Запрет» с контурами задержками — позволяет обеспечить малое время синхронизации и высокую помехоустойчивость.

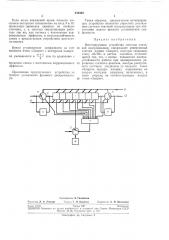

На чертеже приведена функциональная схем а предложенного устройства.

Оно содержит реверсивный счет 1 на т разрядов, ячейки 2 4 «Запрет», контуры задержки 5 и 6, логическую схему «ИЛИ» 7 на т -2 входов и датчик едвтниц 8.

На входы 9 и 10 устройства подаются импульсы с фазового дискриминатопа системы синхронизации, а с выходов 11 и 12 импульсы поступают на соответствующие входы управляющего устройства этой системы.

Датчик единиц 8, ячейка 2 «Запрет» и схема «ИЛИ» 7 служат для автоматического восстановления единицы в средней ячейке реверсивного счетчика, причем с помощью

5 схемы «ИЛИ» 7 и ячейки 2 «Запрет» осуществляется блокировка записи единицы до тех пор, пока в ячейках реверсивного счетчика и в ячейках «Запрет» 8 и 4 имеется хотя бы одна единица.

10 При наличии расхождения по фазе на один из входов устройства, например вход 9, подат -+- 1 ются импульсы. Через тактов в ячейку

15 8 «За прет» записывается единица, которая следующим тактом описывается с ячейки и выдается с выхода 11. Одновременно через контур задержюи 5 снова записывается единица в ячейку 8 «Запрет». Начиная с этого мо20 мента, на выход 11 выдаются импульсы при поступлении каждого очередного импульса на вход 9. При установлении синфазности импульс поступает на вход 10. Так как к этому входу подключена обмотка запрета ячейки

25 «Запрет» 8, то единица считывается с ячейки 8 без появления импульса íà выходе. Следовательно, со схемы «ИЛИ» 7 не поступает блокирующий импульс на ячейку «Запрет» 2 и с датчика единиц 8 записьввается единица в

30 среднюю ячейку реверсивного счетчика.

258369

Предмет изобретения

Составитель Э. Гилинская

Редактор Л. А, Утехина Техр д Т. П. Курилко Корректор А. П. Васильева

Заказ 37/6 Тираж 499 Подппсвос

ЦНИИПИ Комитета по делам изобретсппй и открьгпш при Совете Министров СССР

Москва Я-35, Раушская иао., д. 4, 5

Типография, пр. Сапунова, 2

Если из-за искажений краев посылок импульсы поступают попеременно на вход 9 и 10, происходит движение единицы IIIQ ячейкам счетчика, т. е. система си нхронизации работает та к же, как система с постоянным коррекционным эффектом, и,помехоустойчивость схемы с предлагаемым устройством достаточно высока.

Время установления оинфазности за счет введения ячеек «Запрет» с контурами задержт - - 1 ки уменьшается в ipaa по,сравнению с

2 временем схемы с по стоян ным:коррюкционным эффектом.

Применение предлагаемого устройства не требует усложнения фазового дискриминатора.

Таким образом, предлагаемое интегрирующее устройство позволяет упростить реализац|ию системы тактовой синхронизации при обеспечении,малого в ремени установления син5 ф азности.

Интегрирующее устройство системы такто10 вой синхронизации, содержащее реверсивный счетчик ячейки «Запрет», .контуры задержки, схему «ИЛИ» и датчик «единиц», отличаюи4ееся тем, что, с целью повышения помехоустойчивости работы при одновременном у1п15 рощении схемного решения, выходы реверсивного счетчика соединены со входами ячеек

«Запрет», выходы кото рых подключены ко входам контуров задержки, включенных, в свою очередь, на соответствующих входах

20 ячеек «3 апрет».