Сбор сведений о ходе вычислений

Иллюстрации

Показать всеИзобретение относится к сфере обработки в вычислительной среде, в частности к сфере сбора сведений о ходе выполнения команд программы в вычислительной среде. Технический результат заключается в повышении производительности процессора. Технический результат достигается за счет процессора, который собирает информацию, относящуюся к выполняемому потоку команд. На основе собранной информации формируются записи средства сбора сведений о ходе вычислений. В выполняемом процессором потоке команд выявляется точка выборки средства сбора сведений о ходе вычислений. В программном буфере средства сбора сведений о ходе вычислений сохраняется отчетная группа. Это сохранение включает: определение значения текущего адреса указанного программного буфера средства сбора сведений о ходе вычислений, основанное на доступных команде управляющих параметрах средства сбора сведений о ходе вычислений; и собственно сохранение указанной отчетной группы в указанном программном буфере средства сбора сведений о ходе вычислений, основанное на начальном адресе и указанном текущем адресе программного буфера средства сбора сведений о ходе вычислений, причем отчетная группа содержит указанные сформированные записи средства сбора сведений о ходе вычислений. 3 н. и 17 з.п. ф-лы, 22 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к сфере обработки в вычислительной среде. В частности, изобретение относится к сфере сбора сведений о ходе выполнения команд программы в вычислительной среде.

Уровень техники

Процессоры компьютеров выполняют транзакции с использованием непрерывно усложняющейся логики предсказания ветвлений и кэширования (т.е. буферизации) команд. Эти приемы применяются для повышения скорости выполнения команд, благодаря чему повышается производительность вычислительных систем. Применение предсказания ветвлений и кэширования для повышения производительности затрудняет достоверное предсказание того, как именно процессором компьютера будет выполняться конкретная программа-приложение. При разработке программного обеспечения часто существует баланс между функциональностью и производительностью. Программное обеспечение выполняется на одном или более уровнях абстрагирования от применяемого в вычислительной системе аппаратного обеспечения, на котором выполняется программное обеспечение. И если аппаратное обеспечение виртуализируется, то вводится еще один уровень абстракции. С введением указанной логики, повышающей производительность, а также различных уровней абстракции становится сложно сформировать целостное понимание того, что в действительности происходит на уровне аппаратного обеспечения при выполнении программного обеспечения. При отсутствии этих сведений разработчики программного обеспечения для оптимизации программ-приложений применяют более абстрактные методы, например увеличивают продолжительность выполнения, изменяют режим использования запоминающего устройства, число потоков и т.п.

Раскрытие изобретения

Техническая проблема

Если специфическая информация на уровне аппаратного обеспечения доступна, то она обычно предоставляется разработчику постфактум и в совокупности, на высоком уровне и/или вперемешку со сведениями об активности других программ и операционной системы, что затрудняет идентификацию потенциальных проблем, которые могут повлиять на эффективность и точность программы-приложения.

Решение технической проблемы

Варианты осуществления содержат компьютерный программный продукт, способ и систему для сбора сведений о ходе вычислений. Процессор выполняет поток команд (т.е. непрерывную последовательность команд). Процессором собирается информация о ходе выполнения вычислений, характеризующая выполнение потока команд. На основе указанных зафиксированных сведений о ходе вычислений создаются записи о ходе вычислений. В процессоре выявляется точка (т.е. момент) выборки средства сбора сведений о ходе вычислений для выполняемой последовательности команд, сохраняется отчетная группа записей в программном буфере средства сбора сведений о ходе вычислений. Сохранение основывается на выявленной точке выборки средства сбора сведений о ходе вычислений и включает: определение текущего адреса программного буфера средства сбора сведений о ходе вычислений, причем определение зависит от доступных командам управляющих параметров средства сбора сведений о ходе вычислений; запись отчетной группы в программный буфер средства сбора сведений о ходе вычислений на основе начального адреса и текущего адреса программного буфера средства сбора сведений о ходе вычислений, причем отчетная группа содержит созданные записи о ходе вычислений.

С помощью приемов, составляющих сущность настоящего изобретения, реализуются дополнительные особенности и преимущества. В данной заявке подробно описываются прочие варианты осуществления и аспекты настоящего изобретения, они рассматриваются как часть настоящего изобретения. Для лучшего понимания сущности изобретения, его преимуществ и особенностей приводится описание и чертежи.

Краткое описание чертежей

В формуле изобретения, следующей за описанием, сформулированы и заявлены объекты изобретения. Вышеупомянутые и прочие объекты, особенности и преимущества настоящего изобретения раскрываются в последующем подробном описании, которое сопровождается чертежами. На чертежах показано:

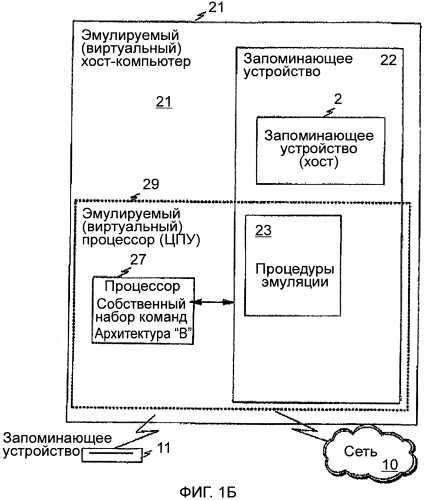

на фиг. 1А - схема примера хост-компьютерной системы согласно варианту осуществления изобретения,

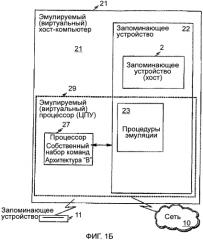

на фиг. 1Б - схема примера хост-компьютерной системы с эмуляцией согласно варианту осуществления изобретения,

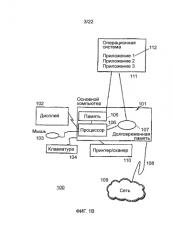

на фиг. 1B - схема примера компьютерной системы согласно варианту осуществления изобретения,

на фиг. 2 - схема примера компьютерной сети согласно варианту осуществления изобретения,

на фиг. 3 - схема элементов компьютерной системы согласно варианту осуществления изобретения,

на фиг. 4А - схема фрагмента компьютерной системы с детализацией элементов согласно варианту осуществления изобретения,

на фиг. 4Б - схема фрагмента компьютерной системы с детализацией элементов согласно варианту осуществления изобретения,

на фиг. 4B - схема фрагмента компьютерной системы с детализацией элементов согласно варианту осуществления изобретения,

на фиг. 5 - схема примера системы для сбора сведений о ходе вычислений в процессоре согласно варианту осуществления изобретения,

на фиг. 6 - схема фрагмента управляющего блока управляющих параметров средства сбора сведений о ходе вычислений (от англ.: Run-time-instrumentation Controls Control Block, аббревиатура RICCB) согласно варианту осуществления изобретения, содержащая управляющие параметры, значение которых может устанавливаться в привилегированном режиме,

на фиг. 7 - схема фрагмента блока параметров RICCB согласно варианту осуществления изобретения в случае, когда значение разряда "К" режима частичных привилегий установлено равным единице,

на фиг. 8 - схема накопительного буфера согласно варианту осуществления изобретения,

на фиг. 9 - схема отчетной группы согласно варианту осуществления изобретения,

на фиг. 10 - схема варианта осуществления записи типа начало в отчетной группе,

на фиг. 11 - схема варианта осуществления записи типа отметка времени в отчетной группе,

на фиг. 12 - схемы вариантов осуществления записи типа извлечение в отчетной группе,

на фиг. 13 - схемы вариантов осуществления записи типа останов в отчетной группе,

на фиг. 14 - схемы вариантов осуществления записей типа вызов в отчетной группе,

на фиг. 15 - схема варианта осуществления записи типа заполнитель в отчетной группе,

на фиг. 16 - схемы вариантов осуществления записей типа команда в отчетной группе,

на фиг. 17 - схема алгоритма сбора сведений о ходе вычислений согласно варианту осуществления изобретения,

на фиг. 18 - графическое представление компьютерного программного продукта согласно варианту осуществления изобретения.

Осуществление изобретения

Вариант осуществления настоящего изобретения представляет собой основанное на аппаратном обеспечении средство сбора сведений о ходе вычислений для сред выполнения задач. В данном случае термин "среда выполнения задач" относится к среде, которая инкапсулирует состояние и управляет ресурсами, используемыми для выполнения программы или приложения (например, виртуальная машина Java®, операционная система, программное обеспечение промежуточного слоя и т.д.). Варианты осуществления средства сбора сведений о ходе вычислений позволяют некоторой программе собирать информацию о ходе выполнения команд программного обеспечения, в том числе собирать данные центрального процессорного устройства (ЦПУ). Собранная информация позволяет программе отслеживать внутренние процессы, связанные с исполняемым программным обеспечением. Варианты осуществления средства сбора сведений о ходе вычислений содержат аппаратное средство для сбора сведений о последовательностях событий (например, переходы при ветвлениях, значения регистров и т.д.) в накопительном буфере. Содержимое накопительного буфера (или части накопительного буфера, содержащей наиболее свежие записи) копируется в программный буфер в пространстве адресов приложения (например, в пространстве адресов виртуальной машины Java) при возникновении программируемого набора типовых инициирующих событий, таких как (но не ограничиваясь): директива программного обеспечения в форме команды, вставленной в поток команд; завершение выполнения некоторого числа команд; окончание заданного интервала времени после последней выборки; заданное событие в аппаратном обеспечении, такое как возникновение промаха кэш-памяти данных или промаха кэш-памяти команд (т.е. отсутствие требуемых данных или команд в кэш-памяти).

Данные, регистрируемые в каждой точке выборки, сохраняются как набор реляционных записей, для обозначения которого в данной заявке используется термин "отчетная группа". Отчетная группа сохраняется в программном буфере, местоположение которого определяется по значениям управляющих параметров средства сбора сведений о ходе вычислений. Таким образом, данные о ходе вычислений, хранящиеся в виде отчетной группы в программном буфере, доступны программе для анализа при постобработке или даже для более агрессивного анализа во время действия средства сбора сведений о состоянии вычислительной системы.

Информацию о ходе вычислений, например собранную основанным на аппаратном обеспечении средством сбора сведений о ходе вычислений, описанным в настоящей заявке, могут использовать динамические компиляторы для оптимизации в реальном масштабе времени на основе обратной связи с программой. Например, динамическим компилятором для выполнения оптимизации, которая делает код специализированным или создает версию (т.е. вариант) кода, определяет потоки, меняет порядок следования выполняемых фрагментов и корректирует ветвления, может использоваться информация о следовании важным ветвям выполнения, о профильных величинах и предпочтительных направлениях ветвления. Варианты осуществления, описанные в настоящей заявке, не ограничиваются использованием компиляторами и могут применяться в различных задачах, например (но не ограничиваясь) для управления другими средствами выполнения программ. Например, сведения о событиях кэш-памяти данных могут использоваться для содействия процедуре определения ненужных данных в принятии решений о совместно размещенных или размещенных раздельно объектах, что позволяет добиться лучшего размещения данных или позволяет избежать мнимых проблем совместного использования данных.

На фиг. 1А показаны характерные компоненты хост-компьютерной системы 50 согласно варианту осуществления изобретения. В компьютерной системе могут также использоваться другие варианты конфигурации компонентов. Пример хост-компьютерной системы 50 содержит один или более процессоров 1, связанных с главным запоминающим устройством 2 компьютера (компьютерной памятью), а также через интерфейсы ввода-вывода с запоминающими устройствами 11 и сетями 10 для обмена информацией с другими компьютерами или сетями хранения данных и т.п. Процессор 1 совместим с архитектурой, имеющей собственный набор команд и собственную функциональность. Процессор 1 может использовать динамическую трансляцию адресов для преобразования программных адресов (виртуальных адресов) в реальные адреса запоминающего устройства. Как правило, средство 3 динамической трансляции адресов (СДТА) содержит буфер 7 быстрого преобразования адреса (БПА) для кэширования преобразований, благодаря чему последние обращения к запоминающему устройству 2 не приводят к задержке, вызываемой трансляцией адреса. Как правило, между запоминающим устройством 2 и процессором 1 размещается кэш-память (быстродействующее буферное запоминающее устройство) 9.

Кэш-память 9 может быть организована по иерархическому принципу, т.е. содержать больший объем кэш-памяти, доступный для двух и более ЦПУ, и также меньшие, более быстродействующие (низкоуровневые) объемы кэш-памяти, размещенные между большим объемом кэш-памяти и каждым ЦПУ. В некоторых вариантах осуществления кэш-память низкого уровня разделяется на низкоуровневую кэш-память для выборки команд и низкоуровневую кэш-память для обращения к данным. Согласно варианту осуществления изобретения команда выбирается из запоминающего устройства 2 устройством 4 выборки команд через кэш-память 9. Команда декодируется в устройстве 6 декодирования команд и направляется (в некоторых вариантах осуществления - совместно с другими командами) в устройства 8 выполнения команд. Как правило, используются различные типы устройств 8 выполнения команд, например арифметическое выполняющее устройство, устройство выполнения команд с плавающей запятой и устройство выполнения команд ветвления. Команда выполняется устройством 8 выполнения команд, обращаясь при необходимости к операндам, находящимся в определяемых командой регистрах или в запоминающем устройстве 2 компьютера. Если требуется доступ к операнду (загруженному или хранящемуся) из запоминающего устройства 2 компьютера, то доступ контролируется устройством 5 загрузки-хранения под управлением выполняемой команды. Команды могут выполняться в схемах аппаратного обеспечения или во внутреннем микрокоде (входящем в состав встроенного программного обеспечения) или комбинацией указанных способов.

На фиг. 1Б показана схема хост-компьютерной системы 21 с эмуляцией, которая эмулирует хост-компьютерную систему, построенную по хост-архитектуре, такую как хост-компьютерная система 50, схема которой показана на фиг. 1А. В хост-компьютерной системе 21 с эмуляцией хост-процессор (ЦПУ) 1 является эмулируемым хост-процессором 29 (или виртуальным хост-процессором), в его состав входит собственный процессор 27, построенный по архитектуре с собственным набором команд, отличной от архитектуры процессора 1 хост-компьютерной системы 50. Эмулируемая хост-компьютерная система 21 обладает запоминающим устройством 22, доступным собственному процессору 27. В варианте осуществления запоминающее устройство 22 разделено на части: часть, служащую запоминающим устройством 2 компьютера, и часть, служащую запоминающим устройством 23 процедур эмуляции. В соответствии с архитектурой хост-компьютера, запоминающее устройство 2 компьютера доступно программам эмулируемой хост-компьютерной системы 21.

Собственный процессор 27 выполняет собственные команды из набора команд собственной архитектуры, отличной от архитектуры эмулируемого процессора 29, причем собственные команды поступают из запоминающего устройства 23 процедур эмуляции. Собственный процессор 27 может обратиться к хост-команде из состава программы, располагающейся в запоминающем устройстве 2 компьютера, для ее исполнения путем выполнения одной или более команд, получаемых подряд, а также с использованием процедуры доступа-декодирования, которая может декодировать хост-команду (хост-команды), к которым происходит обращение, для определения процедуры в рамках собственной архитектуры для выполнения хост-команды и эмулирования функций хост-команды, к которой происходит обращение. Собственными процедурами могут эмулироваться другие возможности, определенные для архитектуры хост-компьютерной системы 50, например, такие как регистры общего назначения, управляющие регистры, динамическая трансляция адресов, поддержка подсистемы ввода-вывода и кэш-память процессора.

Для повышения производительности процедуры эмуляции могут также пользоваться преимуществами функций, предоставляемыми хост-процессором 27, такими как регистры общего назначения и динамическая трансляция виртуальных адресов. Для содействия процессору 27 в эмуляции функций хост-компьютерной системы 50 могут предоставляться специальные аппаратные и разгружающие вычислительные ядра.

Команды, присущие архитектуре компьютеров-мейнфреймов, часто используются программистами (в настоящее время, как правило, пользующимися языком программирования "С") через приложения-компиляторы. Указанные команды, хранящиеся в среде хранения информации, могут выполняться в собственной вычислительной среде на сервере, построенном по архитектуре корпорации IBM® z/Architecture, или же на вычислительных машинах, построенных по другим архитектурам. Эти команды могут эмулироваться на существующих и на будущих серверах-мейнфреймах корпорации IBM и на других вычислительных машинах IBM (например, на серверах типа pSeries® и xSystem®). Указанные команды могут выполняться на вычислительных машинах, работающих под управлением операционной системы Linux, и на обширном множестве вычислительных машин, использующих аппаратное обеспечение производства предприятий IBM®, Intel®, AMD™, Sun Microsystems и др. Помимо указанного аппаратного обеспечения с архитектурой z/Architecture, могут применяться вычислительные машины на основе операционной системы Linux, а также вычислительные машины с эмуляторами Hercules (программный эмулятор мейнфреймов IBM и совместимых), UMX, FSI (от англ. - Fundamental Software, Inc.), PSI (от англ. - Platform Solutions, Inc.), при этом выполнение обычно осуществляется в режиме эмуляции. В режиме эмуляции программа-эмулятор выполняется собственным (физическим) процессором вычислительной системы и имитирует архитектуру эмулируемого процессора.

Один или более компонентов эмулируемой хост-компьютерной системы 21 подробно описан в публикации IBM "z/Architecture Principles of Operation" (от англ. - "Принцип действия архитектуры z/Architecture", публикация IBM № SA22-7832-08, 9-е издание, август 2010 г. ), которая в качестве ссылки включена в настоящую заявку. IBM является зарегистрированным товарным знаком корпорации International Business Machines Corporation, Армонк, штат Нью-Йорк, США. Прочие наименования, используемые в настоящей заявке, могут также являться зарегистрированными или незарегистрированными товарными знаками или наименованиями товаров корпорации International Business Machines Corporation или других компаний.

Как правило, собственный процессор 27 выполняет программное обеспечение-эмулятор, хранящееся в запоминающем устройстве 23 процедур эмуляции. В состав указанного программного обеспечения-эмулятора входят программы из постоянного запоминающего устройства (ПЗУ) или собственная операционная система, необходимые для имитации эмулируемого процессора. Для архитектуры эмулируемого процессора программное обеспечение-эмулятор отвечает за выборку и выполнение команд. Программное обеспечение-эмулятор поддерживает эмулируемый программный счетчик для отслеживания границ команд. Программное обеспечение-эмулятор может в один момент времени выбирать одну или более команд в формате эмулируемой вычислительной машины и преобразовывать указанные одну или более команд в соответствующую группу команд в собственном формате хост-вычислительной машины для выполнения собственным процессором 27. Указанные преобразованные команды могут кэшироваться, благодаря чему преобразование может выполняться более быстро. Программное обеспечение-эмулятор поддерживает правила архитектуры эмулируемой процессорной архитектуры, чтобы обеспечить корректность выполнения операционной системы и приложений, предназначенных для эмулируемого процессора. Более того, программное обеспечение-эмулятор предоставляет вычислительные ресурсы, понятные для эмулируемой процессорной архитектуры, в том числе (но не ограничиваясь) управляющие регистры, регистры общего назначения, регистры с плавающей запятой, функцию динамической трансляции адресов (включая, например, таблицы сегментов и таблицы страниц), механизмы прерываний, механизмы переключения задач, часы времени суток, интерфейсы к подсистемам ввода-вывода, благодаря чему операционная система или прикладная программа, разработанные для выполнения на эмулируемом процессоре 29, могут быть выполнены на собственном (физическом) процессоре 27, оснащенном программным обеспечением-эмулятором.

Конкретная эмулируемая команда декодируется, и для выполнения функции конкретной отдельной команды вызывается соответствующая подпрограмма. Для имитации эмулируемого 29 процессора применяется функция программного обеспечения-эмулятора, например, в виде подпрограммы, написанной на языке программирования "С", либо программа-драйвер, либо используется иной способ осуществления драйвера конкретного аппаратного обеспечения, о чем специалистам в данной области станет ясно после изучения описания предпочтительного варианта осуществления.

Согласно варианту осуществления изобретения изобретение может быть осуществлено программным обеспечением (иногда называемым лицензионным внутренним кодом, содержимым ПЗУ, микрокодом, милликодом, пикокодом и т.п., причем каждый из терминов может относиться к одному или более аспектам настоящего изобретения). На фиг. 1А процессор 1 (ЦПУ) хост-компьютерной системы 50 может обращаться к коду программного обеспечения, содержащему настоящее изобретение и хранящемуся в запоминающем устройстве, таком как долговременное запоминающее устройство, привод CD-ROM (от англ. Compact Disc Read Only Memory - постоянное запоминающее устройство на компакт-диске), привод ленточного накопителя, накопитель на жестких дисках. Программный код может располагаться на любой из множества известных машиночитаемых сред, предназначенных для использования в системе обработки данных, таких как гибкий диск, накопитель на жестких дисках или CD-ROM. Код может распространяться на подобной машиночитаемой среде или поставляться пользователям из запоминающего устройства 2 компьютера или из запоминающего устройства одного компьютера через сеть 10 другим компьютерным системам для их пользователей.

Согласно другому варианту осуществления программный код может находиться в запоминающем устройстве 2 компьютера, и доступ процессора 1 к нему может осуществляться по шине процессора (на чертеже шина процессора не показана). Подобный программный код содержит операционную систему, которая управляет функционированием и взаимодействием различных компонентов компьютера и одной или более прикладных программ. Программный код обычно передается из запоминающего устройства 11 большой емкости в запоминающее устройство 2 компьютера, из которого код доступен процессору 1 для обработки. Приемы и способы размещения кода программного обеспечения в пространстве памяти запоминающего устройства, на физической машиночитаемой среде и/или передача кода программного обеспечения через сети передачи данных достаточно хорошо известны и в настоящей заявке далее обсуждаться не будут. Программный код, созданный и размещенный на материальном носителе, в том числе (но не ограничиваясь) на электронных модулях памяти [в оперативном запоминающем устройстве (ОЗУ)], запоминающих устройствах флеш-памяти, CD-ROM, DVD-ROM (от англ. Digital Video Disc Read-Only Memory - постоянное запоминающее устройство на цифровом видеодиске), магнитной ленте и т.п. часто называют компьютерным программным продуктом. Информация со среды-носителя компьютерного программного продукта обычно считывается схемой обработки предпочтительно в компьютерной системе с целью выполнения программного кода схемой обработки.

На фиг. 1B показана схема примера рабочей станции или аппаратной части сервера, в которых может быть осуществлено настоящее изобретения. На фиг. 1B система 100 содержит типичную основную компьютерную систему 101, например персональный компьютер, рабочую станцию или сервер, в состав которой, в свою очередь, могут входить периферийные устройства. Основная компьютерная система 101 содержит один или более процессоров 106 и шину передачи данных (на чертеже не показана), используемую для подключения и осуществления соединения между одним или более процессорами 106 и другими компонентами основной компьютерной системы 101 по хорошо известной методике. Шина соединяет процессор 106 с запоминающим устройством 105 и запоминающим устройством 107 длительного хранения, которое может содержать, например, дисковый накопитель (в том числе, например, любые магнитные среды хранения данных, CD-ROM, DVD-ROM или устройства флеш-памяти) или ленточный накопитель. Основная компьютерная система 101 может также содержать адаптер интерфейса пользователя, который соединяет один или более процессоров 106 через шину с одним или более интерфейсными устройствами, такими как клавиатура 104, мышь 103, принтер и/или сканер 110 и/или с устройствами интерфейса пользователя других типов, такими как сенсорный экран, устройство цифрового координатного ввода планшетного типа и т.п. Шина также обеспечивает подключение устройства 102 отображения, такого как жидкокристаллический экран или монитор, к одному или более процессорам 106 через адаптер дисплея.

Основная компьютерная система 101 может обмениваться данными с другими компьютерами или сетями компьютеров с помощью сетевого адаптера, способного осуществлять соединение 108 с сетью 109 передачи данных. Примерами сетевых адаптеров являются адаптеры сетей типа Token Ring (от англ. - маркерное кольцо) и Ethernet, а также модемы.

Согласно другому варианту осуществления, основная компьютерная система 101 может обмениваться данными с использованием беспроводного интерфейса, такого как адаптер CDPD (от англ. Cellular Digital Packet Data - цифровая пакетная передача данных по сети сотовой связи). Основная компьютерная система 101 может быть соединена с другими компьютерами в локальную вычислительную сеть (ЛВС) или в глобальную вычислительную сеть, либо система 101 может выступать в качестве клиента в системе клиент-сервер вместе с другим компьютером и т.д.

На фиг. 2 показана схема сети 200 обработки данных, в которой может быть осуществлено настоящее изобретение. Сеть 200 обработки данных может содержать набор индивидуальных сетей, таких как беспроводные и проводные сети, в состав каждой из которых может входить множество индивидуальных рабочих станций 201, 202, 203, 204 и/или основная компьютерная система 101 (см. фиг. 1B). Кроме того, специалисты в данной области техники должны понимать, что может быть задействована одна или более ЛВС, причем ЛВС может содержать набор рабочих станций, соединенных с хост-процессором.

Код 111 программного обеспечения может располагаться в запоминающем устройстве 105, и процессор 106 может обращаться к этому коду по шине процессора. Такой код программного обеспечения содержит операционную систему, которая управляет функционированием и взаимодействием различных компонентов компьютера и одной или более прикладных программ 112. Код программного обеспечения обычно передается из запоминающего устройства 107 длительного хранения в быстродействующее запоминающее устройство 105, из которого этот код доступен процессору 106 для обработки. Приемы и способы размещения кода программного обеспечения в пространстве памяти запоминающего устройства, на физической машиночитаемой среде и/или передачи кода программного обеспечения через сети передачи данных достаточно хорошо известны и в настоящей заявке далее обсуждаться не будут. Программный код, созданный и размещенный на материальном носителе, в том числе (но не ограничиваясь) на электронных модулях памяти (ОЗУ), запоминающих устройствах флеш-памяти, CD-ROM, DVD-ROM, магнитной ленте и т.п., часто называют компьютерным программным продуктом. Информация со среды-носителя компьютерного программного продукта обычно считывается схемой обработки, предпочтительно в компьютерной системе, с целью выполнения схемой обработки.

Процессору наиболее доступна кэш-память низшего уровня (т.е. первого уровня; обозначение первого уровня - L1), которая обычно обладает наибольшим быстродействием н меньшим объемом по сравнению с процессорной кэш-памятью других уровней. Уровень основного запоминающего устройства считается наивысшим (уровень 3, обозначение L3, если всего предусмотрено три уровня). Кэш-память низшего уровня часто разделяется на кэш-память команд 1-кэш (от англ. Instructions cache - кэш-память команд) для хранения предназначенных для исполнения команд и кэш-память данных D-кэш (от англ. Data cache - кэш-память данных), предназначенную для хранения операндов.

На фиг. 2 сети могут также содержать компьютеры-мейнфреймы или серверы, такие как компьютер-шлюз (клиентский сервер) 206 или сервер приложений (удаленный сервер) 208, который может обращаться к хранилищу данных и к которому может также осуществляться доступ непосредственно с рабочей станции 205. Компьютер-шлюз 206 служит точкой доступа в каждую индивидуальную сеть 207. Шлюз требуется при переходе от одного сетевого протокола на другой. Компьютер-шлюз 206 предпочтительно может быть подключен к другой сети (например, к сети 207 Интернет) с помощью канала передачи данных. Компьютер-шлюз 206 также может быть непосредственно соединен с одной или более рабочими станциями 101, 201, 202, 203 и 204 с использованием канала передачи данных. Компьютер-шлюз может быть реализован на основе сервера IBM eServer™ zSeries® z9®, предлагаемого корпорацией International Business Machines Corporation.

Согласно варианту осуществления изобретения процессор 106 основной компьютерной системы 101 может обращаться к коду программного обеспечения, в котором может быть осуществлено настоящее изобретение и который располагается на запоминающем устройстве долговременного хранения, таком как запоминающее устройство 107 долговременного хранения, схема которого показана на фиг. 1B. Код программного обеспечения для его использования системой обработки данных может располагаться на любой из множества известных машиночитаемых сред, таких как гибкий диск, накопитель на жестких дисках или CD-ROM. Код может предоставляться на такой машиночитаемой среде или может предоставляться пользователям 210 и 211 компьютерных систем по сети передачи данных из запоминающих устройств другой компьютерной системы.

На фиг. 3 показан пример осуществления процессора 106. Как правило, для буферизации блоков информации запоминающего устройства используется одноуровневая или многоуровневая кэш-память 303, что позволяет увеличить производительность процессора 106. Кэш-память 303 представляет собой быстродействующее буферное запоминающее устройство, хранящее строки данных основного запоминающего устройства, которые, вероятно, должны использоваться в будущем. Как правило, длина строк данных в кэш-памяти составляет 64, 128 или 256 байтов. Согласно варианту осуществления изобретения часто применяются отдельные функциональные узлы кэш-памяти для буферизации команд и данных. Для поддержания когерентности содержимого кэш-памяти (т.е. для синхронизации копий строк данных в основном запоминающем устройстве и в кэш-памяти) часто применяются различные хорошо известные снуп-алгоритмы (от англ. Snoop algorithm, специальный алгоритм поиска необходимых данных в кэш-памяти). Главное запоминающее устройство, такое как запоминающее устройство 105 вычислительной системы, часто также рассматривается как кэш-память. В вычислительной системе с четырьмя уровнями кэш-памяти 303 запоминающее устройство 105 иногда рассматривается как кэш-память пятого уровня (L5), поскольку оно обычно обладает более высоким быстродействием по сравнению с быстродействием большинства доступных вычислительной системе энергонезависимых запоминающих устройств (запоминающих устройств с прямым доступом, ленточных запоминающих устройств с последовательным доступом и т.п.) и хранит только часть данных указанных устройств. Основное запоминающее устройство 105 "кэширует" (буферизирует) страницы данных, которые загружаются и выгружаются из него операционной системой.

Программный счетчик (счетчик команд) 311 отслеживает адрес текущей подлежащей исполнению команды. Программный счетчик в процессоре, построенном по архитектуре z/Architecture, является 64-разрядным, его длина может быть сокращена до 31 или до 24 разрядов для поддержки предыдущих ограничений на длину адреса. Как правило, программный счетчик реализован в слове состояния программы (ССП) компьютера, так что при переключении задач его содержимое сохраняется. Так, выполнение программы при некотором значении программного счетчика может быть прервано, например, операционной системой (текущий "контекст" переключается от окружения программы к окружению операционной системы). В то время, пока программа неактивна, значение счетчика программ сохраняется в ССП программы, и при выполнении задачи операционной системы используется счетчик программ ССП операционной системы. Согласно варианту осуществления изобретения программный счетчик увеличивается на величину, равную длине в байтах исполняемой в данный момент команды. Команды типа RISC (от англ. Reduced Instruction Set Computing - вычисления с сокращенным набором команд), как правило, имеют фиксированную длину, в то время как команды типа CISC (от англ. Complex Instruction Set Computing - вычисления со сложным набором команд), как правило, имеют переменную длину. Команды в архитектуре IBM z/Architecture относятся к типу CISC, их длина составляет два, четыре или шесть байтов. Значение в программном счетчике 311 изменяется либо операцией переключения задач, либо при выполнении операции ветвления, например, по команде ветвления. При операции переключения задачи текущее значение программного счетчика сохраняется в ССП вместе с другой информацией о состоянии выполнявшейся программы (такой как коды состояния), после чего загружается новое значение программного счетчика, указывающее на команду нового программного модуля, подлежащего исполнению. Операция ветвления, используемая в программе при принятии решений или выполнении циклов, исполняется путем загрузки в программный счетчик 311 результата команды ветвления.

Согласно варианту осуществления изобретения для выборки команд по указанию процессора 106 применяется устройство 305 выборки команд. Устройство 305 выборки команд либо выбирает команду в порядке следования, либо команду, на которую указывает команда ветвления, либо по указанию о переключении задачи - первые команды программы. Согласно варианту осуществления изобретения в устройстве 305 выборки команд применяются упреждающие методы для спекулятивной выборки команд, основанные на гипотезе о том, что заблаговременно выбранные команды могут потребоваться в будущем. Например, устройство 305 выборки может загрузить 16 байтов команд, в число которых входят следующая по очереди команда и, кроме того, байты команд, следующих за ней.

Затем выбранные команды выполняются процессором 106. Согласно варианту осуществления изобретения выбранная команда (команды) передаются на устройство 306 декодирования-диспетчеризации устройства 305 выборки команд. Устройство декодирования-диспетчеризации 306 декодирует команду (команды) и передает информацию о декодированной команде (командах) на соответствующие устройства 307, 308 и/или 310. Исполнительный блок 307 принимает информацию о декодированных арифметических операциях от устройства 305 выборки команд и выполняет арифметические операции над операндами согласно коду операции команды. Операнды передаются в исполнительное устройство 307 либо из запоминающего устройства 105, либо из собственных регистров 309, либо извлекаются из внутреннего поля выполняемой команды. Результаты выполнения команды, требующие сохранения, сохраняются либо в запоминающем устройстве 105, либо в собственных регистрах 309, либо в ином аппаратном обеспечении вычислительной системы (например, в управляющих регистрах, регистрах ССП и т.п.).

Как правило, процессор 106 снабжен одним или более исполнительными устройствами 307, 308 и 310, предназначенными для выполнения указанной командой функции. На схеме, показанной на фиг. 4А, исполнительное устройство 307 может обмениваться информацией с собственными регистрами 309 общего назначения, устройством 306 декодирования-диспетчеризации, устройством 310 загрузки-хранения и другими устройствами 401 процессора с помощью интерфейсной логики 407. В исполнительном устройстве 307 могут применяться различные схемы 403, 404 и 405 регистров для временного хранения информации, предназначенной для обработки арифметическо-логическим устройством (АЛУ) 402. АЛУ 402 выполняет арифметические операции, такие как сложение, вычитание, умножение и деление, а также логические операции, такие как конъюнкция, дизъюнкция, сложение по модулю 2, сдвиг, циклический сдвиг. Согласно варианту осуществления изобретения АЛУ поддерживает специализированные операции, зависящие от особенностей архитектуры. Прочие схемы могут реализовывать другие предусмотренные арх