Команда векторного типа для поиска равнозначного элемента

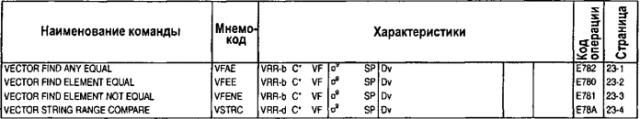

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении эффективности обработки символьных данных. Способ выполнения машинной команды в центральном процессоре, в котором принимают решение о том, содержит ли поле маски флаг поиска нуля, на основе поля маски, содержащего флаг поиска нуля, выполнение поиска во втором операнде равного нулю элемента, причем в результате предоставляют индекс равного нулю элемента, содержащий либо индекс найденного в результате поиска равного нулю элемента, либо длину вектора, если равных нулю элементов не найдено, сравнение каждого элемента второго операнда с каждым элементом третьего операнда на предмет равенства их значений, причем в результате предоставляют индекс сравнения, содержащий либо индекс найденного в результате сравнения элемента с равенством значений, либо длину вектора, если равнозначных элементов не найдено, формирование результата, причем, если поиск равного нулю элемента не выполнялся, то результат содержит индекс сравнения, если поиск равного нулю элемента выполнялся, то результат содержит минимальное из значений индекса сравнения и индекса равного нулю элемента. 3 н. и 8 з.п. ф-лы, 18 ил.

Реферат

Предпосылки создания изобретения

Настоящее изобретение относится к сфере обработки текста: Более точно, изобретение относится к сфере эффективной обработки символьных данных.

При обработке текстовой информации часто требуется выполнить сравнение символьных данных, в том числе (но не ограничиваясь) сравнение символьных строк. Обычно команды, применяемые для сравнения символьных данных, в один момент времени выполняют сравнение одиночного байта данных.

Кроме того, при обработке текстовой информации часто требуются другие виды обработки строк, в том числе поиск места завершения (например, конца строки), определение объема символьных данных, поиск определенного символа и т.д. Команды, применяемые в настоящее время для указанных видов обработки, становятся все менее эффективными.

Сущность изобретения

Для преодоления недостатков уровня техники предложен способ выполнения машинной команды в центральном процессорном устройстве, включающий получение процессором машинной команды для выполнения. Команда определена для выполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для указания кода операции, идентифицирующего операцию, выполняемую по команде векторного типа для поиска равнозначного элемента (от англ.: Vector Find Element Equal); поле расширения, используемое для обозначения одного или более регистров; поле первого регистра, объединяемое с первой частью указанного поля расширения для обозначения первого регистра, причем указанный первый регистр содержит первый операнд, являющийся векторным операндом, содержащим заданное число элементов; поле второго регистра, объединяемое со второй частью указанного поля расширения для обозначения второго регистра, причем указанный второй регистр содержит второй операнд, являющийся векторным операндом, содержащим заданное число элементов; поле третьего регистра, объединяемое с третьей частью указанного поля расширения для обозначения третьего регистра, причем указанный третий регистр содержит третий операнд, являющийся векторным операндом, содержащим заданное число элементов; поле маски, которое содержит один или более управляющих флагов (параметров), предназначенных для использования во время выполнения машинной команды. Способ также включает выполнение машинной команды, включающее: принятие решения о том, содержит ли поле маски флаг поиска нуля, указывающий на необходимость поиска в векторе равного нулю элемента; на основе поля маски, содержащего флаг поиска нуля, указывающий на необходимость поиска в векторе равного нулю элемента, выполнение поиска во втором операнде равного нулю элемента, причем в результате поиска предоставляется индекс равного нулю элемента, содержащий либо индекс найденного в результате поиска равного нулю элемента, либо длину вектора, если равных нулю элементов не найдено; выполняемое в параллельном режиме сравнение каждого элемента второго операнда с каждым элементом третьего операнда на предмет равенства их значений, причем в результате сравнения предоставляется индекс сравнения, основанный на направлении поиска и длине элементов вектора и содержащий либо индекс найденного в результате сравнения элемента с равенством значений, либо длину вектора, если равнозначных элементов в результате сравнения не найдено; формирование результата, причем в зависимости от того, выполнялся ли поиск равного нулю элемента, результат содержит одно из двух: если поиск равного нулю элемента не выполнялся, то результат содержит индекс сравнения; если поиск равного нулю элемента выполнялся, то результат содержит минимальное из значений индекса сравнения и индекса равного нулю элемента.

Объектами изобретения являются также система, содержащая средства, приспособленные для выполнения всех шагов описанного выше способа, и машиночитаемый носитель данных, в котором хранится компьютерная программа, содержащая команды для выполнения всех шагов описанного выше способа при ее выполнении в компьютерной системе.

Технический результат, достигаемый при осуществлении изобретения, заключается, в частности, в повышении эффективности обработки символьных данных.

Краткое описание чертежей

В описании и формуле изобретения указываются и отдельно формулируются в качестве примеров один или более аспектов настоящего изобретения. Вышеупомянутые и прочие объекты, особенности и преимущества настоящего изобретения раскрываются в последующем подробном описании, которое сопровождается чертежами.

На чертежах показано:

на фиг. 1 - схема примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2А - схема другого примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2Б - более детальная схема запоминающего устройства из состава вычислительной среды, показанной на фиг. 2А, согласно варианту осуществления настоящего изобретения,

на фиг. 3 - схема варианта формата команды векторного типа для поиска равнозначного элемента согласно варианту осуществления настоящего изобретения,

на фиг. 4 - схема варианта процедуры, связанной с командой векторного типа для поиска равнозначного элемента, согласно варианту осуществления настоящего изобретения,

на фиг. 5 - схема взаимодействия узлов обработки, реализующая процедуру, показанную на фиг. 4, согласно варианту осуществления настоящего изобретения,

на фиг. 6 - схема примера файла регистра согласно варианту осуществления настоящего изобретения,

на фиг. 7 - схема варианта формата команды векторного типа для поиска элемента, равнозначного любому (от англ.: Vector Find Any Equal), согласно варианту осуществления настоящего изобретения,

на фиг. 8 - схема варианта процедуры, связанной с командой векторного типа для поиска элемента, равнозначного любому, согласно варианту осуществления настоящего изобретения,

на фиг. 9 - графическое представление варианта осуществления компьютерного программного продукта, содержащего один или более аспектов настоящего изобретения,

на фиг. 10 - схема варианта осуществления хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 11 - схема другого варианта осуществления компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 12 - схема другого варианта осуществления компьютерной системы, содержащей вычислительную сеть, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 13 - схема варианта осуществления различных узлов компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 14А - схема варианта осуществления исполнительного устройства из состава компьютерной системы, показанной на фиг. 13, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 14Б - схема варианта осуществления устройства ветвления из состава компьютерной системы, показанной на фиг. 13, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 14В - схема варианта осуществления устройства загрузки-хранения из состава компьютерной системы, показанной на фиг. 13, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 15 - схема варианта осуществления эмулируемой (виртуальной) хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения.

Подробное описание

Согласно варианту осуществления настоящего изобретения, предоставляется возможность эффективной обработки символьных данных, в том числе (но не ограничиваясь) буквенных символов на любом языке, чисел, образованных из цифр, знаков пунктуации и/или прочих символов. Указанные символьные данные могут являться строками данных или не являться строками данных. С символьными данными связаны стандарты, примерами которых, в том числе, являются: ASCII (от английского American Standard Code for Information Interchange - Американский стандартный код обмена информацией); Юникод (стандарт Международной организации по стандартизации представления символов всех национальных алфавитов), в том числе (но не ограничиваясь) UTF 8 (от английского Unicode Transformation Format - формат преобразования Юникода); UTF16 и т.д.

Согласно одному из вариантов осуществления, вводится команда Find Element Equal, которая сравнивает данные многоэлементных векторов на предмет равенства и формирует признак равенства, если таковое имеет место. Согласно одному из вариантов осуществления, в специально предусмотренном векторном регистре сохраняется индекс, связанный с тем элементом, которому найден равный элемент.

Согласно настоящей заявке, длина элемента векторного регистра (также используется термин "вектор") составляет, например, один, два или четыре байта; векторным операндом является, например, операнд типа SIMD (от английского Single Instruction, Multiple Data - одиночный поток команд, множественный поток данных), состоящий из множества элементов. Согласно другим вариантам осуществления, длина элементов может быть иной, и векторный операнд необязательно имеет тип SIMD и/или может содержать один элемент.

Согласно другому варианту осуществления, та же команда Find Element Equal также в выбранном векторе выполняет поиск элементов с нулевыми значениями (например, значения всех двоичных разрядов элемента равны нулю). Ноль или пустой символ (символ конца строки) указывает на окончание символьных данных, например, означает конец определенной строки данных. Результат выполнения команды зависит от того, выполнялся ли поиск равного нулю элемента, или же выполнялось сравнение элементов.

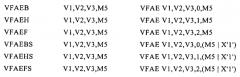

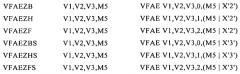

Согласно другому варианту осуществления, вводится команда векторного типа для поиска элемента, равнозначного любому (от англ.: Vector Find Any Equal), которая в векторе выполняет поиск определенных символов и/или равных нулю элементов и возвращает маску или индекс (порядковый номер) байта удовлетворяющего условию символа или равного нулю элемента.

Схема одного из вариантов осуществления вычислительной среды для внедрения и использования одного или более вариантов настоящего изобретения показана на фиг. 1. Вычислительная среда 100 содержит, например, процессор 102 [например, центральное процессорное устройство (ЦПУ)], запоминающее устройство 104 (например, основное запоминающее устройство) и одно или более устройств ввода-вывода и/или один или более интерфейсов 106, соединенных с другой вычислительной средой, например, через одну или более шин 108 и/или с помощью иных соединений.

Согласно варианту осуществления, процессор 102 основан на архитектуре z/Architecture (торговая марка, обозначающая архитектуру линейки мейнфреймов), предложенной корпорацией International Business Machines Corporation (корпорацией IBM) и являющейся частью сервера, такого как сервер System z (торговая марка, обозначающая линейку мейнфреймов), который также предлагается корпорацией International Business Machines Corporation и в котором реализована архитектура z/Architecture. Один из вариантов осуществления архитектуры z/Architecture описан в публикации IBM "z/Architecture Principles of Operation" (от англ.: "Принцип действия архитектуры z/Architecture", публикация IBM №SA22-7832-08, 9-е издание, август 2010 г.). Согласно одному из вариантов осуществления, процессор выполняет команды операционной системы, такой как z/OS, также предлагаемой корпорацией IBM. IBM®, Z/ARCHITECTURE® и Z/OS® являются зарегистрированными торговыми марками корпорации International Business Machines Corporation, Армонк, штат Нью-Йорк, США. Прочие наименования, используемые в настоящей заявке, могут также быть зарегистрированными торговыми марками, торговыми марками или наименованиями продуктов корпорации International Business Machines Corporation или других компаний.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре POWER Architecture (от английского Performance Optimization With Enhanced RISC - оптимизация производительности с применением улучшенной архитектуры RISC), предложенной корпорацией IBM. Одна из реализаций архитектуры POWER Architecture описана в публикации корпорации IBM "Power ISA™ Version 2.06 Revision В" от 23 июля 2010 г. POWER ARCHITECTURE® является зарегистрированной торговой маркой корпорации International Business Machines Corporation.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре Intel, предложенной корпорацией Intel. Одна из реализаций архитектуры Intel описана в публикациях "Intel® 64 and IA-32 Architectures Developer′s Manual: Vol.2B, Команды Set Reference, A-L", номер заказа 253666-041US, декабрь 2011 г., и "Intel® 64 and IA-32 Architectures Developer′s Manual: Vol.2B, Команды Set Reference, M-Z", номер заказа 253667-041US, декабрь 2011 г.. Intel® является зарегистрированной торговой маркой корпорации Intel Corporation, г. Санта-Клара, штат Калифорния, США.

Согласно другому варианту осуществления, схема компьютерного окружения для внедрения и использования одного или более аспектов настоящего изобретения показана на фиг. 2А. В данном примере компьютерное окружение 200 содержит, например, собственное ЦПУ 202, запоминающее устройство 204 и одно или более устройств ввода-вывода и/или интерфейсов 206, соединенных между собой, например, через одну или более шин 208 и/или соединений другого типа. Например, компьютерное окружение 200 может содержать: процессор PowerPC, сервер pSeries или сервер xSeries, предложенные корпорацией International Business Machines Corporation, Армонк, штат Нью-Йорк, США; сервер HP Superdome с процессорами Intel Itanium II, предложенный корпорацией Hewlett Packard Corporation, г. Пало-Альто, штат Калифорния, США; и/или другие электронно-вычислительные машины, основанные на архитектурах, предложенных корпорациями International Business Machines Corporation, Hewlett Packard, Intel, Oracle или другими компаниями и корпорациями.

Собственное ЦПУ 202 содержит один или более собственных регистров 210, таких как один или более регистров общего назначения и/или один или более регистров специального назначения, используемых при выполнении вычислений в компьютерном окружении. Перечисленные регистры содержат информацию, которая отражает состояние компьютерного окружения в каждый отдельно взятый момент времени.

Кроме того, собственное ЦПУ 202 выполняет команды и программный код, которые хранятся в запоминающем устройстве 204. Согласно одному из примеров, ЦПУ выполняет код 212 эмулятора, хранящийся в запоминающем устройстве 204. Этот код позволяет компьютерному окружению, сконфигурированному по одной архитектуре, эмулировать (т.е. имитировать) другую архитектуру. Например, код 212 эмулятора позволяет электронным вычислительным машинам, основанным на архитектурах, отличных от z/Architecture, таким как процессоры PowerPC, серверы pSeries, серверы xSeries, серверы HP Superdome или другим, имитировать архитектуру z/Architecture и выполнять программное обеспечение и команды, разработанные для архитектуры z/Architecture.

Использование кода 212 эмулятора показано более подробно на схеме фиг. 2Б. Гостевые команды 250 содержат команды программного обеспечения (например, машинные команды), которые были разработаны для выполнения на архитектуре, отличной от архитектуры собственного ЦПУ 202. Например, гостевые команды 250 могли были быть разработаны для исполнения на процессоре 102, построенном по архитектуре z/Architecture, однако вместо этого эмулируются на собственном ЦПУ 202, которое может быть, например, процессором типа Intel Itanium II. В одном из примеров код 212 эмулятора содержит устройство 252 выборки команд, предназначенное для получения одной или более гостевых команд 250 из запоминающего устройства 204 и, возможно, для выполнения локальной буферизации (временного хранения) полученных команд. Этот код 212 эмулятора также содержит процедуру 254 трансляции команд, предназначенную для определения типа поступившей гостевой команды и трансляции указанной гостевой команды в одну или более соответствующих собственных команд 256 (т.е. команд, предназначенных для исполнения собственным ЦПУ, построенным по собственной архитектуре). В состав процедуры трансляции входят, например, идентификация функции, которая должна выполняться гостевой командой, и выбор собственной команды или набора команд для выполнения этой функции.

Кроме того, эмулятор 212 содержит процедуру 260 управления эмуляцией, обеспечивающую исполнение собственных команд. Процедура 260 управления эмуляцией может заставить собственное ЦПУ 202 выполнять программу из собственных команд, которая имитирует одну или более раннее поступивших гостевых команд, и по окончании этого вычислительного процесса возвращать управление упомянутой процедуре выборки команд для имитации получения следующей гостевой команды или группы гостевых команд. Процесс выполнения собственных команд 256 может содержать загрузку данных в регистр из запоминающего устройства 204, передачу данных из регистра обратно в запоминающее устройство для хранения или выполнение некоторой арифметической или логической операции в соответствии с указаниями процедуры трансляции.

Каждая процедура реализована, например, в программном обеспечении, которое хранится в запоминающем устройстве и выполняется собственным ЦПУ 202. В других примерах одна или более процедур или операций реализованы в постоянном запоминающем устройстве (ПЗУ), в аппаратном или программном обеспечении или в их комбинации. Упомянутые регистры эмулируемого процессора могут имитироваться с использованием регистров 210 собственного ЦПУ или с использованием пространства памяти запоминающего устройства 204. Согласно вариантам осуществления, гостевые команды 250, собственные команды 256 и код 212 эмулятора могут располагаться в одном и том же запоминающем устройстве или могут храниться распределенно (т.е. в различных запоминающих устройствах).

В рассматриваемом примере ПЗУ хранит, например, микрокод, милликод и/или макрокод процессора. Код содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации машинных кодов более высокого уровня. В одном из вариантов осуществления код содержит, например, проприетарный код, который обычно является микрокодом и содержит выверенное программное обеспечение или микрокод, специфический для окружающего аппаратного обеспечения и контролирующий доступ операционной системы к аппаратному обеспечению вычислительной системы.

В одном из примеров загружаемая, транслируемая и исполняемая гостевая команда 250 является одной из описанных в настоящей заявке команд. Такая команда, предназначенная для одной архитектуры (например, для архитектуры z/Architecture), извлекается из запоминающего устройства, транслируется и представляется набором собственных команд 256 другой архитектуры (например, архитектуры PowerPC, pSeries, xSeries, Intel и т.д.). Затем указанные собственные команды исполняются.

Согласно варианту осуществления, описанные команды являются командами векторного типа и являются частью векторного функционала (т.е. векторной среды, набора команд векторного типа и средств их обработки), предоставляемого согласно аспекту настоящего изобретения. Векторный функционал позволяет работать, например, с векторами фиксированной длины в пределах от одного до шестнадцати элементов. Каждый вектор содержит данные, которые обрабатываются векторными командами, определенными в векторном функционале. Согласно варианту осуществления, если вектор образован из набора элементов, то каждый элемент обрабатывается параллельно с другими элементами. Выполнение команды не завершено, пока не завершена обработка всех элементов.

Согласно настоящей заявке, векторные команды могут применяться в составе различных архитектур, в том числе (но не ограничиваясь) z/Architecture, Power, Intel и т.д. Несмотря на то, что описываемый в настоящей заявке вариант осуществления ориентирован на архитектуру z/Architecture, векторные команды и один или более аспектов настоящего изобретения могут базироваться и предназначаться для многих других типов архитектур. Архитектура z/Architecture используется исключительно в качестве одного из примеров.

Согласно варианту осуществления, по которому векторный функционал реализован как часть архитектуры z/Architecture, для того, чтобы использовать векторные регистры и команды, в специализированном управляющем регистре (например, управляющем регистре 0) флаги разрешения векторного функционала и векторных регистров должны быть установлены в состояние, например, логической единицы. Если векторный функционал инсталлирован, и векторная команда выполняется без разрешающих флагов, то возникает программное исключение (ошибка) данных. Если же векторный функционал не инсталлирован, и делается попытка выполнить векторную команду, то возникает программное исключение (ошибка) исполнения.

Векторные данные располагаются в запоминающем устройстве, например, в той же самой последовательности, слева направо, как и прочие форматы данных. Разряды формата данных с номерами от 0 до 7 образуют байт в крайней левой (с наименьшим номером) ячейке хранения байтов пространства памяти; разряды с номерами от 8 до 15 образуют байт в следующей за предыдущей ячейке памяти и т.д. В другом примере векторные данные могут располагаться в пространстве памяти запоминающего устройства в иной последовательности, например, справа налево.

Многие векторные команды, поддерживаемые векторным функционалом, снабжены полем, состоящим из специальных разрядов. Такое поле, называемое полем RXB (от английского register extension bit - бит расширения регистра), содержит наиболее значимый разряд для обозначений (т.е. для адресов) векторных регистров операндов. Разряды обозначений векторных регистров операндов, не оговоренные спецификацией команды, являются зарезервированными и должны быть установлены в состояние логического нуля.

Согласно варианту осуществления, поле RXB состоит из четырех разрядов (например, с номерами от 0 до 3), и значения этих разрядов имеют следующее назначение:

разряд 0 - наиболее значимый разряд обозначения векторного регистра первого операнда;

разряд 1 - наиболее значимый разряд обозначения векторного регистра второго операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 2 - наиболее значимый разряд обозначения векторного регистра третьего операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 3 - наиболее значимый разряд обозначения векторного регистра четвертого операнда, если такой операнд и соответствующий регистр предусмотрены командой.

Каждый разряд устанавливается в состояние логического нуля или логической единицы, например, ассемблером, в зависимости от номера регистра. Например, в регистрах с номерами от 0 до 15 разряд устанавливается в состояние логического нуля, в регистрах с номерами от 16 до 31 разряд устанавливается в состояние логической единицы и т.д.

Согласно варианту осуществления, каждый разряд поля RXB является разрядом расширения определенного поля в составе команды, указывающего на один или более векторных регистров. Например, в одной или более векторных командах разряд с номером 0 поля RXB служит разрядом-расширением части команды с номерами позиций от 8 до 11, эта часть команды обозначается, например, как V1; разряд с номером 1 поля RXB служит разрядом-расширением части команды с номерами позиций от 12 до 15, эта часть команды обозначается, например, как V2, и т.д.

Согласно другому варианту осуществления, поле RXB содержит дополнительные разряды, и для указания на каждый вектор или регистр в качестве разрядов-расширений используются по два и более разрядов.

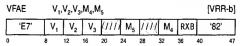

Согласно аспекту настоящего изобретения, одной из команд, содержащих поле RXB, является команда векторного типа для поиска равнозначного элемента, структура (схема формата) которой показана на фиг. 3. В одном из примеров команда 300 векторного типа для поиска равнозначного элемента содержит: поля кода операции 302а (например, разряды с номерами 0-7) и 302b (например, разряды 40-47), идентифицирующие операцию векторного типа для поиска равнозначного элемента; поле 304 первого векторного регистра (например, разряды 8-11), используемое для обозначения первого векторного регистра (V1); поле 306 второго векторного регистра (например, разряды 12-15), используемое для обозначения второго векторного регистра (V2); поле 308 третьего второго векторного регистра (например, разряды 16-19), используемое для обозначения третьего векторного регистра (V3); поле 310 первой маски (М5) (например, разряды 24-27); поле 312 второй маски (М4) (например, разряды 32-35); поле 314 RXB (например, разряды 36-39). В одном из вариантов осуществления каждое из полей 304-314 является отдельным и независимым от поля (полей) кода оптации. Кроме того, согласно другому варианту осуществления, указанные поля являются отдельными и независимыми между собой; однако, согласно другим вариантам осуществления, два и более полей могут быть объединенными. Далее приводятся сведения об использовании перечисленных полей.

Согласно варианту осуществления, определенные разряды (например, первые два разряда) кода операции из состава поля 302а кода операции определяют длину и формат команды. В рассматриваемом примере двоичное число в указанных разрядах означает, что длина составляет три полуслова и что формат - операция типа векторный регистр и регистр, с расширенным кодом операции. Каждое из векторных (V) полей совместно с соответствующим разрядом расширения регистра, содержащимся в поле RXB, обозначает некоторый векторный регистр. В частности, векторный регистр, содержащий операнд, обозначается (адресуется) с использованием, например, четырехразрядного поля обозначения регистра и разряда RXB как наиболее значимого. Например, если четырехразрядное поле содержит двоичное число 0110, и в разряде расширения содержится двоичное число 0, то пятиразрядное число 00110 указывает на регистр с номером 6 в десятичной системе счисления.

Нижний индекс в обозначении поля команды соответствует номеру операнда, к которому это поле относится. Например, нижний индекс "1" в обозначении "V1" векторного регистра указывает на соответствие регистра первому операнду и т.д. Операнд регистра имеет ту же длину, что и сам регистр, например 128 бит.

Поле М4, состоящее, например, из четырех разрядов с номерами от 0 до 3, описывает спецификатор длины элемента, например, с помощью разрядов с 1-го по 3-й. Спецификатор длины элемента задает длину элементов операндов векторного регистра. Например, спецификатор длины элемента задает длину элемента равной одному байту, полуслову (например, два байта) или слову (например, четыре байта). Например, значение 0 обозначает длину в один байт, 1 обозначает полуслово, 2 - слово, называемое также полным словом. Если в поле использовано зарезервированное значение, то возникает программное исключение (ошибка) спецификации.

Поле М5 является, например, четырехразрядным, и его разряды с номерами от 0 до 3 имеют, например, следующие значения:

разряд 2 - поле флага ZS (от английского zero search - поиск нуля) поиска нуля: значение 1 указывает, что каждый элемент второго операнда дополнительно сравнивается с нулем (в следующем примере каждый элемент третьего операнда или иного операнда сравниваемого с нулем);

разряд 3 - поле флага СС (от английского condition code - код условия) установки кода условия: значение 0 указывает, что установка кода условия не требуется, значение кода условия остается неизмененным; значение 1 указывает, что код условия устанавливается, например, по следующему правилу:

значение 0: если флаг ZS поиска нуля установлен, то сравнение выявило во втором операнде элемент с нулевым значением, и индекс этого элемента меньше, чем индекс любого из элементов второго операнда, совпадающих с каким-либо элементом третьего операнда;

значение 1: сравнение выявило совпадение некоторого элемента второго операнда с элементом третьего операнда. Если установлен флаг ZS поиска нуля, то указанное совпадение выявлено в элементе, индекс которого меньше или равен индексу равного нулю элемента второго операнда; значение 2: не определено;

значение 3: элементов с совпадающими значениями не выявлено. Согласно одному из вариантов осуществления, при выполнении команды векторного типа для поиска равнозначного элемента в направлении, по одному из вариантов осуществления, слева направо, беззнаковые целые двоичные элементы второго операнда (содержащиеся в регистре, определяемом значением поля V2 и соответствующим ризрядом RXB) сравниваются с соответствующими им беззнаковыми целыми двоичными элементами третьего операнда (содержащимися в регистре, определяемом значением поля V3 и соответствующим разрядом RXB). Если два элемента равны (т.е. их значения совпадают), то индекс первого байта крайнего левого равного элемента помещается в специально предназначенный байт (например, в байт 7) первого операнда (содержащегося в регистре, определяемом значением поля V1 и соответствующим разрядом RXB). В оставшиеся байты первого операнда записываются нули.

Например, если длина элемента составляет один байт, то возвращается индекс байта крайнего левого равного элемента (например, если имеется 16 элементов с номерами от 0 до 15, совпадает элемент с номером 6, то возвращается значение 6 индекса байта). Аналогично, если длина элемента составляет полуслово, имеется восемь элементов с номерами от 0 до 7, и совпадают два байта третьего элемента с номерами 6 и 7, то возвращается значение 6 индекса байта. Если же длина элемента составляет полное слово, имеется четыре элемента с номерами от 0 до 3, и байты с 4-го по 7-й первого элемента совпадают, то возвращается значение 4 индекса байта.

Если совпадающих или равных нулю (если был задан поиск нуля) байтов не выявлено, то в определенном байте (например, в байте 7) первого операнда сохраняется значение индекса, равное длине вектора (например, число байтов; например, 16).

Если в поле М5 установлен флаг поиска нуля, то каждый элемент второго операнда (либо, согласно другому варианту осуществления, другого операнда, в частности, третьего операнда) дополнительно проверяется на предмет равенства нулю (пустому элементу; символу конца строки). Если во втором операнде нулевой элемент обнаружен прежде, чем выявлено равенство каких-либо иных элементов второго и третьего операндов, то в специально предназначенном байте (например, в байте 7) первого операнда сохраняется индекс первого байта равного нулю элемента, а во все прочие элементы первого операнда записываются. Если значение флага установки кода условия равно единице, то значение кода условия устанавливается равным нулю.

Согласно варианту осуществления, сравнение элементов ведется в параллельном режиме. Например, если сравниваемые векторные регистры имеют длину 16 байтов, то одновременно сравниваются 16 байтов. Согласно другому варианту осуществления, кроме того, во время исполнения задается направление векторов: слева направо или справа налево. Например, команда обращается к регистру, флагу состояния или другому объекту, который указывает направление обработки: либо слева направо, либо справа налево. Согласно варианту осуществления, флаг направления не встроен жестко в саму команду, он сообщается команде во время выполнения.

Согласно другому варианту осуществления, команда не содержит поле RXB: расширение не используется вовсе или расширение организовано иным способом, например, по внешнему по отношению к команде указанию, или же расширение содержится в другом поле той же команды.

Дальнейшие сведения об одном из вариантов осуществления команды векторного типа для поиска равнозначного элемента поясняются схемой на фиг. 4. В одном из примеров процессор компьютерного окружения выполняет следующий алгоритм.

Вначале на шаге 400 принимается решение о том, должен ли быть выполнен поиск нуля (так называемого нулевого элемента, конца строки, символа окончания и т.п.). Если поиск нуля должен быть выполнен, то на шаге 402 выполняется сравнение с нулевыми символами, т.е. поиск равных нулю элементов, результат поиска присваивается выходной переменной nullidx (от английского null index - индекс нулевого символа) 403. Например, если длина элемента - байт, и в пятом байте найден равный нулю элемент, то индекс этого байта (например, 5) помещается в nullidx. Аналогично, если длина элемента составляет полуслово, имеется восемь элементов с номерами от 0 до 7, и значение третьего элемента (т.е. байты с номерами 6 и 7) равно нулю, то в nullidx помещается значение 6 (соответствует индексу байта 6). Аналогично, если длина элемента составляет полное слово, имеется четыре элемента с номерами от 0 до 3, и значение первого элемента (т.е. байты с 4-го по 7-й) равно нулю, то в nullidx помещается значение 4 (соответствует индексу байта 4). Если равный нулю элемент не выявлен, то согласно одному из примеров в nullidx помещается значение, равное длине вектора (например, в байтах; например, 16).

Кроме того, или даже если поиск нуля не должен выполняться, то на шаге 404 в параллельном режиме выполняется множество (например, 16) операций, состоящих в сравнении А и В операцией сравнения. В одном из примеров А -содержимое второго операнда, В - содержимое третьего операнда, и операция сравнения - равенство.

Результат сравнения присваивается переменной 406, называемой либо левым индексом, cmpidxl (от английского comparison index left - индекс сравнения слева), либо правым индексом, cmpidxr (от английского comparison index right - индекс сравнения справа) в зависимости от того, в каком направлении велся поиск: слева или справа. Например, если операция сравнения - равенство, поиск велся слева направо, а сравнение выявило одно или более совпадений, то значение индекса, связанное с первым байтом младшего из совпавших элементов, помещается в cmpidxl. Например, если длина элемента - байт, вектор состоит из 16 элементов (с номерами от 0 до 15) и выявлено равенство в элементе с номером 6, то в переменной cmpidxl сохраняется значение 6. Аналогично, если длина элемента - полуслово, вектор состоит из восьми элементов (с номерами от 0 до 7) и выявлено равенство в элементе с номером 3 (например, в байтах 6 и 7), то возвращается индекс первого байта данного элемента (т.е. значение 6). Аналогично, если длина элемента - полное слово, вектор состоит из четырех элементов (с номерами от 0 до 3) и выявлено равенство в элементе 1 (т.е. в байтах с 4-го по 7-й), то возвращается индекс первого байта данного элемента (т.е. значение 4). Если совпадений не выявлено, то согласно варианту осуществления переменной cmpidxl или cmpidxr (в зависимости от направления поиска) присваивается значение, равное длине вектора (например, в байтах; например, значение 16).

Затем на шаге 408 принимается решение, велся ли поиск слева или справа. Если поиск велся слева, то на шаге 410 переменной cmpidx присваивается значение cmpidxl, в противном случае на шаге 412 переменной cmpidx присваивается значение переменной cmpidxr.

После присвоения значения переменной cmpidx принимается решение, велся ли поиск нуля - шаг 414. Если поиск нуля не велся, то на шаге 416 переменной idx (от английского index - индекс) присваивается значение cmpidx. Если поиск нуля велся, то на шаге 418 переменной idx присваивается минимальное из значений индекса сравнения и индекса нуля (т.е. nullidx). Этим шагом работа алгоритма заканчивается.

На фиг. 5 показана схема, поясняющая выполнение операций по алгоритму, показанному на фиг. 4. В данном примере имеется два входных блока данных, вектор В 500 и вектор А 502. Оба этих вектора поступают на операцию 504 сравнения, которая выполняет сравнение (например, поиск равенства) в параллельном режиме. Кроме того, один из входных векторов, а именно вектор А, поступает также на операцию 506 поиска нулевых символов.

Результаты работы операций сравнения - значение 508 переменных id×L или id×R, а также результат операции поиска нуля - значение 510 переменной nullidx поступают в процедуру 512 определения результата. Процедура 512 также принимает значения следующих управляющих переменных (флагов): справа/слева 514, указывающей направление поиска; поиск нуля 516, показывающей, велся ли поиск нуля; длина элемента 518, указывающей длину каждого элемента векторов (например, байт, полуслово, полное слово). Процедура 512 формирует результат обработки - значение переменной resultidx (от англ.: индекс-результат) 520, котор