Способ, устройство и система уменьшения времени возобновления работы для корневых портов и конечных точек, интегрированных в корневые порты

Иллюстрации

Показать всеГруппа изобретений относится к области вычислительной техники и может быть использована для возобновления работы для корневых портов и конечных точек, интегрированных в корневые порты. Техническим результатом является уменьшение времени перехода в рабочее состояние. Устройство содержит логику восстановления для: определения того, что устройство в состоянии низкой мощности; инициирования перехода устройства из состояния низкой мощности в активное состояние, при этом определено фиксированное минимальное время восстановления для переходов из состояния низкой мощности в активное состояние; идентификации возможности устройства, соответствующей переходу указанного устройства из состояния низкой мощности в активное состояние, и завершения перехода устройства из состояния низкой мощности в активное состояние по меньшей мере частично на основе указанной возможности, при этом переход подлежит завершению до истечения фиксированного минимального времени восстановления; при этом указанная возможность содержит возможность прерывания, а логика восстановления, дополнительно, выполнена с возможностью получения прерывания от указанного устройства, при этом прерывание представляет собой указание того, что устройство готово завершить переход. 4 н. и 20 з.п. ф-лы, 10 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к вычислительной системе и, в частности (но не исключительно), к периодам времени возобновления работы для корневых портов и конечных точек, интегрированных в корневые порты.

Уровень техники

Так как электронные устройства становятся все более сложными и повсеместно используются в повседневной жизни пользователей, к ним предъявляется все больше и больше разнообразных требований. Чтобы удовлетворить большинство из этих требований, ряд электронных устройств содержит многочисленные электронные устройства, таких как центральное процессорное устройство (ЦПУ), устройство связи, графический ускоритель и т.д. Во многих случаях между этими устройствами можно устанавливать связь с большим объемом передаваемых данных. Кроме того, многие пользователи испытывают большие надежды, связанные с техническими характеристиками устройство. Пользователи становятся все менее терпимыми к большому времени ожидания операций, выполняемых их устройствами. В дополнение к этому, многие устройства выполняют все более сложные и тяжелые задачи, которые могут приводить к большим объемам передачи данных между устройствами. Поэтому между этими устройствами можно поддерживать связь, которая будет преимущественной от быстрого времени срабатывания.

Краткое описание чертежей

Варианты осуществления проиллюстрированы посредством примера, а не посредством ограничения, на фигурах сопроводительных чертежей одинаковые ссылочные позиции показывают аналогичные элементы, при этом:

фиг. 1 иллюстрирует варианты осуществления блок-схемы вычислительной системы, включающие в себя многоядерный процессор, согласно по меньшей мере одному примерному варианту осуществления;

фиг. 2 иллюстрирует вариант осуществления вычислительной системы, включающей в себя архитектуру межсоединений согласно по меньшей мере одному примерному варианту осуществления;

фиг. 3 иллюстрирует вариант осуществления архитектуры межсоединений, включающей в себя многоуровневый стек согласно по меньшей мере одному примерному варианту осуществления;

фиг. 4 иллюстрирует вариант осуществления запроса или пакета, который будет генерироваться или приниматься в рамках архитектуры межсоединений согласно по меньшей мере одному примерному варианту осуществления;

фиг. 5 иллюстрирует вариант осуществления пары передатчика и приемника для архитектуры межсоединений согласно по меньшей мере одному примерному варианту осуществления;

фиг. 6 иллюстрирует примерную диаграмму переходов состояний управления мощностью;

фиг. 7 - блок-схема последовательности операций согласно по меньшей мере одному варианту осуществления;

фиг. 8 - блок-схема последовательности операций согласно по меньшей мере одному варианту осуществления;

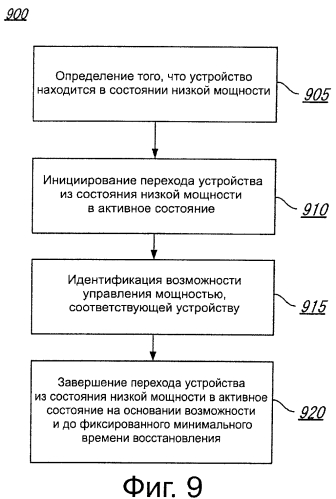

фиг. 9 - блок-схема последовательности операций согласно по меньшей мере одному примерному варианту осуществления;

фиг. 10 иллюстрирует вариант осуществления блок-схемы для вычислительной системы.

Осуществление изобретения

В последующем описании изложены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные структуры аппаратных средств, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы инструкций, конкретные компоненты систем, конкретные измерения/вершины, конкретные стадии и работа процессорного конвейера и т.д., чтобы обеспечить полное понимание настоящего изобретения. Однако специалистам в данной области техники будет очевидно, что эти конкретные детали не обязательно должны применяться при практическом осуществлении настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы/код для описанных алгоритмов, конкретный код аппаратных средств, конкретная операция межсоединения, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные реализации компилятора, конкретное выражение алгоритмов в коде, конкретное выключение питания и вентильная технология/логика и другие конкретные подробности работы компьютерной системы подробно не описаны во избежание излишнего усложнения настоящего изобретения.

Хотя следующие варианты осуществления можно описать со ссылкой на уменьшение времени возобновления работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, таких как в вычислительных платформах или микропроцессорах, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Аналогичные технологии и идеи вариантов осуществления, описанных здесь, можно применить к другим типам и схемам полупроводниковых устройств, которые могут также получить выигрыш от уменьшения времени возобновления работы. Например, раскрытые варианты осуществления не ограничиваются настольными компьютерными системами или Ultrabooks™. К тому же, их можно также использовать и в других устройствах, таких как портативные карманные устройства, планшетные компьютеры, другие тонкие ноутбуки, устройства "системы на микросхеме″ (SOC) и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства на основе Интернет-протокола, цифровые камеры, персональные цифровые помощники (PDA) и портативные персональные компьютеры (ПК). Встроенные приложения типично включают в себя микроконтроллер, процессор цифровой обработки сигналов (DSP), систему на микросхеме, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая позволяет выполнять функции и операции, указанные ниже. Более того, устройства, способы и системы, описанные здесь, не ограничиваются физическими вычислительными устройствами, но могут также относиться к оптимизациям программного вычисления для уменьшения периодов возобновления работы.

На фиг. 1 изображена блок-схема, иллюстрирующая компоненты, связанная с уменьшением времени возобновлением работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, согласно по меньшей мере одному примерному варианту осуществления. Примеры фиг. 1 представляют собой только примеры компонентов, связанных с уменьшением времени возобновления работы для корневых портов и конечных точек, составляющих единое целое с корневыми портами, и не ограничивают объем формулы изобретения. Например, могут изменяться операции, относящиеся к компоненту, может изменяться число компонентов, может изменяться состав компонента и/или т.п. Например, в некоторых вариантах осуществления операции, относящиеся к одному компоненту примера, показанного на фиг. 1, можно выделить одному или более другим компонентам.

Процессор 100 включает в себя любой процессор или процессорное устройство, такое как микропроцессор, встроенный процессор, процессор цифровой обработки сигналов (DSP), сетевой процессор, портативный процессор, процессор приложений, сопроцессор, система на кристалле (SOC) или другое устройство для исполнения кода. Процессор 100 в одном варианте осуществления включает в себя по меньшей мере два ядра - ядро 101 и 102, которые могут включать в себя ассиметричные ядра и симметричные ядра (иллюстрированные варианты осуществления). Однако процессор 100 может включать в себя любое число процессорных элементов обработки, которые могут быть симметричными или ассиметричными.

В одном варианте осуществления процессорный элемент относится к аппаратным средствам или к логике для поддержки программного потока. Примеры аппаратных процессорных элементов включают в себя: блок потоков, слот потоков, поток, блок обработки, контекст, блок контекста, логический процессор, аппаратный поток, ядро и/или любой другой элемент, который может поддерживать состояние для процессора, такое как состояние исполнения или архитектурное состояние. Другими словами, процессорный элемент в одном варианте осуществления относится к любому аппаратному средству, которое может независимым образом ассоциироваться с кодом, таким как программный поток, операционная система, приложение или другой код. Физический процессор (или разъем для установки процессора) типично относится к интегральной схеме, которая потенциально включает в себя любое число других процессорных элементов, таких как ядра или аппаратные потоки.

Ядро часто относится к логике, расположенной на интегральной схеме, с возможностью поддержания независимого архитектурного состояния, в котором каждое архитектурное состояние, поддерживаемое независимым образом, ассоциируется по меньшей мере с некоторыми выделенными ресурсами исполнения. В отличие от ядер аппаратный поток типично относится к любой логике, расположенной на интегральной схеме, с возможностью поддержания независимого архитектурного состояния, в котором архитектурные состояния, поддерживаемые независимым образом, совместно используют доступ к ресурсам исполнения. Как можно увидеть, когда совместно используются определенные ресурсы, и другие ресурсы выделяются архитектурному состоянию, линия между номенклатурой аппаратного потока и ядром перекрывается. Тем не менее, часто ядро и аппаратный поток рассматриваются операционной системой как отдельные логические процессоры, где операционная система может отдельно планировать операции, исполняемые в каждом логическом процессоре.

Физический процессор 100, как иллюстрировано на фиг. 1, включает в себя два ядра - 101 и 102. В данном случае, ядро 101 и 102 рассматриваются как симметричные ядра, то есть ядра с одинаковыми конфигурациями, функциональными блоками и/или логикой. В другом варианте осуществления ядро 101 включает в себя процессорное ядро неупорядоченного исполнения, тогда как ядро 102 включает в себя процессорное ядро упорядоченного исполнения. Однако ядра 101 и 102 можно по отдельности выбрать из любого типа ядра, такого как родное ядро, ядро, управляемое с помощью, программного обеспечения, ядро, адаптированное к исполнению родной архитектуры набора команд (ISA), ядро, адаптированное для исполнения транслированной архитектуры набора команда (ISA), ядро комплексного проектирования или другое известное ядро. В неоднородной среде ядра (то есть ассиметричные ядра), некоторую форму трансляции, такую как двоичная трансляция, можно использовать для планирования или исполнения кода в одном или обоих ядрах. Тем не менее, в дальнейшем обсуждении функциональные блоки, иллюстрированные в виде ядра 101, описаны более подробно ниже, так как блоки в ядре 102 работают аналогичным образом в изображенном варианте осуществления.

Как изображено, ядро 101 включает в себя два аппаратных потока 101a и 101b, которые можно также называть как слоты 101а и 101b аппаратных потоков. Поэтому программные объекты, такие как операционные системы, в одном варианте осуществления, потенциально рассматривают процессор 100 как четыре отдельных процессора, четыре логических процессора или процессорные элементы с возможностью одновременного исполнения четырех программных потоков. Как упоминалось выше, первый поток ассоциируется с регистрами 101а состояния архитектуры, второй поток ассоциируется с регистрами 101b состояния архитектуры, третий поток может ассоциироваться с регистрами 102а состояния архитектуры и четвертый поток может ассоциироваться с регистрами 102b состояния архитектуры. В данном случае, каждый из регистров (101а, 101b, 102а и 102b) состояния архитектуры можно называть как процессорные элементы, потоковые слоты или потоковые блоки, как описано выше. Как это иллюстрировано, регистры 101а состояния архитектуры тиражируются в регистрах 101b состояния архитектуры, поэтому отдельные состояния, контексты архитектуры могут сохраняться для логического процессора 101а и 101b. В ядре 101 другие меньшие ресурсы, такие как указатели инструкций и логика переименования в распределителе, и блок 130 переименования и распределения можно также дублировать для потоков 101а и 101b. Некоторые ресурсы, такие как буферы переупорядочения в блоке 135 переупорядочения/извлечения, целевой буфер ветвления (ВТВ) и буфер 120 трансляции инструкций (I-TLB), буферы нагрузки/хранения и очереди можно совместно использовать посредством разбиения. Другие ресурсы, такие как внутренние регистры общего назначения, регистр(ы) базовой страницы-таблицы, данные кэш-памяти низкого уровня и данные TLB 150, блок(и) 140 исполнения и части блок 135 неупорядоченного исполнения потенциально и полностью используются совместно.

Процессор 100 часто включает в себя другие ресурсы, которые можно в полное мере совместно использовать, совместно использовать путем разбиения или выделения с помощью/в процессорных элементах. На фиг. 1 проиллюстрирован вариант осуществления только примерного процессора с иллюстративными логическими блоками/ресурсами процессора. Следует отметить, что процессор может включать в себя или не включать в себя или не включать в себя любой из этих функциональных блоков, а также включать в себя любые другие известные функциональные блоки, логику или непоказанные аппаратные средства. Как показано, ядро 101 включает в себя упрощенное, типичное процессорное ядро с неупорядоченным исполнением (ООО). Но процессор с упорядоченным исполнением можно использовать в различных вариантах осуществления. Ядро ООО включает в себя а ВТВ и I-TLB 120 для предсказания ветвей, которые будут исполняться/получать и ВТВ и I-TLB 120 для хранения вводов трансляции адресов для инструкций.

Ядро 101 дополнительно включает в себя модуль 125 декодирования, соединенный с ВТВ и I-TLB 120 для декодирования выбранных элементов. Логика выборки в одном варианте осуществления включает в себя отдельные секвенсеры, ассоциированные с потоковыми слотами 101а, 101b, соответственно. Обычно ядро 101 ассоциируется с первой ISA, которая определяет/специфицирует инструкции, исполняемые в процессоре 100. Часто инструкции машинного кода, которые представляют собой часть первой ISA, включают в себя часть инструкций, которые называются кодом операции, которая обращается к/специфицирует инструкцию или операцию, которая будет выполняться. Логика 125 декодирования включает в себя схему, которая распознает эти инструкции из своих кодов операций и передает декодированные инструкции по конвейеру для обработки, так как это определено первой ISA. Например, как будет более подробно описано ниже, декодеры 121 в одном варианте осуществления включают в себя логику, назначенную или адаптированную для распознавания конкретных инструкций, таких как транзакционная инструкция. В результате распознавания с помощью декодеров 125, архитектура или ядро 101 принимает конкретные, предварительно определенные действия для выполнения задач, связанных с соответствующей инструкцией. Важно отметить, что любую из задач, блоков, операций и способов, описанных здесь, можно выполнить в ответ на одну или нескольких инструкций, некоторые из которых могут быть новыми или старыми инструкциями. Следует отметить, что декодеры 125 в одном варианте осуществления распознают ту же самую ISA (или ее поднабор). Альтернативно, в неоднородной среде ядра декодеры 125 распознают вторую ISA (либо поднабор первой ISA или особый ISA).

В одном примере блок 130 переименования и распределения включает в себя распределитель для резервирования ресурсов, таких как регистровые файлы для хранения результатов обработки инструкций. Однако потоки 101а и 101b имеют возможность неупорядоченного исполнения, где блок 130 переименования и распределения также резервирует другие ресурсы, такие как буферы переупорядочения, чтобы отследить результаты инструкций. Блок 130 переименования и распределения может также включать в себя средство переименования регистров для переименования регистров со ссылкой на программы/инструкции для других регистров, внутренних к процессору 100. Блок 135 переупорядочения/извлечения включает в себя компоненты, такие как буферы переупорядочения, упомянутые выше, буферы загрузки и буферы хранения для поддержания неупорядоченного исполнения и впоследствии упорядоченного извлечения инструкций, исполняемых вне очереди.

Блок 140 модуля(ей) планирования и исполнения в одном варианте осуществления включает в себя модуль планировщика для планирования инструкций/операции по отношению к исполнительным блокам. Например, инструкция операции с плавающей точкой планируется в порту блока исполнения, который имеет доступный блок исполнения операций с плавающей точкой. Файлы регистров, ассоциированные с блоками исполнения, также включены для хранения информационных результатов обработки инструкций. Примерные блоки исполнения включают в себя блок исполнения операций с плавающей точкой, блок исполнения целочисленных операций, блок исполнения переходов, блок исполнения загрузки, блок исполнения сохранения и другие известные блоки.

Кэш данных нижнего уровня и буфер 150 трансляции данных (D-TLB) соединены с блоком(ами) 140 исполнения. Кэш данных предназначен для хранения недавно используемых, выполняемых операций над элементами, такими как операнды данных, которые потенциально удерживаются в состояниях когерентности памяти. D-TLB предназначен для хранения последних, виртуальных/линейных и физических адресных трансляций. В качестве конкретного примера, процессор может включать в себя структуру таблицы страниц для разбиения физической памяти на множество виртуальных страниц.

В данном случае, ядра 101 и 102 совместно используют доступ к кэш более высокого уровня или еще выше, такому как кэш второго уровня, ассоциированный с интерфейсом 810, расположенным на кристалле. Следует отметить, что более высокий уровень или еще выше относится к уровням кэш, которые увеличиваются или становятся дальше от блока(ов) исполнения. В одном варианте осуществления кэш более высокого уровня представляет собой кэш данных самого последнего уровня (последний кэш в иерархии памяти в процессоре 100), таком как кэш данных второго или третьего уровня. Однако кэш более высокого уровня не является ограниченным, так как он может ассоциироваться с или включать в себя кэш инструкций. Трассовый кэш (тип кэша инструкций) вместо этого может быть связан после декодера 125 для хранения недавно декодированных трасс. В данном случае, инструкция потенциально относится к макроинструкции (то есть к общей инструкции, распознанной декодерами), которая может быть закодирована в ряде микроинструкций (микроопераций).

В изображенной конфигурации процессор также включает в себя накристальный модуль 110 интерфейса. Исторически контроллер памяти, который будет более подробно описан ниже, был включен в вычислительную систему (внешнюю) к процессору 100. В этом сценарии накристальный модуль ПО интерфейса должен поддерживать связь с устройствами, внешними к процессору 100, такими как системная память 175, микропроцессорный набор (часто включающий в себя концентратор контроллера памяти для подсоединения к памяти 175 и концентратор контроллера ввода/вывода для подсоединения периферийных устройств), концентратор контроллера памяти, северный мост или другую интегральную схему. И в этом сценарии шина 105 может включать в себя любое известное межсоединение, такое как многоточечная шина, двухточечное межсоединение, последовательное межсоединение, параллельная шина, когерентная (например, когерентная кэш-память) шина, архитектура многоуровневого протокола, дифференциальная шина и шина приемопередатчиков (GTL).

Память 175 можно выделить процессору 100 или совместно использовать с другими устройствами в системе. Общие примеры типов памяти 175 включают в себя DRAM, SRAM, энергонезависимую память (NV память) и другие известные запоминающие устройства. Следует отметить, что устройство 180 может включать в себя графический процессор и плату, подсоединенную к концентратору контроллера памяти, запоминающее устройство для данных, подсоединенное к концентратору контроллера ввода/вывода, беспроводный приемопередатчик, устройство флэш-памяти, аудиоконтроллер, сетевой контроллер, или другое известное устройство.

Однако в последнее время, так как большое количество логических схем и устройств выполняется как единое целое на одном кристалле, таком как система на кристалле (SOC), каждое из этих устройств можно встроить в процессор 100. Например, в одном варианте осуществления концентратор контроллера памяти находится в одном и том же корпусе и кристалле с процессором 100. В данном случае, часть ядра (часть на ядре) 100 включает в себя один или более контроллеров для сопряжения с другими устройствами, такими как память 175 или устройство 180. Конфигурация, включающая в себя межсоединение и контроллеры для сопряжения с такими устройствами часто называется как наядерной (или неядерной конфигурацией). В качестве примера накристальный интерфейс ПО включает в себя кольцевое межсоединение для накристальной связи и высокоскоростную последовательную двухточечную линии 105 связи для внекристальной связи. Кроме того, в среде SOC даже большее количество устройств, таких как сетевой интерфейс, сопроцессоры, память 175, устройство 180 и любые другие известные компьютерные устройства/интерфейсы можно выполнить как единое целое на одном кристалле или интегральной схемы для обеспечения маленького форм-фактора с высокими функциональными возможностями и низкой потребляемой мощностью.

В одном варианте осуществления процессор 100 выполнен с возможностью исполнения компилятора оптимизации и/или кода 177 транслятора для компиляции, трансляции и/или оптимизации кода 176 приложения для поддержки устройства и способов, описанных в данном документе или для сопряжения с ними. Компилятор часто включает в себя программу или набор программ для трансляции исходного текста/кода в целевой текст/код. Обычно компиляция кода программы/приложения с помощью компилятора выполняется в несколько фаз и передается для преобразования кода языка программирования высокого уровня в машинный код низкого уровня или код на языке Ассемблера. Кроме того, однопроходные компиляторы можно по-прежнему использовать для простой компиляции. Компилятор может использовать любые известные технологии компиляции и выполнять любые известные операции компилятора, такие как лексический анализ, предобработка, синтаксический анализ, семантический анализ, генерацию кода, преобразование кода и оптимизацию кода.

Более крупные компиляторы часто включают в себя несколько фаз, но чаще всего эти фазы включены в две общие фазы: (1) препроцессор, то есть обычно там, где может иметь место синтаксическая обработка, семантическая обработка и некоторые преобразования/оптимизация, и (2) постпроцессор, то есть обычно там, где имеет место анализ, преобразования, оптимизации и генерация кода. Некоторые компиляторы оказываются посередине, что иллюстрирует размывание разграничение между препроцессором и постпроцессором компилятора. В результате, ссылка на вставку, ассоциацию, генерацию и другую операцию компилятора может иметь место в любой из вышеупомянутых фаз или проходов, а также в любых других известных фазах или проходах компилятора. В качестве иллюстративного примера, компилятор потенциально вставляет операции, вызовы, функции и т.д. в одну или более фаз компиляции, такие как вставка вызовов/операций на фазе предварительной обработки компиляции и затем преобразования вызовов/операций в код более низкого уровня во время фазы преобразования. Следует отметить, что во время динамической компиляции, код компилятора или код динамической оптимизации позволяет вставлять такие операции/вызовы, а также оптимизировать код для исполнения во время прогона. В качестве конкретного иллюстративного примера, двоичный код (уже компилированный код) можно динамическим образом оптимизировать во время прогона. В данном случае, программный код может включать в себя код динамической оптимизации, двоичный код или их комбинацию.

Аналогично компилятору, транслятор, такой как двоичный транслятор, транслирует код либо статическим, либо динамическим образом для оптимизации и/или трансляции кода. После этого ссылка на исполнение кода, кода приложения, кода программы или другой программной среды может относиться к: (1) исполнение программ(ы) компилятора, оптимизатора кода оптимизации или транслятора динамическим или статистическим образом для компиляции программного кода, для поддержания программных структур, для выполнения других операций, для оптимизации кода или для трансляции кода; (2) исполнение главного программного кода, включающего в себя операции/вызовы, такие как код прикладной программы, который был оптимизирован/компилирован; (3) исполнение другого программного кода, такого как библиотеки, ассоциированные с главным программным кодом для поддержания программных структур, для выполнения других операций, которые относятся к программному обеспечению или для оптимизации кода; или (4) их комбинации.

В некоторых реализациях контроллер 160 управления мощностью можно также выполнить и реализовать в виде аппаратных средств и программного обеспечения. Система и устройства, подсоединенные к системе, могут поддерживать многочисленные состояния мощности, включая полную мощность, низкую мощность и состояние без мощности, среди прочих (например, промежуточных) состояний или условий. Контроллер 160 управления мощностью может выполнять функции и выполнять задачи для оказания содействия при минимизации потребления мощности системой, тепловых ограничений системы управления и максимизации срока службы аккумулятора системы среди прочих функциональных возможностей. Управление мощностью может включать в себя управление другими функциональными возможностями и характеристиками системы, в том числе быстродействием системы, шумом, сроком службы аккумулятора и потреблением мощности переменного тока среди прочих примеров.

Накристальный интерфейс может включать в себя модуль 104 времени возобновления. Модуль 104 времени возобновления может включать в себя процессор 182 и память 184. Накристальный интерфейс 110 и устройство 180 могут поддерживать связь через высокоскоростную шину последовательного ввода-вывода (PCIe) совместимое или другое соединение. В некоторых протоколах межсоединений, таких как межсоединения периферийных компонентов (PCI) и (PCIe), можно предусмотреть архитектурные механизмы для задержки входов устройств в состояние полной мощности (например, в связи с определенными политиками и возможностями управления мощностью). Например, программное обеспечение, такое как логика управления мощностью операционной системы устройства позволяет по меньшей мере частично, управлять входами и выходами в различных состояниях мощности. В некоторых примерах, политики платформ могут обеспечить минимальные периоды восстановления (задержки), прежде разрешить программному обеспечению выдавать запросы на конфигурацию в устройства, например, в связи с инициированием состояния мощности. Например, чтобы улучшить использование мощности в режиме ожидания, политики функциональной возможности управления мощностью могут попытаться разместить устройство, включающее в себя дискретные присоединенные устройства, корневые порты (RP) и корневые комплексные интегральные конечные точки (RCIE) и т.д., а также внешние устройства, соединенные поверх межсоединения, в состояниях с управлением мощностью, где мощность в этих устройствах можно выключить, устройства могут работать в состоянии с пониженной мощностью, или эти устройства могут работать в условиях резервной мощности. После возобновления работы из этих состояний мощности, программное обеспечение ожидает в течение конкретного периода времени (например, 10 мс, 100 мс и т.д.), прежде чем оно будет выдавать запросы на конфигурацию. Это может иметь значительное влияние на время возобновления. Такие определенные минимальные периоды времени восстановления, несмотря на то, что они являются преимущественными в некоторых контекстах и в связи с некоторыми устройствами, тем не менее, могут быть нежелательными в других контекстах и в связи с другими устройствами.

В некоторых реализациях накристальный интерфейс может включать в себя модуль 104 времени возобновления. Модуль 104 времени возобновления может включать в себя процессор 182 и память 184. Модуль 104 времени возобновления можно сконфигурировать таким образом, чтобы разрешить внутреннему устройству, такому как корневой порт, назначенный порт (DP) или RCIE информировать о времени восстановления, специфическом для устройства, показывая то, как скоро после перехода в состояние мощности (например, первоначальная подача мощности, переход из D3 в D0 и т.д.) устройство будет готово для первой конфигурации (например, в связи с программным обеспечением). В варианте осуществления модуль 104 времени возобновления может дополнительно включать в себя механизм прерывания (например, описание производительности, механизм управления для разрешения прерываний) для внутренних устройств, чтобы запускать прерывание в том случае, когда оно завершается или готово для завершения перехода между состояниями мощности (например, первоначальная подача мощности, переход D3-D0 и т.д.), чтобы дополнительно усилить окончание в предварительно установленном периоде времени восстановления или в противном случае инициировать задачи конфигурации, которые будут выполняться программным обеспечением.

В некоторых реализациях возможности периода времени возобновления, конкретного для устройства, можно определить в одном или более регистров возможностей, и они могут быть доступны одному или более инструментам управления мощностью, в том числе инструментам на основе программного обеспечения. В одном примере во время подсчета устройств (например, одного или более устройств 180, в том числе внешних или внутренних устройств) модуль 104 времени возобновления может осуществлять доступ к возможностям времени возобновления устройства и может сохранять их в памяти 184 для дальнейшего использования. Модуль 104 времени возобновления может также считывать возможности прерывания устройства и реализовывать механизм прерывания вместо механизма опроса с возможностью запуска и распознавания прерывания в том случае, когда внутреннее устройство готово для доступа к конфигурации. Например, в некоторой точке внутреннее устройство может переходить в состояние низкой мощности. В варианте осуществления модуль 104 времени возобновления может определить, что внутреннее устройство должно переходить из состояния низкой мощности в состояние полной мощности. Кроме того, модуль 104 времени возобновления может извлекать объявленное значение времени возобновления для устройства 180 из памяти 184 и затем выдавать первый запрос на конфигурацию после ожидания периода времени в памяти 184, который был объявлен внутренним устройством в соответствующей структуре возможностей среди прочих примеров.

В другом варианте осуществления модуль 104 времени возобновления может определить, что он собирается применить мощность к подсистеме, которая управляла устройством 180. Если устройство 180 выполнено с возможностью передачи прерывания в случае, когда устройство 180 вышло из состояния с низкой мощностью, модуль 104 времени возобновления может ожидать прерывания, которое будет получено из устройства 180, показывать, что оно готово для первого доступа к конфигурации. В обоих случаях модуль времени возобновления может удалить фиксированное архитектурное время ожидания 100 мс перед осуществлением доступа к устройству с помощью первого доступа к конфигурации. Модуль 104 времени возобновления может также удалить фиксированное архитектурное время ожидания для программного обеспечения перед доступом к устройству с помощью первого доступа к конфигурации после записи в регистре статуса и управления мощностью (PMCSR). Чтобы поддержать совместимость с предыдущими версиями, архитектурные периоды времени восстановления (например, унаследованную задержку 100 мс или 10 мс (для доступа после записи (PMCSR)) не следует увеличивать с помощью модуля 104 времени возобновления и можно поддержать в качестве режима по умолчанию для устройств, которые не используют обычные возможности времени возобновления. Как изложено выше, накристальный интерфейс ПО и устройство 180 могут поддерживать связь через соединение по линии связи, такое как PCIe, MIPI, QPI или другие линии межсоединений, совместимые с протоколом.

Основная цель PCIe состоит в том, чтобы обеспечить возможность компонентам и устройствам от разных производителей совместно функционировать в открытой архитектуре, охватывающей многочисленные сегменты рынка; клиенты (настольные компьютерные и мобильные устройства), серверы (стандартные и промышленные), и встроенные и коммуникационные устройства. PCIe имеет высокую производительность межсоединения ввода/вывода общего назначения, определенное для большого разнообразия будущих вычислительных и коммуникационных платформ. Некоторые атрибуты PCI, такие как ее модель применения, архитектура нагрузки-хранения и программные интерфейсы, поддерживались через их поправки, тогда как предыдущие реализации параллельной шины были заменены на высоко масштабируемый, полностью последовательный интерфейс. Более поздние версии PCIe являются преимущественными благодаря достижениям в двухточечных межсоединениях, технологии на основе переключения и пакетированию протокола для доставки новых уровней производительности и особенностей. Управление мощностью, качество обслуживания (QoS), поддержка активного соединения/замена непосредственно в процессе работы, целостность данных и устранение ошибок представляют собой одни из расширенных функциональных возможностей, поддерживаемых PCIe.

Со ссылкой на фиг. 2 иллюстрирован вариант осуществления структур, состоящих из двухточечных линий связи, которые обеспечивают межсоединение набора компонентов. Система 200 включает в себя процессор 205 и системную память 210, подсоединенную к концентратору 215 контроллера. Процессор 205 включает в себя любой процессорный элемент, такой как микропроцессор, хост-процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 205 соединен с концентратором 215 контроллера через управляющую шину (FSB) 206. В одном варианте осуществления, FSB 206 представляет собой последовательное двухточечное межсоединение, как описано ниже. В другом варианте осуществления линия 206 связи включает в себя последовательную дифференциальную архитектуру межсоединений, которая совместима с различными стандартами межсоединений.

Системная память 210 включает в себя устройство памяти, такое как оперативное запоминающее устройство (RAM), энергонезависимую (NV) память или другую память, доступ к которым осуществляется с помощью устройств в системе 200. Системная память 210 соединена с концентратором 215 контроллера через интерфейс 216 памяти. Примеры интерфейса памяти включают в себя интерфейс памяти с удвоенной скоростью передачи данных (DDR), интерфейс памяти с двухканальной DDR и интерфейс памяти с динамическим RAM (DRAM).

В одном варианте осуществления концентратор 215 контроллера представляет собой корневой концентратор, корневой комплекс или корневой контроллер в иерархии межсоединений PCIe. Примеры концентратора 215 контроллера включают в себя микропроцессорный набор, концентратор контроллера памяти (МСН), северный мост, концентратор контроллера межсоединений (ICH), южный мост и корневой контроллер/концентратор. Часто термин "микропроцессорный" набор относится к двум физически отдельным концентраторам контроллера, то есть к концентратору контроллера памяти (МСН), соединенному с концентратором контроллера межсоединений (ICH). Следует отметить, что данные системы часто включают в себя МСН, выполненные как единое целое с процессором 205, тогда как контроллер 215 должен поддерживать связь с устройствами ввода/вывода аналогичным образом, как описано ниже. В некоторых вариантах осуществления одноранговая маршрутизация дополнительно поддерживается через корневой к