Модуль сопроцессора кэша

Иллюстрации

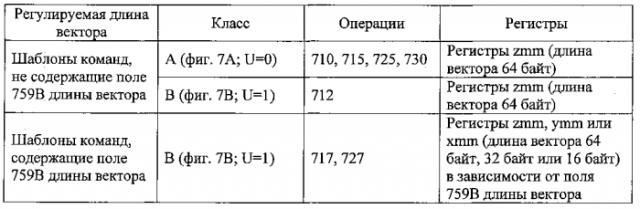

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в уменьшении операций загрузки и сохранения, осуществляемых между исполнительным кластером и модулем сопроцессора кэша. Модуль сопроцессора кэша в компьютерной системе содержит массив кэша для хранения данных; аппаратный декодирующий модуль для декодирования команд, выгружаемых из потока выполнения исполнительным кластером компьютерной системы, для уменьшения операций загрузки и сохранения, осуществляемых между исполнительным кластером и модулем сопроцессора кэша; группу из одного или более операционных модулей для выполнения множества операций с массивом кэша в соответствии с декодированными командами; при этом модуль выгрузки команд выполнен с возможностью выдачи команд напрямую в модуль сопроцессора кэша для выгрузки выполнения указанных команд в модуль сопроцессора кэша. 3 н. и 18 з.п. ф-лы, 25 ил., 1 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к архитектуре процессора компьютера и, более конкретно, к модулю сопроцессора кэша.

Уровень техники

Набор команд или структура набора команд (ISA) представляет собой часть архитектуры компьютера, относящуюся к программированию, и может содержать различные виды внутренних данных, команды, архитектуру регистров, режимы адресации, архитектуру памяти, обработку прерываний и особых ситуаций, а также внешний ввод и вывод (I/O). Следует отметить, что термин команда здесь обычно относится к макрокоманде, т.е. команде, направляемой в процессор для выполнения, в отличие от микрокоманды или микрооперации, являющихся результатом декодирования макрокоманд посредством декодера процессора.

Структура набора команд отличается от микроархитектуры, представляющей собой внутреннюю конструкцию процессора, реализующего структуру ISA. Процессоры с различными микроархитектурами могут использовать общий набор команд. Набор команд содержит один или более форматов команд. Конкретный набор команд определяет разнообразные поля (число битов, расположение битов) для спецификации, помимо всего прочего, операции, которую нужно выполнить, и операнд(ы), над которыми должна быть выполнена эта операция. Конкретную команду представляют с использованием конкретного формата команд, и эта команда определяет и операцию, и операнд(ы). Поток команд представляет собой определенную последовательность команд, где каждая команда в последовательности является событием команды в некоем формате команды.

Разного рода научные, финансовые приложения, автоматически векторизуемые приложения общего назначения, приложения RMS (распознавание, анализ и синтез)/визуальные и мультимедийные (например, 2D/3D графика, обработка изображения, сжатие/расширение видео, алгоритмы распознавания речи и манипуляции со звуком) приложения часто требуют, чтобы одна и та же операция была выполнена над большим числом элементов данных (именуется «параллелизмом данных»). Название «одна команда, множество данных» (SIMD) обозначает тип команд, в соответствии с которыми процессор выполняет одну и ту же операцию применительно к множеству объектов данных. Технология SIMD специально приспособлена для процессоров, способных разбивать биты в регистре на некоторое число элементов данных фиксированного размера, каждый из которых представляет отдельную величину. Например, биты в 64-битовом регистре могут быть определены как операнд-источник, работать с которым следует как с четырьмя отдельными 16-битовыми элементами данных, каждый из которых представляет отдельную 16-битовую величину. В качестве другого примера, биты в 256-битовом регистре могут быть определены как операнд-источник, работать с которым следует как с четырьмя отдельными 64-битовыми упакованными элементами данных (элементы данных размером со счетверенное слово (Q)), восемью отдельными 32-битовыми упакованными элементами данных (элементы данных размером со сдвоенное слово (D)), шестнадцатью отдельными 16-битовыми упакованными элементами данных (элементы данных размером в одно слово (W)) или тридцатью двумя отдельными 8-битовыми элементами данных (элементы данных размером в один байт (В)). Данные такого типа именуются данными упакованного типа (упакованными данными) или данными векторного типа (векторными данными), а операнды данных такого типа называются операндами упакованных данных или векторными операндами. Другими словами термином «объект упакованных данных» или «вектор» обозначают последовательность упакованных элементов, а операнды такого типа именуются операндами упакованных данных или векторными операндами. Другими словами, термин «упакованный объект данных» или «вектор» обозначает последовательность упакованных элементов данных; а операнд упакованных данных или векторный операнд является операндом-источником или операндом-адресатом для SIMD-команды (также называемой «команда для упакованных данных» или «векторная команда»).

Операция транспонирования является общеупотребительной элементарной операцией (примитивом) для векторного программного обеспечения. Хотя некоторые структуры наборов команд имеют команды для осуществления операции транспонирования, эти команды обычно производят перетасовку и перестановку, что требует дополнительных издержек, чтобы задать маски управления перетасовкой с использованием битов непосредственной адресации или с использованием отдельного векторного регистра, увеличивая тем самым нагрузку команд и увеличивая размеры. Кроме того, операции перетасовки в некоторых структурах наборов команд являются 128-битовыми операциями. В результате для осуществления операции полного транспонирования применительно к 256-битовому регистру или 512-битовому регистру (например) необходимо сочетание перетасовок и перестановок.

Программные приложения расходуют значительную долю времени на операции загрузки (LD) и сохранения (ST) в памяти, причем число операций загрузки обычно более чем вдвое превосходит число сохранений в памяти. Некоторые функции, требующие многочисленных операций загрузки и сохранения, почти не требуют вычислений - это, например, очистка памяти, копирование памяти, транспонирование; а другие используют незначительный объем вычислений - это например, вычисление скалярного произведения матриц, суммирование массивов и т.п. Каждая операция загрузки или операция сохранения требует использования ресурсов ядра (например, станций резервации (RS), буфера переупорядочения (ROB), буферов заполнения и т.п.).

Краткое описание чертежей

Настоящее изобретение иллюстрируется примером и не ограничивается прилагаемыми чертежами, на которых подобные позиционные обозначения присвоены аналогичным элементам и на которых:

фиг. 1 иллюстрирует пример выполнения команды транспонирования согласно одному из вариантов;

фиг. 2 иллюстрирует другой пример выполнения команды транспонирования согласно одному из вариантов;

фиг. 3 представляет логическую схему, иллюстрирующую пример операций транспонирования элементов данных в векторном регистре или в позиции памяти путем выполнения одной команды транспонирования согласно одному из вариантов;

фиг. 4 представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров, содержащего пример модуля сопроцессора кэша, выполняющего команды, которые были выгружены, чтобы их не выполнял исполнительный кластер процессорного ядра, согласно одному из вариантов;

фиг. 5 представляет блок-схему, иллюстрирующую пример операций для выполнения выгруженной команды согласно одному из вариантов;

фиг. 6А иллюстрирует пример формата команды AVX, содержащего префикс VEX, поле кода операции реального режима, байт Mod R/M, байт SIB, поле смещения и IMM8 согласно одному из вариантов;

фиг. 6В показывает, какие поля из представленных на фиг. 6А составляют поле полного кода операции и поле базовой операции согласно одному из вариантов;

фиг. 6С показывает, какие поля из представленных на фиг. 6А составляют поле индекса регистра согласно одному из вариантов;

фиг. 7А представляет блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблон команд класса А в этом формате согласно вариантам настоящего изобретения;

фиг. 7В представляет блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблон команд класса В в этом формате согласно вариантам настоящего изобретения;

фиг. 8А представляет блок-схему, иллюстрирующую пример специального удобного для работы с векторами формата команд согласно вариантам настоящего изобретения;

фиг. 8В представляет блок-схему, иллюстрирующую поля показанного на фиг. 8А конкретного удобного для работы с векторами формата команд, составляющие поле полного кода операции согласно одному из вариантов настоящего изобретения;

фиг. 8С представляет блок-схему, иллюстрирующую поля конкретного удобного для работы с векторами формата команд, составляющие поле индекса регистра согласно одному из вариантов настоящего изобретения;

фиг. 8D представляет блок-схему, иллюстрирующую поля конкретного удобного для работы с векторами формата команд, составляющие поле дополнительной операции согласно одному из вариантов настоящего изобретения;

фиг. 9 представляет блок-схему регистровой архитектуры согласно одному из вариантов настоящего изобретения;

фиг. 10А представляет блок-схему, иллюстрирующую пример конвейера, выполняющего команды по порядку, и пример конвейера с выдачей данных/выполнением команд не по порядку и переименованием регистров согласно вариантам настоящего изобретения;

фиг. 10В представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей данных/выполнением команд не по порядку и переименованием регистров для включения в состав процессора согласно вариантам настоящего изобретения;

фиг. 11А представляет блок-схему одного ядра процессора вместе с его соединением с выполненной на кристалле соединительной схемой и с его локальным подмножеством кэша Уровня 2 (L2) согласно вариантам настоящего изобретения;

фиг. 11В представляет расширенное изображение части ядра процессора, показанного на фиг. 11А, согласно вариантам настоящего изобретения;

фиг. 12 представляет блок-схему процессора, который может иметь больше одного ядра, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам настоящего изобретения;

фиг. 13 представляет блок-схему системы согласно одному из вариантов настоящего изобретения;

фиг. 14 представляет блок-схему первого более конкретного примера системы согласно одному из вариантов настоящего изобретения;

фиг. 15 представляет блок-схему второго более конкретного примера системы согласно одному из вариантов настоящего изобретения;

фиг. 16 представляет блок-схему «системы на кристалле» (SoC) согласно одному из вариантов настоящего изобретения; и

фиг. 17 представляет блок-схему сравнения использования программного преобразователя команд с целью преобразования двоичных команд из состава исходного набора команд в двоичные команды из состава целевого набора команд согласно вариантам настоящего изобретения.

Осуществление

В последующем описании приведены многочисленные конкретные детали. Однако понятно, что варианты настоящего изобретения могут быть практически реализованы и без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и способы не были показаны подробно, чтобы не затруднять понимание настоящего описания.

Ссылки в настоящем описании на «один вариант», «некоторый вариант», «пример варианта» и т.п. означают, что описываемый вариант может иметь конкретный признак, структуру или характеристику, но каждый вариант совсем не обязательно содержит этот конкретный признак, структуру или характеристику. Более того, такая фраза совсем не обязательно относится к тому же самому варианту. Далее, когда конкретный признак, структура или характеристика описывается в связи с каким-либо вариантом, предполагается, что у специалиста в рассматриваемой области достаточно знаний, чтобы применить их в других вариантах, независимо от того, описано такое применение в явном виде или нет.

Команда транспонирования

Как подробно описано ранее, операцию транспонирования элементов традиционно выполняли в виде сочетания операций перетасовки и перестановки, что требует дополнительных издержек задания масок управления перетасовкой с использованием самих ближайших битов или с использованием отдельного векторного регистра, что увеличивает нагрузку и размер команд.

Варианты команды транспонирования (Transpose) подробно рассмотрены ниже, равно как и варианты, систем, архитектур, форматов команд и т.п., которые могут быть использованы для выполнения такой команды. Команда транспонирования содержит операнд, определяющий векторный регистр или позицию в памяти. При выполнении команды транспонирования процессор сохраняет элементы данных, записанные в определенном векторном регистре или позиции памяти, в порядке, обратном первоначальному порядку. Например, наиболее значимый («самый старший») элемент данных становится наименее значимым («самым младшим») элементом данных, наименее значимый элемент данных становится наиболее значимым элементом данных и т.д.

В некоторых вариантах, если команда определяет позицию в памяти, эта команда дополнительно содержит операнд, указывающий число элементов.

В некоторых вариантах, как будет подробно описано позднее, команду транспонирования выгружают для выполнения в модуле сопроцессора кэша.

Один из примеров этой команды выглядит так "Transpose [PS/PD/B/W/D/Q] Vector_Register/Memory", где параметр Vector_Register указывает векторный регистр (такой как 128, 256 или 512-битовый регистр), а параметр Memory указывает позиции в памяти. Участок "PS" команды обозначает скалярную плавающую запятую (4 байта). Участок "PD" команды указывает плавающую запятую для двойного формата (8 байт). Участок "В" обозначает байт, независимо от атрибута размера операнда. Участок "W" команды обозначает слово, независимо от атрибута размера операнда. Участок "D" команды обозначает сдвоенное слово, независимо от атрибута размера операнда. Участок "Q" команды обозначает счетверенное слово, независимо от атрибута размера операнда.

Определенный векторный регистр или позиция памяти является и источником, и адресатом операции. В результате выполнения команды транспонирования элементы данных, находящиеся в определенном векторном регистре или позиции памяти, сохраняют в порядке, обратном первоначальному порядку, в этом же определенном векторном регистре или позиции памяти.

Другой пример этой команды выглядит так "Transpose [PS/PD/B/W/D/Q] Memory, Num_Elements", где параметр Memory обозначает позиции в памяти, а параметр Num_Elements обозначает число элементов. В одном из вариантов команду такого вида выгружают и выполняют в модуле сопроцессора кэша.

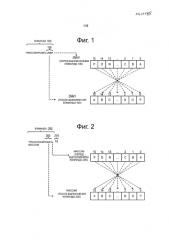

Фиг. 1 иллюстрирует пример выполнения команды транспонирования согласно одному из вариантов. Команда 100 транспонирования содержит операнд 105. Эта команда 100 транспонирования принадлежит к структуре набора команд, и каждое «появление» такой команды 100 в потоке команд должно содержать величины в операнде 105. В этом примере операнд 105 определяет векторный регистр (такой как 128-, 256- или 512-битовый регистр). В качестве такого векторного регистра показан регистр zmm с 16 32-битовыми элементами данных; однако здесь могут быть использованы и другие размеры элементов данных и регистров, например, регистры xmm или ymm с 16-битовыми или 64-битовыми элементами данных.

Содержимое регистра, определенное операндом 105 (zmml), представлено, как показано на чертеже, 16 элементами данных. Фиг. 1 иллюстрирует регистр zmml до выполнения команды 100 транспонирования и после выполнения этой команды 100. Перед выполнением команды 100 транспонирования элемент данных с индексом 0 в регистре zmml сохраняет величину А, элемент данных с индексом 1 в регистре zmml сохраняет величину В, и т.д., так что последний элемент данных с индексом 15 в регистре zmml сохраняет величину Р. Выполнение команды 100 транспонирования вызывает пересохранение элементов данных, находившихся в регистре zmml, в этом же регистре, но в обратном порядке. Таким образом, элемент данных с индексом 0 в регистре zmml сохраняет величину Ρ (которая раньше находилась под индексом 15 в регистре zmml), элемент данных с индексом 1 сохраняет величину О (которая раньше находилась под индексом 14), и т.д., так что элемент данных с индексом 15 сохраняет величину А (которая раньше находилась под индексом 0).

Фиг. 2 иллюстрирует другой пример выполнения команды транспонирования. Команда 200 транспонирования содержит операнд 205 и операнд 210. Операнд 205 определяет позицию в памяти (в которой в этом примере хранится массив данных), а операнд 210 указывает число элементов (которое в этом примере равно 16). Перед выполнением команды 200 транспонирования элемент данных с индексом 0 в массиве сохраняет величину А, элемент данных с индексом 1 в массиве сохраняет величину В и т.д., а последний элемент данных с индексом 15 в массиве сохраняет величину Р. Выполнение команды 200 транспонирования вызывает пересохранение элементов данных, находившихся в массиве, в этом же массиве, но в обратном порядке относительно первоначального порядка. Таким образом, элемент данных с индексом 0 в массиве сохраняет величину Ρ (которая раньше находилась в массиве под индексом 15), элемент данных с индексом 1 сохраняет величину О (которая раньше находилась под индексом 14), и т.д., так что элемент данных с индексом 15 сохраняет величину А (которая раньше находилась под индексом 0).

Фиг. 3 представляет логическую схему, иллюстрирующую пример операций для транспонирования элементов данных в векторном регистре или в позиции памяти при выполнении одной команды транспонирования согласно одному из вариантов. На операции 310 процессор выбирает команду транспонирования (например, посредством модуля выборки в составе процессора). Эта команда транспонирования содержит операнд, определяющий векторный регистр или позицию в памяти. Специфицированный векторный регистр или позиция в памяти содержит несколько элементов данных, которые нужно транспонировать. Векторный регистр может, например, представлять собой регистр zmm, имеющий 16 32-битовых элементов данных; однако здесь могут быть использованы и другие размеры элементов данных и регистров, например, регистры xmm или ymm с 16-битовыми или 64-битовыми элементами данных.

Процесс переходит от операции 310 к операции 315, где процессор декодирует команду транспонирования. Например, в некоторых вариантах, процессор содержит аппаратный декодирующий модуль, куда поступает команда (например, от модуля выборки в составе процессор). В качестве декодирующего модуля могут быть использованы самые разнообразные и хорошо известные декодирующие модули. Например, такой декодирующий модуль может декодировать команду транспонирования и превратить ее в одну широкую микрокоманду. В качестве другого примера декодирующий модуль может декодировать команду транспонирования и превратить ее в несколько широких микрокоманд. Еще в одном примере, особенно хорошо подходящем для конвейерных систем, выполняющих команды не по порядку, декодирующий модуль может декодировать команду транспонирования и превратить ее в одну или несколько микроопераций, где каждая такая микрооперация может быть выдана и выполнена не по порядку (с изменением очередности). Кроме того, декодирующий модуль может быть реализован в составе одного или нескольких декодеров, причем каждый декодер может быть выполнен в виде программируемой логической матрицы (PLA), как это хорошо известно в технике. В качестве примера, конкретный декодирующий модуль может содержать: 1) управляющую логическую схему, направляющую различные макрокоманды в разные декодеры; 2) первый декодер, который может декодировать подмножество набора команд (но больше, чем это может делать каждый из второго, третьего и четвертого декодеров) и генерировать две микрооперации за один раз; 3) второй, третий и четвертый декодеры, каждый из которых может декодировать только подмножество всего набора команд и генерировать только одну микрооперацию за один раз; 4) ROM коммутатора микрокоманд, которое может декодировать только подмножество всего набора команд и генерировать четыре микрооперации за один раз; и 5) мультиплексорную логическую схему, получающую на входы микрокоманды от декодеров и от ROM коммутатора микрокоманд и определяющую, выходную команду какого из этих модулей поставить в очередь микроопераций. Другие варианты декодирующего модуля могут содержать больше или меньше декодеров, способных декодировать больше или меньше команд и подмножеств команд. Например, один вариант может содержать второй, третий и четвертый декодеры, каждый из которых может генерировать по две микрооперации за один раз; и может содержать ROM коммутатора микрокоманд, которое генерирует по восемь микроопераций за один раз.

Далее процедура переходит к операции 320, в ходе которой процессор выполняет команду транспонирования, вызывающую сохранение элементов данных, находящихся в некотором порядке в определенном векторном регистре или позиции памяти, в этом же определенном регистре или позиции памяти, но в порядке, обратном первоначальному порядку.

Команду транспонирования может автоматически генерировать компилятор, либо ее может закодировать вручную разработчик программного обеспечения. Выполнение описанной здесь команды транспонирования улучшает программируемость структуры набора команд и уменьшает число команд, снижая тем самым потребление энергии в ядре. Кроме того, выполнение команды транспонирования происходит, не требуя создания временного буфера для сохранения транспонированных элементов в памяти, в отличие от традиционных способов выполнения операции транспонирования, что уменьшает требования к размеру памяти. Кроме того, выполнение одной команды транспонирования проще, чем выполнение сложного набора перетасовок и перестановок, который раньше требовался для осуществления операций транспонирования.

Выгрузка команд для выполнения модулем сопроцессора кэша

Как подробно описано ранее, программные приложения могут содержать функции, обычно требующие выполнения некоторого числа операций загрузки и/или сохранения между исполнительным кластером процессорного ядра и модулем памяти (кэшем и памятью) компьютерной системы. Некоторые из этих функций почти не требуют вычислений, но могут потребовать большого числа операций загрузки и/или сохранения, таких как очистка памяти, копирование памяти и транспонирование. Другие функции, такие как вычисление скалярного произведения матриц и суммирование массивов требуют небольшого объема вычислений, но также могут потребовать большого числа операций загрузки и/или сохранения. Например, для выполнения операции транспонирования массива памяти этот массив памяти следует загрузить в регистр, ядро обратит порядок следования величин, после чего эти величины снова сохраняют в массиве памяти (эти этапы может потребоваться повторить несколько раз прежде, чем будет транспонирован весь массив памяти).

Варианты настоящего изобретения описывают модуль процессора кэша, выполняющий команды, выгруженные, чтобы не выполнять их посредством исполнительного кластера компьютерной системы. Например, некоторые функции управления памятью (такие как очистка памяти, копирование памяти, транспонирование и т.п.) выгружают, чтобы их не выполнял исполнительный кластер компьютерной системы, и выполняют непосредственно в модуле сопроцессора кэша (который может содержать данные, над которыми производятся операции). В качестве другого примера, команды, которые требуют проведения постоянной вычислительной операции в непрерывной области массива кэша в модуле сопроцессора кэша, могут быть выгружены в этот модуль сопроцессора кэша и выполнены им (например, скалярное произведение матриц, суммирование массивов и т.п.). Выгрузка этих команд в модуль сопроцессора кэша уменьшает число операций загрузки и сохранения между модулем процессора кэша и исполнительным кластером компьютерной системы, что уменьшает число команд, освобождает ресурсы исполнительного кластера (например, станций резервации (RS), буфера переупорядочения (ROB), буферов заполнения и т.п.), и тем самым позволяет исполнительному кластеру использовать эти ресурсы для выполнения других команд.

Фиг. 4 представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров, содержащего пример модуля сопроцессора кэша, выполняющего команды, которые были выгружены, чтобы их не выполнял исполнительный кластер процессорного ядра, согласно одному из вариантов. Прямоугольниками из сплошных линий на фиг. 4 обозначены компоненты конвейера с выполнением команд по порядку и ядра с выполнением команд по порядку, тогда как добавленные в качестве компоненты в прямоугольниках из штриховых линий обозначают компоненты конвейера и ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров. Поскольку аспект выполнения команд по порядку являются частью аспекта с выполнением команд не по порядку, далее будет описан аспект с выполнением команд не по порядку.

Как показано на фиг. 4, процессорное ядро 400 содержит модуль 410 ввода, соединенный с исполнительным модулем 415, который соединен с модулем 470 сопроцессора кэша. Процессорное ядро 400 может представлять собой компьютерное ядро с уменьшенным набором команд (RISC), ядро со сложным набором команд (CISC), ядро с очень длинным командным словом (VLIW), либо ядро гибридного или альтернативного типа. Еще в одном варианте ядро 400 может представлять собой ядро специального назначения, такое как, например, сетевое ядро или ядро связи, автомат сжатия, сопроцессорное ядро, ядро графического процессора общего назначения (GPGPU), графическое ядро или другое подобное ядро.

Входной модуль 410 содержит модуль 420 выборки команд, соединенный с декодирующим модулем 425. Этот декодирующий модуль 425 (или декодер) конфигурирован для декодирования команд и генерации на выходе одной или нескольких микроопераций, точек ввода микрокодов, микрокоманд, других команд или других сигналов управления, которые декодированы на основе, или как-то иначе отражают или выведены из исходных команд. Такой декодирующий модуль 425 может быть реализован с использованием разнообразных механизмов. К примерам подходящих механизмов относятся, не ограничиваясь этим, просмотровые таблицы, аппаратные реализации, программируемые логические матрицы (PLA), ROM микрокодов и т.п. В одном из вариантов, ядро 400 содержит ROM микрокодов или другой носитель, сохраняющий микрокоды для определенных макрокоманд (например, в декодирующем модуле 425 или, в ином случае, в модуле 410 ввода). Указанный декодирующий модуль 425 соединен с модулем 435 переименования/назначения в составе исполнительного модуля 415. Хотя на фиг. 1 это не показано, модуль 410 ввода может также содержать модуль прогнозирования ветвления, соединенный с модулем кэша команд, который в свою очередь соединен с буфером ассоциативной трансляции (TLB), связанным с модулем выборки команд 420.

Декодирующий модуль 425 также конфигурирован для определения, следует ли выгрузить какую-либо команду в модуль 470 сопроцессора кэша. В одном из вариантов, решение о выгрузке команды в модуль 470 сопроцессора кэша принимается динамически (во время выполнения программы) и зависит от архитектуры. Например, в одном из вариантов команда может быть выгружена, если ее длина в памяти больше длины кэш-линии (например, 64 байта) и если она кратна длине кэш-линии. В другом варианте решение о выгрузке команды в модуль 470 сопроцессора кэша может быть принято независимо от длины этой команды в памяти, а в зависимости от эффективности модуля 470 сопроцессора кэша.

В другом варианте при принятии решения о выгрузке команды в модуль 470 сопроцессора кэша может также учитываться сама команда. Иными словами, некоторые команды могут быть специально предназначены для выгрузки в модуль 470 сопроцессора кэша или по меньшей мере могут быть (допускают) выгружены в этот модуль 470 сопроцессора кэша. В качестве примера, такая команда может быть сформирована компьютером или написана разработчиком программного обеспечения на основе того, что такую команду было бы более эффективно выгрузить в модуль сопроцессора кэша.

Указанный исполнительный модуль 415 содержит модуль 435 переименования/назначения, соединенный с модулем 450 выбытия и группой из одного или более модулей планировщиков 440. Модули 440 планировщики представляют собой любое число различных планировщиков, включая станции резервации, центральное командное окно и т.п. Модули 440 планировщиков соединены с модулями 445 физических регистровых файлов. Каждый из этих модулей 445 физических регистровых файлов представляет один или более физических регистровых файлов, так что разные файлы сохраняют один или более различных типов данных, такие как скалярные целочисленные данные, скалярные данные с плавающей запятой, упакованные целочисленные данные, упакованные данные с плавающей запятой, векторные целочисленные данные, векторные данные с плавающей запятой, данные состояния (например, указатель команды, представляющий собой адрес следующей команды, которую нужно выполнить) и т.п. В одном из вариантов, модуль 445 физических регистровых файлов содержит модуль векторных регистров, модуль регистров масок записи и модуль скалярных регистров. Эти регистровые модули могут предоставлять архитектурные векторные регистры, регистры векторных масок и регистры общего назначения. На модули 445 физических регистровых файлов наложен модуль 450 выбытия для иллюстрации различных способов, которыми может быть реализовано переименование регистров и выполнение команд не по порядку (например, с использованием буфера(ов) переупорядочения и регистровых файлов выбытия; с использованием будущих файлов, буфера(ов) предыстории и регистровых файлов выбытия; с использованием карт регистров и пула регистров; и т.п.). Указанные модуль 450 выбытия и модули 445 физических регистровых файлов соединены с исполнительным кластером(ами) 455.

Исполнительный кластер(ы) 455 содержит группу из одного или более исполнительных модулей 460 и группу модулей 465 доступа к памяти. Исполнительные модули 455 могут осуществлять различные вычислительные операции (например, сдвиги, суммирование, вычитание, умножение) и над различными типами данных (например, скалярными данными с плавающей запятой, упакованными целочисленными данными, упакованными данными с плавающей запятой, векторными целочисленными данными, векторными данными с плавающей запятой). Модули 440 планировщиков, модули 445 физических регистровых файлов и исполнительные кластеры 455 показаны как, возможно, по несколько штук, поскольку в некоторых вариантах создают отдельные конвейеры для некоторых типов данных/операций (например, конвейер для скалярных целочисленных данных, конвейер для скалярных данных с плавающей запятой/упакованных целочисленных данных/упакованных данных с плавающей запятой/векторных целочисленных данных/векторных данных с плавающей запятой и/или конвейер доступа к памяти, так что каждый конвейер имеет свой собственный модуль планировщика, модуль физических регистровых файлов и/или исполнительный кластер - и в случае отдельного конвейера доступа к памяти реализованы некоторые варианты, в которых только исполнительный кластер этого конвейера имеет модули 465 доступа к памяти). Следует понимать, что при использовании раздельных конвейеров один или более из этих конвейеров могут использовать выдачу/выполнение не по порядку очередности, а остальные - в порядке очередности.

Группа модулей 465 доступа к памяти соединена с модулем 470 сопроцессора кэша. В одном из вариантов модуль 465 доступа к памяти содержит модуль 484 загрузки, модуль 486 адресов сохранения, модуль 488 сохранения данных и группу из одного или более модулей 490 выгрузки команд, осуществляющих выгрузку команд в модуль 470 сопроцессора кэша. Указанный модуль 484 загрузки выдает операции доступа для загрузки (которые могут иметь форму микроопераций загрузки) в модуль процессора кэша 470. Например, модуль 484 загрузки указывает адрес данных, которые нужно загрузить. Для выполнения операций сохранения используют модуль 486 адресов сохранения и модуль 488 сохранения данных. Здесь модуль 486 адресов сохранения задает адрес, а модуль 488 сохранения данных указывает данные, которые нужно записать в память. В некоторых вариантах, модули загрузки и модули адресов сохранения могут быть использованы либо в качестве модулей загрузки, либо в качестве модулей адресов сохранения.

Как описано ранее, программные приложения могут тратить значительное количество времени и ресурсов на выполнение операций загрузки и сохранения. Например, многие команды, такие как очистка памяти, копирование памяти и транспонирование, обычно требуют выполнения множества команд загрузки, вычисления и сохранения в исполнительных модулях исполнительного кластера ядра. Например, команду загрузки выдают для загрузки данных в регистр(ы), осуществляют вычисление и выдают команду сохранения, чтобы записать полученные в результате данные. Для полного выполнения команды могут потребоваться несколько итеративных циклов этих операций. Операции загрузки и сохранения также используют ширину полосы кэша и памяти, равно как и другие ресурсы ядра (например, станций RS, буфера ROB, буферов заполнения и т.п.).

Модуль(и) 490 выгрузки команд выдает команду(ы) в модуль 470 сопроцессора кэша с целью перенести («выгрузить») выполнение некоторых команд в модуль 470 сопроцессора кэша. Например, выполнение команд, которые обычно требуют значительного числа операций загрузки и/или сохранения, но при этом требуют незначительного (или вообще нулевого) объема вычислений, могут быть выгружены для выполнения прямо в модуль 470 сопроцессора кэша, чтобы уменьшить число операций загрузки и сохранения, которые в противном случае пришлось бы осуществить. Например, функция очистки памяти, функция копирования памяти и функция транспонирования обычно требуют выполнения большого числа операций загрузки и сохранения, но при этом связаны с незначительным (или даже нулевым) объемом вычислений. В одном из вариантов, выполнение этих функций может быть выгружено в модуль 470 сопроцессора кэша. В качестве другого примера в модуль 470 сопроцессора кэша могут быть для выполнения выгружены команды, для которых требуется постоянно выполнять одну и ту же операцию вычисления в непрерывной области данных. Примерами таких команд являются осуществление функций, таких как вычисление скалярного произведения матриц, вычисление суммы массивов и т.п.

Рассматриваемый модуль 470 сопроцессора кэша осуществляет операции с кэшем (например, кэш L1, кэш L2) для ядра 400 и обрабатывает выгруженные команды. Таким образом, модуль 470 сопроцессора кэша обрабатывает обращения для загрузки и обращения для сохранения аналогично тому, как это делает обычный модуль кэша, а также обрабатывает выгруженные команды. Декодирующий модуль 474 в составе модуля 470 сопроцессора кэша содержит логическую схему для декодирования выгруженных команд, а также запросов загрузки, адресов сохранения и запросов на сохранение данных. В одном из вариантов для декодирования каждого запроса используется отдельная управляющая проводная линия между каждым из модулей доступа к памяти и модулем 470 сопроцессора кэша. В другом варианте для уменьшения числа проводных линий используют группу из одного или более управляющих проводов между модулями 465 доступа к памяти и декодирующим модулем 474, управляемым одним или более мультиплексорами.

После декодирования запрошенной операции(й) операционные модули 472 из состава модуля 470 сопроцессора кэша выполняют эти операции. Например, операционный модуль(и) 472 содержит логическую схему для записи данных в массив 482 кэша (для операций сохранения) и считывания данных из массива 482 кэша (для операций загрузки), равно как из любых требуемых буферов. Например, если принят запрос загрузки, операционный модуль(и) 472 обращается в массив кэша по запрошенному адресу и выдает данные (в предположении, что эти данные находились в массиве 482 кэша). В качестве другого примера, если принят запрос сохранения, операционный модуль(и) 472 записывает запрошенные данные по запрашиваемому адресу.

Декодирующий модуль 474 определяет, какие операции должны быть произведены для выполнения выгруженной команды. В качестве примера, в варианте, где выгруженная команда является по существу невычислительной (например, очистка памяти, копирование памяти, транспонирование или другая функция, трансформиру