Комплексное устройство обнаружения

Иллюстрации

Показать всеИзобретение относится к технике радиолокации, радиосвязи, радионавигации и радиоуправления и может быть использовано в радиоэлектронных системах для решения задачи обнаружения сигналов. Достигаемый технический результат - расширение функциональных возможностей устройства в условиях неопределенной помеховой обстановки за счет учета статистической зависимости частных решений обнаружителей. Указанный результат достигается за счет того, что комплексное устройство обнаружения является многоканальным и содержит в каждом канале обнаружитель, два мультиплексора, а в общей для всех каналов части содержит пороговое устройство, два умножителя, сумматор на два входа, два ключа, две ячейки памяти, инвертор и делитель, при этом все перечисленные средства определенным образом соединены между собой. 1 ил., 1 табл..

Реферат

Предлагаемое изобретение относится к технике радиолокации, радиосвязи, радионавигации и радиоуправления и может быть использовано в радиоэлектронных системах для решения задачи обнаружения сигналов.

Известна оптимальная комплексная система обнаружителей (КСО), реализуемая на этапе первичной обработки сигналов [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992, с. 299, рис. 8.4]. Система содержит набор согласованных фильтров и умножителей (по числу l объединяемых обнаружителей), сумматор и пороговое устройство. Аналоговые сигналы, поступающие на входы согласованных фильтров, после их прохождения и домножения на весовые коэффициенты преобразуются в корреляционные интегралы qi ( i = 1, l ¯ ), которые в виде аналоговых реализаций поступают на входы сумматора. На выходе сумматора формируется решающая статистика Z = ∑ i = 1 l q i , поступающая на вход порогового устройства, которое после ее сравнения с заданным порогом вырабатывает решение о наличии или отсутствии сигнала.

Аналогичная КСО имеет место в многопозиционных радиолокационных станциях (МПРЛС) при централизованном обнаружении [Черняк B.C. Многопозиционная радиолокация - М.: Радио и связь, 1993, с. 155], когда по линиям передачи данных (ЛПД) в центр обработки информации (ЦОИ) передаются корреляционные интегралы, сформированные всеми позициями МПРЛС, а решение о наличии или отсутствии сигнала принимается только в ЦОИ после суммирования этих корреляционных интегралов и сравнения полученной суммы с порогом. В случае превышения порога принимается решение о наличии сигнала, в противном случае - об отсутствии сигнала.

К недостаткам системы можно отнести ее громоздкость и сложность в реализации, особенно в многопозиционной радиолокационной станции, где требуется передавать в ЦОИ реализации корреляционных интегралов, что предъявляет высокие требования к пропускной способности ЛПД.

По техническому решению наиболее близким к предлагаемому изобретению является комплексное устройство (система) обнаружения, оптимизированное на этапе вторичной обработки сигналов [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992, с. 298, рис. 8.3], которое и выбрано в качестве прототипа.

Устройство содержит l обнаружителей и l умножителей (является l-канальным), сумматор и пороговое устройство. Выход обнаружителя каждого канала подключен к первому входу умножителя, второй вход которого является внешним. Выход каждого умножителя подключен к соответствующему входу сумматора, выход которого подключен ко входу порогового устройства, выход которого является выходом устройства.

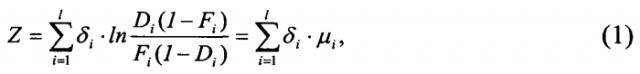

Устройство реализует алгоритм оптимального по критерию Неймана-Пирсона комплексирования обнаружителей на этапе вторичной обработки, который заключается в сравнении с порогом следующей решающей статистики [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992, с. 298]

где i - номер обнаружителя;

l - количество объединяемых обнаружителей;

δi=1; δi=0 - частные решения объединяемых обнаружителей о наличии сигнала или его отсутствии;

Di, Fi - вероятности правильного обнаружения и ложной тревоги соответственно;

Устройство работает следующим образом (рассмотрим работу одного i-го канала устройства, поскольку каналы идентичны).

Аналоговый входной сигнал yit поступает на вход i-го обнаружителя, с выхода которого частное решение δi в виде 1 (сигнал есть) или 0 (сигнала нет) поступает на первый вход умножителя. На второй вход умножителя подается значение весового коэффициента µi, рассчитанное по формуле (2) в зависимости от значений вероятностей ложной тревоги Fi и правильного обнаружения Di. Результат перемножения δi·µi с выхода умножителя поступает на соответствующий вход сумматора. Сформированная в сумматоре решающая статистика (1) подается на вход порогового устройства, где ее значение сравнивается с величиной порога h. В зависимости от результата сравнения пороговое устройство формирует общее решение ϑ=1 (если порог превышен - сигнал есть) или ϑ=0 (порог не превышен - сигнала нет).

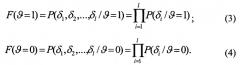

В прототипе частные решения обнаружителей считаются независимыми, поэтому функции правдоподобия принимаемых общих решений записываются в виде

Тогда отношение правдоподобия принимает вид

В зависимости от принятых обнаружителями частных решений (δi=1 или δi=0) частные отношения правдоподобия λi могут быть записаны в виде

Объединяя выражения (6), (7) одной формулой и подставив ее в (5), получим

Одним из недостатков прототипа является то, что обработка частных решений обнаружителей ведется без учета возможного воздействия преднамеренных помех, что влияет на достоверность общего решения. Степень неопределенности помеховой обстановки зададим вероятностью действия помех P(Jam=да). Тогда учет в прототипе изменяющейся помеховой обстановки возможен путем расчета средних значений входящих в (8) вероятностей по формулам

С учетом (9), (10) выражение (8) принимает вид

Однако главным недостатком прототипа уже в условиях возможного применения преднамеренных помех является несостоятельность гипотезы о независимости частных решений обнаружителей, поскольку они становятся статистически зависимыми (условно независимыми при заданном уровне помех Jam). В прототипе этот факт не учитывается, что может привести к снижению достоверности общего решения.

Целью изобретения является расширение функциональных возможностей комплексного устройства обнаружения в условиях неопределенной помеховой обстановки, задаваемой вероятностью действия помех P(Jam=da), за счет учета статистической зависимости частных решений обнаружителей.

Для учета статистической зависимости (условной независимости) частных решений обнаружителей предлагается применить математический аппарат байесовских сетей доверия [Тулупьев А.Л., Николенко С.И., Сироткин А.В. Байесовские сети: Логико-вероятностный подход. - СПб.: Наука, 2006], в соответствии с которым функции правдоподобия принимаемых общих решений могут быть записаны в следующем виде

С учетом (12), (13) отношение правдоподобия принимает вид

Таким образом, в прототипе отношение правдоподобия рассчитывается по формуле (11) с учетом (9), (10), а в предлагаемом устройстве по формуле (14).

Цель изобретения достигается тем, что из известного многоканального устройства, содержащего в каждом канале обнаружитель и умножитель, а также общие для всех каналов сумматор и пороговое устройство, второй вход которого является внешним входом сигнала порогового уровня, а выход является выходом устройства, исключены умножители и многовходовый сумматор, в общую часть устройства дополнительно введены первый и второй умножители, сумматор на два входа, первый и второй ключи, первая и вторая ячейки памяти, инвертор и делитель, а в каждый канал дополнительно введены два мультиплексора, первые адресующие входы которых подключены к выходу соответствующего обнаружителя, а вторые адресующие входы всех мультиплексоров объединены в один вход внешнего сигнала; информационные входы каждого из мультиплексоров являются внешними входами, выходы первых мультиплексоров каждого канала подключены к соответствующим входам первого умножителя, а выходы вторых мультиплексоров каждого канала - к соответствующим входам второго умножителя, дополнительный вход каждого из которых является входом соответствующего внешнего сигнала, а выход подключен к соответствующему входу сумматора, выход которого подключен к информационным входам первого и второго ключей, управляющий вход первого из которых непосредственно, а второго через инвертор подключен ко вторым адресующим входам всех мультиплексоров, причем выход первого ключа через первую ячейку памяти подключен к первому входу делителя, а выход второго ключа через вторую ячейку памяти подключен ко второму входу делителя, выход которого соединен со входом порогового устройства, а входы считывания первой и второй ячеек памяти объединены и являются внешним входом устройства обнаружения.

Сопоставительный анализ с прототипом показывает, что заявляемое многоканальное устройство отличается тем, что из каждого канала исключен умножитель, а из общей части многовходовый сумматор, вместо которых в общую часть дополнительно введены первый и второй умножители, сумматор на два входа, первый и второй ключи, первая и вторая ячейки памяти, инвертор и делитель, а в каждый канал дополнительно введены два мультиплексора. Кроме того, устройство отличается новыми связями указанных блоков между собой и с другими элементами устройства.

Таким образом, заявляемое устройство соответствует критерию изобретения «новизна».

Сравнение заявляемого решения с другими техническими решениями показывает, что вновь введенные элементы известны [Угрюмов Е.П. Цифровая схемотехника. - СПб: БХВ-Петербург, 2001].

Однако при их введении в указанной связи с остальными элементами в заявляемое устройство оно проявляет новые свойства, что приводит к расширению функциональных возможностей устройства в условиях неопределенной помеховой обстановки.

Это позволяет сделать вывод о соответствии технического решения критерию «существенные отличия».

Блок-схема устройства представлена на чертеже.

Устройство является l-канальным (по числу обнаружителей), причем i-ый канал содержит:

1 - обнаружитель, выход которого подключен к первым адресующим входам двух мультиплексоров 2;

2 - два мультиплексора {i/1, i/2), первый адресующий вход каждого из которых подключен к выходу обнаружителя, а второй адресующий вход является общим для всех мультиплексоров внешним входом устройства, непосредственно подключенным к управляющему входу первого ключа 5, а через инвертор 8 - к управляющему входу второго ключа 5. Информационные входы мультиплексоров 2 являются внешними входами устройства. Выход мультиплексора i/1 подключен к соответствующему входу первого умножителя 3, а выход мультиплексора i/2 - к соответствующему входу второго умножителя 3.

Общая часть устройства, объединяющая все l каналов, содержит:

3 - первый и второй умножители, выход каждого из которых подключен к соответствующему входу сумматора 4. Входы первого умножителя 3 подключены к выходам мультиплексоров i/1 ( i = 1, l ¯ ), а входы второго умножителя 3 подключены к выходам мультиплексоров i/2 ( i = 1, l ¯ ). Дополнительные входы первого и второго умножителей 3 являются внешними входами устройства;

4 - сумматор, первый и второй входы которого подключены соответственно к выходам первого и второго умножителей 3, а выход соединен с информационными входами первого и второго ключей 5;

5 - первый и второй ключи, информационные входы которых соединены с выходом сумматора 4, выход первого ключа 5 через первую ячейку памяти 6 подключен к первому входу (входу делимого) делителя 7, а выход второго ключа 5 через вторую ячейку памяти 6 подключен ко второму входу (входу делителя) делителя 7. Управляющий вход первого ключа 5 подключен ко входу инвертора 9 и ко вторым адресующим входам всех мультиплексоров 2, а управляющий вход второго ключа 5 - к выходу инвертора 9;

6 - первая и вторая ячейки памяти, входы которых подключены соответственно к выходам первого и второго ключей 5, а выходы соединены соответственно с первым и вторым входами делителя 7. На объединенные считывающие входы первой и второй ячеек памяти 6 поступает внешний сигнал считывания;

7 - делитель, первый вход (вход делимого) которого соединен с выходом первой ячейки памяти 6, второй вход (вход делителя) - с выходом второй ячейки памяти 6, а выход подключен ко входу порогового устройства 8;

8 - пороговое устройство, вход которого подключен к выходу делителя 7, второй вход является внешним входом сигнала порогового уровня, а выход является выходом устройства;

9 - инвертор, вход которого подключен к управляющему входу первого ключа 5 и ко вторым адресующим входам всех мультиплексоров 2, а выход - к управляющему входу второго ключа 5.

Устройство работает следующим образом (рассмотрим работу одного i-го канала устройства, поскольку каналы идентичны).

Аналоговый входной сигнал yit поступает на вход i-го обнаружителя 1, с выхода которого частное решение δi в виде 1 (сигнал есть) или 0 (сигнала нет) поступает на первые адресующие входы мультиплексоров 2 (i/1 и i/2), на вторые адресующие входы которых поступает внешний сигнал 9 в виде 1 или 0. В первом цикле работы устройства подается внешний сигнал ϑ=1, при котором формируется функция правдоподобия F(ϑ=1), а во втором цикле - внешний сигнал ϑ=0, при котором формируется функция правдоподобия F(ϑ=0). Поступающие на информационные входы мультиплексоров 2 (i/1 и i/2) сигналы удобно представлять в виде матриц

Каждый из элементов матрицы (15) подается на свой информационный вход мультиплексора i/1, а матрицы (16) - на свой информационный вход мультиплексора i/2.

Дальнейший порядок работы предлагаемого устройства рассмотрим на простейшем примере двухканального обнаружителя. Исходные данные и результаты промежуточных расчетов сразу для двух циклов работы устройства приведены в таблице 1

В зависимости от комбинации сигналов ϑi, ϑ на адресующих входах на выход соответствующего мультиплексора 2 выдается одно из значений вероятностей, поступающих на информационные входы мультиплексора. Так, на информационные входы мультиплексора 1/1 первого канала поступают значения вероятностей, представленные матрицей (15), а на информационные входы мультиплексора 1/2 первого канала поступают значения вероятностей, представленные матрицей (16). В рассмотренном в таблице 1 примере в первом цикле работы устройства (ϑ=1) при δ1=0, ϑ=1 на выход мультиплексора 1/1 выдается значение 1-D1=0,50, а на выход мультиплексора 1/2 значение . Указанные значения поступают на первый вход первого и второго умножителей 3 соответственно. Аналогично рассмотренному выше, при δ2=1,ϑ=1 на выход мультиплексора 2/1 второго канала выдается значение D2=0,90, а на выход мультиплексора 2/2 второго канала значение . Указанные значения поступают на второй вход первого и второго умножителей 3 соответственно. На дополнительный вход первого умножителя 3 поступает значение вероятности Р(Jam=da), а на дополнительный вход второго умножителя 3 - значение вероятности 1-P(Jam=da). В рассматриваемом примере эти значения составляют 0,70 и 0,30 соответственно. В результате перемножения на выходе первого умножителя 3 формируется значение 0,50·0,90·0,70=0,3150, а на выходе второго умножителя 3 - значение 0,20·0,95·0,30=0,0570. Указанные значения поступают на первый и второй входы сумматора 4, выходной сигнал которого F(ϑ=1)=0,3150+0,0570=0,3720 поступает на информационные входы первого и второго ключей 5. Аналогично рассмотренному, во втором цикле работы устройства (ϑ=0) на выходе сумматора 4 будет сформирован выходной сигнал F(ϑ=0)=0,0175+0,0027=0,0202. При поступлении входного сигнала ϑ=1 на управляющий вход первого ключа 5 он открывается и выходной сигнал сумматора 4 F(ϑ=1)=0,3720 записывается в первую ячейку памяти 6. При поступлении входного сигнала ϑ=0 через инвертор 9 на управляющий вход второго ключа 5 он открывается и сигнал F(ϑ=0)=0,0202 с выхода сумматора 4 записывается во вторую ячейку памяти 6. По внешнему сигналу считывания, поступающему на считывающие входы первой и второй ячеек памяти 6, значения F(ϑ=1)=0,3720 и F(ϑ=0)=0,0202 с выходов ячеек памяти 6 поступают соответственно на первый (вход делимого) и второй (вход делителя) входы делителя 7. Сформированное в делителе 7 отношение правдоподобия λ = F ( ϑ = 1 ) F ( ϑ = 0 ) = 0,3720 0,0202 = 18,416 поступает на вход порогового устройства 8, в котором оно сравнивается со значением порога h, поступающим на его пороговый вход в качестве внешнего сигнала. В зависимости от результата сравнения на выходе порогового устройства 8 формируется окончательное решение о наличии сигнала (порог превышен →ϑ=1) или об его отсутствии (порог не превышен →ϑ=0).

В рассматриваемом примере при h=17 предлагаемым устройством будет принято решение ϑ=1 о наличии сигнала.

В прототипе при тех же исходных данных отношение правдоподобия (11) составит

и будет принято противоположное решение ϑ=0 об отсутствии сигнала.

Таким образом, отсутствие учета статистической зависимости частных решений обнаружителей в прототипе может привести к принятию им неверного общего решения в условиях неопределенной помеховой обстановки.

Сравнительная оценка отношений правдоподобия показывает, что в предлагаемом устройстве оно на 15,66% выше, чем в прототипе. Поскольку отношение правдоподобия является мерой апостериорного отличия гипотез о наличии и отсутствии сигнала, то чем оно больше, тем более достоверно решение в пользу соответствующей гипотезы.

Комплексное устройство обнаружения, являющееся многоканальным, содержащее в каждом канале обнаружитель, а в общей части пороговое устройство, второй вход которого является внешним входом сигнала порогового уровня, а выход является выходом устройства, отличающееся тем, что в общую часть устройства дополнительно введены первый и второй умножители, сумматор на два входа, первый и второй ключи, первая и вторая ячейки памяти, инвертор и делитель, а в каждый канал дополнительно введены два мультиплексора, первые адресующие входы которых подключены к выходу соответствующего обнаружителя, а вторые адресующие входы всех мультиплексоров объединены в один вход внешнего сигнала; информационные входы каждого из мультиплексоров являются внешними входами, выходы первых мультиплексоров каждого канала подключены к соответствующим входам первого умножителя, а выходы вторых мультиплексоров каждого канала - к соответствующим входам второго умножителя, дополнительный вход каждого из которых является входом соответствующего внешнего сигнала, а выход подключен к соответствующему входу сумматора, выход которого подключен к информационным входам первого и второго ключей, управляющий вход первого из которых непосредственно, а второго через инвертор подключен ко вторым адресующим входам всех мультиплексоров, причем выход первого ключа через первую ячейку памяти подключен к первому входу делителя, а выход второго ключа через вторую ячейку памяти подключен ко второму входу делителя, выход которого соединен со входом порогового устройства, а входы считывания первой и второй ячеек памяти объединены и являются внешним входом устройства обнаружения.