Устройство драйвера и способ возбуждения для возбуждения нагрузки, в частности, блока сид

Иллюстрации

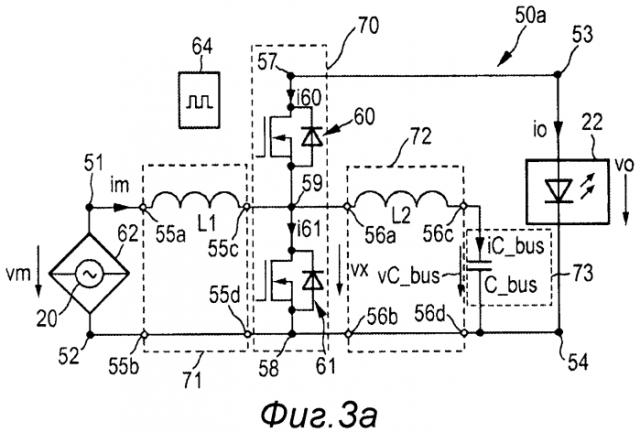

Показать всеИзобретение относится к устройству (50a-50j) драйвера и соответствующему способу возбуждения для возбуждения нагрузки (22), в частности, блока LED. Техническим результатом является предоставление драйвера с высоким коэффициентом полезного действия, который может применяться для широких диапазонов напряжений питания и возбуждения нагрузки, в частности, блока СИД. Результат достигается тем, что устройство драйвера содержит клеммы (51, 52) ввода мощности для приема выпрямленного напряжения питания из внешнего источника питания, клеммы (53, 54) вывода мощности для выдачи напряжения и/или тока возбуждения для возбуждения нагрузки (22), полумостовой блок (70), содержащий первый (60) и второй (61) коммутационные элементы, присоединенный последовательно между узлом (57) высокого напряжения и узлом (58) низкого напряжения и имеющий узел (59) коммутации между упомянутым первым и вторым коммутационными элементами, блок (71) повышающего входного фильтра, содержащий первую катушку (L1) индуктивности, присоединенную между упомянутыми клеммами (51, 52) ввода мощности и упомянутым полумостовым блоком (70), блок (72) подпорного выходного фильтра, содержащий вторую катушку (L2) индуктивности, присоединенную между упомянутым полумостовым блоком (70) и клеммой (53, 54) вывода мощности, блок (73) накопления энергии и блок (64) управления для управления упомянутыми коммутационными элементами (60, 61). 2 н. и 12 з.п. ф-лы, 28 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

Настоящее изобретение относится к устройству драйвера и соответствующему способу возбуждения для возбуждения нагрузки, в частности, блока СИД (светоизлучающих диодов, LED), содержащего один или более СИД. Кроме того, настоящее изобретение относится к устройству освещения.

УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

В области техники драйверов СИД для автономных применений, таких как модернизированные лампы, требуются решения, чтобы справляться с требованиями, относящимися к высокой эффективности, высокой плотности мощности, длинному сроку службы, высокому коэффициенту мощности и низкой стоимости, среди других значимых признаков. Несмотря на то, что на практике все существующие решения компрометируют одно или другое требование, существенно, что предложенные схемы драйвера надлежащим образом приводят в определенное состояние форму потребляемой от сети мощности в форму, требуемую СИД, наряду с сохранением совместимости с настоящими и будущими предписаниями силовых питающих сетей. Критически важно гарантировать максимальное значение в отношении воспринимаемого мерцания света (предпочтительно нулевое) одновременно с тем, что коэффициент мощности поддерживается выше определенного предела.

Типично, два последовательно соединенных силовых каскада применяются для получения высокого коэффициента мощности наряду с сохранением выходной мощности постоянной на всем протяжении цикла питающей сети (или цикла питания, то есть цикла напряжения сети или напряжения питания). К тому же, известны преобразователи с одиночным каскадом преобразования мощности, который предоставляет возможность высоких коэффициентов мощности (HPF) посредством встраивания повышающего преобразователя, работающего в режиме прерываемой проводимости. Такие преобразователи фактически объединяют два каскада преобразования мощности.

Преобразователь HPF (с высоким коэффициентом мощности) для малогабаритных люминесцентных ламп описан в «High-Power-Factor Electronic Ballast with Constant DC-Link Voltage», by Ricardo de Oliveira Brioschi and Jose Luiz F. Vieira, IEEE Transactions on Power Electronics, vol. 13, no. 6, 1998 («Электронный дроссель стартера с большим коэффициентом мощности и постоянным напряжением звена постоянного тока», Рикардо Де-Оливейра Бриоши и Жозе Луиз Ф. Виера, Труды по силовой электронике IEEE, том. 13, № 6, 1998). Здесь полумостовой блок совместно используется повышающим преобразователем и параллельным резонансным преобразователем LC, который эксплуатируется выше резонанса, для того, чтобы получать переключение при нулевом напряжении (ZVS). Чтобы дополнительно поддерживать ZVS, напряжение на шине регулируется, чтобы быть постоянным. Такой преобразователь с HPF типично требует большого конденсатора на шине и выходного выпрямителя и имеет всего лишь узкие диапазоны напряжения питания и напряжения (возбуждения) нагрузки.

US2006/103363 раскрывает схему стабилизатора мощности с преобразованием постоянного тока. Схема имеет входные клеммы для приема входного напряжения постоянного тока и имеет порт вывода для выдачи стабилизированного выходного напряжения постоянного тока. Схема содержит повышающий входной фильтр и подпорный выходной фильтр, содержащие соответственно первое и второе средства катушки индуктивности. Между обоими фильтрами предусмотрен полумост. Схема дополнительно включает в себя блок накопления энергии и блок управления. Эта схема пригодна только для применения в пределах узких диапазонов напряжений питания и возбуждения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Цель настоящего изобретения состоит в том, чтобы предоставить устройство драйвера и соответствующий способ возбуждения для возбуждения нагрузки, в частности, блока СИД, содержащего один или более СИД, дающие возможность достигаться особенно высокому коэффициенту мощности, практически постоянной нагрузке, малому размеру, высокому коэффициенту полезного действия, продолжительному сроку службы и низким затратам. Более того, изобретение имеет намерением предоставить драйвер, который может применяться для широких диапазонов напряжений питания и возбуждения. Кроме того, цель настоящего изобретения состоит в том, чтобы предоставить соответствующее устройство освещения.

Согласно аспекту настоящего изобретения, предложено устройство драйвера, содержащее:

- клеммы ввода мощности для приема выпрямленного напряжения питания из внешнего источника питания,

- клеммы вывода мощности для выдачи напряжения и/или тока возбуждения для возбуждения нагрузки,

- полумостовой блок, содержащий первый и второй коммутационные элементы, присоединенный последовательно между узлом высокого напряжения и узлом низкого напряжения и имеющий узел коммутации между упомянутым первым и упомянутым вторым коммутационными элементами,

- блок повышающего входного фильтра, содержащий первую катушку индуктивности, присоединенную между упомянутыми клеммами ввода мощности и упомянутым полумостовым блоком,

- блок подпорного выходного фильтра, содержащий вторую катушку индуктивности, присоединенный между упомянутым полумостовым блоком и клеммой вывода мощности,

- блок управления для управления упомянутыми коммутационными элементами.

Согласно еще одному аспекту настоящего изобретения, предложен соответствующий способ возбуждения.

Согласно еще одному другому аспекту настоящего изобретения, предусмотрено устройство освещения, содержащее осветительную сборку, имеющую один или более световых блоков, в частности, блок СИД, содержащий один или более СИД, и устройство драйвера для возбуждения упомянутой осветительной сборки, как предусмотренное согласно настоящему изобретению.

Предпочтительные варианты осуществления изобретения определены в зависимых пунктах формулы изобретения. Будет понятно, что заявленный способ имеет подобные и/или идентичные предпочтительные варианты осуществления, как у заявленного устройства и как определенные в зависимых пунктах формулы изобретения.

Настоящее изобретение основано на идее встроить автономный синхронный повышающий преобразователь в синхронный подпорный преобразователь. Нагрузка (например, блок СИД HV) присоединена к клеммам вывода мощности. Кроме того, конденсатор (высокочастотного, HF) ВЧ-фильтра (то есть сетевого фильтра) предпочтительно присоединен к клеммам ввода мощности. Таким образом, настоящее изобретение обеспечивает как постоянный ток возбуждения, так и коэффициенты мощности 0,9 или выше.

Уровень напряжения отдельного конденсатора (то есть уровень напряжения на блоке накопления мощности, который предпочтительно является конденсатором; в дальнейшем также называемого «конденсатором на шине») предоставляет возможность минимизации накопленной энергии. Подпорный ток предусматривает коммутацию без потерь обоих коммутационных элементов (предпочтительно транзисторов, например MOSFETS (полевых транзисторов с изолированным затвором), упомянутые коммутационные элементы формируют полумостовой блок), что означает высокий коэффициент полезного действия даже на высоких частотах, который предоставляет возможность миниатюрных катушек индуктивности.

По сравнению с известным преобразователем HPF, можно обходиться без большого конденсатора на шине, предоставляя напряжению на шине (то есть напряжению на блоке накопления энергии) возможность меняться в течение цикла питания или цикла напряжения сети (например, на от 20 до 80%) наряду с поддержанием выходного тока (возбуждения) постоянным. Кроме того, не включен в состав выходной выпрямитель, так как каскад LC заменен каскадом преобразователя со ступенчатым понижением (то есть подпорным преобразователем). Кроме того, дополнительно, узкие диапазоны напряжений питания и возбуждения могут преодолеваться изменением схемы и специальным управлением полумостом. Это дает возможность спроектировать изобретение для питающей сети США или для европейской питающей сети, по-прежнему наряду с поддержанием нагрузки напряжением полумостового блока и элемента накопления энергии (например, накопительного конденсатора) в рамках типичных пределов.

Согласно настоящему изобретению, есть различные базовые конфигурации синхронного подпорного преобразователя с встроенной вольтодобавкой (BSB), которые предусмотрены в качестве разных предпочтительных вариантов осуществления, которые могут выдерживать различные диапазоны нагрузок и входных напряжений. Все из них могут управляться на полном диапазоне нагрузок вплоть до практически нулевого тока нагрузки посредством манипулирования только относительной длительностью включения или частотой переключения, либо приведения в действие пакетного режима.

Напряжение питания может быть выпрямленным периодическим напряжением питания, выдаваемым источником питания. В случае, в котором напряжение сети переменного тока (AC) предусмотрено в качестве входного напряжения в источник питания (или на клеммы ввода мощности), например из подвода напряжения сети, блок выпрямителя предпочтительно используется (в качестве части устройства драйвера или в качестве внешнего блока, присоединенного к клеммам ввода мощности) для выпрямления предоставленного входного напряжения переменного тока, например напряжения сети, в (выпрямленное периодическое) напряжение питания. Такой блок выпрямителя, например, может содержать общеизвестный полумостовой или полномостовой выпрямитель. Напряжение питания, таким образом, имеет одинаковую полярность для любой полярности входного напряжения переменного тока.

В качестве альтернативы, например, если выпрямленное периодическое напряжение питания уже предусмотрено на клеммах ввода мощности, например, из выпрямителя (представляющего упомянутый внешний источник питания), предусмотренного в другом месте, никакие дополнительные или только обычные элементы (например, подобные усилителю) не присоединены к клеммам ввода мощности для придания формы выдаваемому напряжению питания.

Есть различные варианты осуществления предложенного устройства драйвера, которые главным образом отличаются способом, которым соединены различные элементы устройства драйвера.

Выходная сторона блока повышающего входного фильтра может быть присоединена к первому или второму коммутационному элементу полумостового блока. Предпочтительно, если выходные клеммы блока повышающего входного фильтра переключаются, то есть по-разному присоединяются к полумостовому блоку, входные клеммы подпорного выходного фильтра также переключаются, то есть по-разному присоединяются к полумостовому блоку, для того, чтобы обеспечивать самоустанавливающееся действие.

Согласно дополнительным вариантам осуществления, нагрузка (то есть клеммы вывода мощности) или блок накопления энергии, например конденсатор на шине, присоединены к выходным клеммам блока подпорного выходного фильтра или выходным клеммам блока повышающего входного фильтра. В еще одном варианте осуществления блок накопления энергии присоединен последовательно нагрузке.

Различные варианты осуществления предусмотрены для использования в разных применениях и на разных напряжениях и направлены на достижение определенных целей. Часто, должен устанавливаться компромисс для выбора оптимального варианта осуществления.

Предпочтительно, коммутационные элементы вместе формируют полумостовой блок (также называемый коммутационным блоком или иногда называемый полумостом). Но, обычно, коммутационные элементы могут быть реализованы различными способами, в том числе, например, транзисторами (например, MOSFET) или другим управляемым средством переключения.

Преимущественно, блок накопления энергии содержит зарядный конденсатор, предпочтительно, одиночный конденсатор.

В варианте осуществления вторая клемма ввода мощности и вторая клемма вывода мощности присоединены к опорному потенциалу, в частности, потенциалу земли. В других вариантах осуществления первая клемма ввода мощности и первая клемма вывода мощности соединены напрямую наряду с тем, что вторая клемма ввода мощности и второй вывод мощности не соединены напрямую.

Предпочтительно, блок управления приспособлен для поддержания выходного тока постоянным для того, чтобы поддерживать напряжение на элементе накопления энергии ниже предопределенного порогового значения и/или чтобы придавать форму входному току. Переключение при нулевом напряжении коммутационных элементов предусмотрено конструкцией (компонентами) предложенного устройства драйвера. Задачи управления состоят в том, чтобы удерживать выходной ток постоянным, возможно согласно опорному току (уставке), чтобы поддерживать напряжение на шине (то есть напряжение на элементе накопления энергии) ниже заранее заданного предела и/или чтобы придавать форму входному току.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Эти и другие аспекты изобретения будут очевидны из и разъяснены со ссылкой на вариант(ы) осуществления, описанный в дальнейшем.

На последующих чертежах:

фиг.1 показывает принципиальную структурную схему известного двухкаскадного устройства драйвера,

фиг.2a показывает принципиальную структурную схему известного однокаскадного устройства драйвера с входным накопительным конденсатором,

фиг.2b показывает принципиальную структурную схему известного однокаскадного устройства драйвера с выходным накопительным конденсатором,

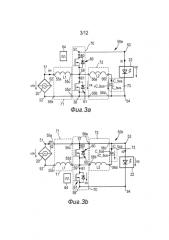

фиг.3 показывает принципиальные структурные схемы двух вариантов осуществления первой конфигурации устройства драйвера согласно настоящему изобретению,

фиг.4 показывает принципиальные структурные схемы четырех вариантов осуществления второй конфигурации устройства драйвера согласно настоящему изобретению,

фиг.5 показывает принципиальные структурные схемы двух вариантов осуществления третьей конфигурации устройства драйвера согласно настоящему изобретению,

фиг.6 показывает эпюры напряжений и токов во время одного низкочастотного цикла в варианте осуществления первой конфигурации предложенного устройства драйвера,

фиг.7 показывает эпюры различных токов во время одного высокочастотного цикла в варианте осуществления первой конфигурации предложенного устройства драйвера,

фиг.8 показывает эпюры напряжений и токов во время одного низкочастотного цикла в варианте осуществления второй конфигурации предложенного устройства драйвера,

фиг.9 показывает эпюры различных токов во время одного высокочастотного цикла в варианте осуществления второй конфигурации предложенного устройства драйвера,

фиг.10 показывает эпюры напряжений и токов во время одного низкочастотного цикла в варианте осуществления третьей конфигурации предложенного устройства драйвера,

фиг.11 показывает эпюры различных токов во время одного высокочастотного цикла в варианте осуществления третьей конфигурации предложенного устройства драйвера,

фиг.12 показывает четыре варианта блока повышающего входного фильтра для использования в устройстве драйвера согласно настоящему изобретению,

фиг.13 показывает два варианта блока подпорного выходного фильтра для использования в устройстве драйвера согласно настоящему изобретению,

фиг.14 показывает два примерных варианта осуществления нагрузки, которая может возбуждаться устройством драйвера согласно настоящему изобретению,

фиг.15 показывает первый вариант осуществления блока управления предложенного устройства драйвера,

фиг.16 показывает сигнал переключения первого коммутационного элемента в полумостовом блоке, и

фиг.17 показывает второй вариант осуществления блока управления предложенного устройства драйвера.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Вариант осуществления известного двухкаскадного устройства 10 драйвера схематически показан на фиг.1. Упомянутое устройство 10 драйвера содержит блок 12 выпрямителя, блок 14 предварительной обработки первого каскада, присоединенный к выходу блока 12 выпрямителя, блок 16 преобразования второго каскада, присоединенный к выходу блока 14 предварительной обработки первого каскада, и зарядный конденсатор 18, присоединенный к узлу 15 между упомянутым блоком 14 предварительной обработки первого каскада и упомянутым блоком 16 преобразования второго каскада. Блок 12 выпрямителя предпочтительно содержит выпрямитель, такой как известный полноволновый или полуволновый мостовой выпрямитель, для выпрямления поставляемого входного напряжения V20 переменного тока, например, из внешнего источника 20 напряжения сети в выпрямленное напряжение V12. Нагрузка 22, в этом варианте осуществления, блок СИД, содержит два СИД 23, присоединенных к выходу блока 16 преобразования второго каскада, чей выходной сигнал, в частности, его напряжение V16 возбуждения и его ток I16 возбуждения, используется для возбуждения нагрузки 22.

Блок 14 предварительной обработки первого каскада предварительно обрабатывает выпрямленное напряжение V12 в промежуточное напряжение V14 постоянного тока, а блок 16 преобразования второго каскада преобразует упомянутое промежуточное напряжение V14 постоянного тока в требуемое напряжение V16 возбуждения постоянного тока. Зарядный конденсатор 18 предусмотрен для накопления заряда, то есть он заряжается от промежуточного напряжения V14 постоянного тока, тем самым отфильтровывая низкочастотный сигнал из выпрямленного напряжения V12, чтобы обеспечивать по существу постоянную выходную мощность второго блока 16 преобразования второго каскада, в частности постоянный ток I16 возбуждения через нагрузку 22. Так как эти элементы 14, 16, 18 общеизвестны и широко используются в таких устройствах 10 драйвера, здесь они подробнее описаны не будут.

Вообще, устройство 10 драйвера удовлетворяет вышеупомянутую потребность в высоком коэффициенте мощности и низких пульсациях за счет больших пространственных требований и более высоких затрат, которые, однако, могут быть радикально ограничены особенно в модернизированных применениях. Размер блока 14 предварительной обработки первого каскада главным образом может определяться ассоциативно связанными пассивными компонентами, особенно если он содержит источник питания с переключаемым режимом (SMPS), например, повышающий преобразователь, работающий на низкой или средней частоте переключений. Любая попытка повысить частоту переключений с тем, чтобы уменьшить размер этих компонентов фильтра, может давать быстрый рост энергетических потерь в SMPS с жестким переключением, а отсюда - необходимость в больших радиаторах.

Варианты осуществления известных однокаскадных устройств 30a, 30b драйвера схематически показаны на фиг.2a и фиг.2b. Упомянутое устройство 30 драйвера содержит блок 32 выпрямителя (который может быть идентичным блоку 12 выпрямителя двухкаскадного устройства 10 драйвера, показанного на фиг.1) и блок 34 преобразования (например, преобразователь обратного хода для варианта осуществления, показанного на фиг.2b, или подпорный преобразователь для варианта осуществления, показанного на фиг.2a), присоединенный к выходу блока 32 выпрямителя. Кроме того, в варианте осуществления, показанном на фиг.2a, зарядный конденсатор 36a (представляющий собой низкочастотный входной накопительный конденсатор) присоединен к узлу 33 между упомянутым блоком 32 выпрямителя и упомянутым блоком 34 преобразования. В варианте осуществления, показанном на фиг.2b, зарядный конденсатор 36b (представляющий собой низкочастотный выходной накопительный конденсатор) присоединен к узлу 35 между упомянутым блоком 34 преобразования и нагрузкой 22. Блок выпрямителя выпрямляет входное напряжение V20 переменного тока, например, из внешнего источника 20 напряжения сети (также называемого источником питания) в выпрямленное напряжение V32. Выпрямленное напряжение V32 преобразуется в требуемое напряжение V34 возбуждения постоянного тока для возбуждения нагрузки 22.

Накопительные конденсаторы 18 (на фиг.1) и 36a, 36b (на фиг.2a, 2b) главным образом предусмотрены для отфильтровывания низкочастотной составляющей выпрямленного напряжения V12 для того, чтобы предоставлять возможность для постоянного тока в нагрузку. Такие конденсаторы поэтому являются большими, особенно, когда поставлены параллельно с нагрузкой и когда такой нагрузкой является СИД.

Устройства драйвера, как показанные на фиг.1 и 2, например, описаны в Robert Erickson and Michael Madigan, «Design of a simple high-power-factor rectifier based on the flyback converter», IEEE Proceedings of the Applied Power Electronics Conferences and Expositions, 1990, pp. 792-801 (Роберт Эриксон и Майкл Мадиган, «Конструкция простого выпрямителя с высоким коэффициентом мощности, основанная на преобразователе обратного хода», Протоколы IEEE конференций и выставок по прикладной силовой электронике, 1990, стр. 792-801).

Большинство таких однокаскадных устройств 30a, b драйвера, хотя и содержащих отличительный признак более низкого количества аппаратных компонентов по сравнению с двухкаскадными устройствами драйвера, как иллюстративно показано на фиг.1, обычно не могут предложить высокий коэффициент мощности вследствие ограничений по размеру зарядного конденсатора, который должен отфильтровывать низкочастотную составляющую входного напряжения переменного тока. В дополнение, однокаскадные устройства драйвера могут критически компрометировать размер, срок службы и максимальную температуру работы нагрузки (например, лампы) вследствие использования больших накопительных конденсаторов для уменьшения заметной пульсации.

Фиг.3-5 изображают некоторые варианты осуществления трех разных базовых конфигураций устройства драйвера согласно настоящему изобретению. Эти три конфигурации (варианты осуществления конфигурации 1, показываемой на фиг.3, варианты осуществления конфигурации 2, показываемые на фиг.4, варианты осуществления конфигурации 3, показываемые на фиг.5) отличаются в действии в показателях диапазонов входного и выходного напряжений, которые они поддерживают, а также в показателях нагрузки компонентов при пиковых напряжениях и токах RMS. Все три конфигурации показывают самоустанавливающееся поведение, которое предоставляет возможность регулирования выходного тока с тем, чтобы был постоянным при предопределенных пульсациях напряжения на шине (то есть напряжения vbus), как будет пояснено ниже. Повышающая катушка индуктивности (то есть первая катушка L1 индуктивности блока 71 повышающего входного фильтра) предназначена для работы в режиме прерываемой проводимости. Кроме того, ZVS возможно для обоих переходов коммутационных элементов (то есть коммутационных элементов 60, 61, формирующих полумостовой блок), которые определяются подпорной катушкой индуктивности (то есть второй катушкой L2 индуктивности блока 72 подпорного выходного фильтра).

В вариантах осуществления типа 1 (то есть вариантах осуществления, показанных на фиг.3a, 4a, 5a) и типа 2 (то есть вариантах осуществления, показанных на фиг.3b, 4b, 4c, 4d, 5b) все соединения переключаются относительно верхнего и нижнего коммутационных элементов 60, 61.

Диаграммы, показанные на фиг.6-11, ссылаются на три конфигурации, показанные на фиг.3, 4 и 5. Все они показывают коэффициент мощности около 0,95 и нагрузку 10 Вт. В варианте осуществления, в котором нагрузка 22 является цепочкой СИД, содержащей два или более СИД, выходной ток io (возбуждения) состоит из составляющей iLED постоянного тока через цепочку СИД плюс тока ВЧ, протекающего через параллельный конденсатор ВЧ (здесь не показан; указанный в качестве C_HF на фиг.14b). В примерах ток СИД поддерживается постоянным посредством манипулирования относительной длительностью включения.

Первый вариант осуществления устройства 50a драйвера согласно настоящему изобретению схематически показан на фиг.3a. Он содержит клеммы 51, 52 ввода мощности для приема выпрямленного напряжения vm питания из внешнего источника 20 питания (например, источника напряжения сети), которое предпочтительно выпрямляется выпрямителем 62. Устройство 50a драйвера дополнительно содержит клеммы 53, 54 вывода мощности для выдачи напряжения vo возбуждения и/или тока io напряжения для возбуждения нагрузки 22.

Полумостовой блок 70 (также называемый коммутационным блоком или полумостом), содержащий первый 60 и второй 61 коммутационные элементы, присоединен последовательно между узлом 57 высокого напряжения и узлом 58 низкого напряжения и формирует узел 59 коммутации между упомянутым первым и упомянутым вторым коммутационными элементами 60, 61. Блок 71 повышающего входного фильтра, содержащий первую катушку L1 индуктивности, присоединен между упомянутыми клеммами 51, 52 ввода мощности и упомянутым полумостовым блоком 70. Блок 72 подпорного выходного фильтра, содержащий вторую катушку L2 индуктивности, присоединен между упомянутым полумостовым блоком 70 и клеммой 53, 54 вывода мощности.

Входные клеммы 55a, 55b блока 71 повышающего входного фильтра присоединены к клеммам 51, 52 ввода мощности. Выходные клеммы 55c, 55d блока 71 повышающего входного фильтра присоединены к узлу 59 коммутации и узлу 58 низкого напряжения полумостового блока 70. Входные клеммы 56a, 56b упомянутого блока 72 подпорного выходного фильтра присоединены к узлу 58 низкого напряжения и узлу 59 коммутации полумостового блока 70. Выходные клеммы 56c, 56d блока 72 подпорного выходного фильтра присоединены к блоку 73 накопления энергии, который предпочтительно является одиночным конденсатором C_bus на шине.

Клеммы 53, 54 вывода мощности, между которыми присоединена нагрузка 22, присоединены непосредственно к узлу 57 высокого напряжения и узлу 58 низкого напряжения полумостового блока 70.

В заключение, блок 64 управления (например, реализованный в качестве контроллера, процессора или компьютера, который надлежащим образом сконструирован или запрограммирован) предусмотрен для управления упомянутыми коммутационными элементами 60, 61.

Второй вариант осуществления устройства 50b драйвера согласно настоящему изобретению схематически показан на фиг.3b. По сравнению с первым вариантом осуществления устройства 50a драйвера, выходные клеммы 55c, 55d блока 71 повышающего входного фильтра присоединены к узлу 57 высокого напряжения и узлу 59 коммутации полумостового блока 70. Кроме того, входные клеммы 56a, 56b упомянутого блока 72 подпорного выходного фильтра присоединены к узлу 57 коммутации и узлу 57 высокого напряжения полумостового блока 70.

Фиг.12 показывает четыре варианта осуществления блока 71 повышающего входного фильтра. В первом и втором вариантах 71a, 71b осуществления предусмотрена одиночная первая катушка L1 индуктивности в соединении от первой входной клеммы 55a к первой выходной клемме 55c либо в соединении между второй входной клеммой 55b и второй выходной клеммой 55d. В третьем и четвертом вариантах 71c, 71d осуществления диод D1 присоединен последовательно с первой катушкой L1 индуктивности.

Фиг.13 показывает два варианта осуществления блока 72 подпорного выходного фильтра. В первом варианте 72a осуществления вторая катушка L1 индуктивности предусмотрена в соединении от первой входной клеммы 56a до первой выходной клеммы 56c наряду с тем, что во втором варианте 72b осуществления вторая катушка L2 индуктивности предусмотрена в соединении между второй входной клеммой 56b и второй выходной клеммой 56d.

Различные варианты осуществления блока 71 повышающего входного фильтра, показанного на фиг.12, и различные варианты осуществления блока 72 подпорного выходного фильтра, показанного на фиг.13, могут быть присоединены к различным вариантам осуществления блока драйвера, как показано на фиг.3 (а также к вариантам осуществления, показанным на фиг.4 и 5), вместо соответственных вариантов осуществления блока 71 повышающего входного фильтра у блока 72 подпорного выходного фильтра, показанных на таких фигурах.

Два варианта осуществления нагрузки, которая может быть присоединена к устройству драйвера согласно настоящему изобретению, показаны на фиг.14. Фиг.14a показывает одиночный СИД 23 в качестве нагрузки 22a наряду с тем, что фиг.14b показывает нагрузку 22b, сформированную последовательным соединением нескольких СИД 23, присоединенную параллельно конденсатору ВЧ, C_HF. В нагрузке 22b ток нагрузки io разделяется на ток конденсатора iC_HF и ток СИД iLED.

Диод D1 используется, если конденсатор входного фильтра ВЧ (то есть сетевой фильтр) присоединен на клеммах 55a, 55b повышающего входного фильтра, то есть между клеммами 51, 52 ввода мощности. Диод D1 не включен в состав, если конденсатор фильтра ВЧ присоединен на входе переменного тока выпрямителя 20 и если в нем используются достаточно быстрые выпрямители. За исключением вышеприведенного ограничения (то есть опущен D1), конденсатор ВЧ может быть присоединен к каждой из трех клемм, а именно клеммам 51, 52 ввода мощности, выходным клеммам 55c, 55d повышающего входного фильтра и выходным клеммам 56c, 56d подпорного выходного фильтра.

Согласно первому и второму вариантам осуществления, повышающий преобразователь, по существу сформированный первой катушкой L1 индуктивности и двумя коммутационными элементами 60, 61, питает нагрузку 22. Ток iLED повышающего преобразователя (который соответствует выходному току io в случае нагрузки, как показанная на фиг.14a) может поддерживаться постоянным на всем протяжении цикла питающей сети, так как часть входного тока im сети подается в конденсатор C_bus на шине, который присоединен к концу подпорного преобразователя, сформированного по существу коммутационными элементами 60, 61 и второй катушкой L2 индуктивности, работающего в качестве двунаправленного преобразователя, который питает нагрузку 22 на низких входных напряжениях сети.

Фиг.6 и 7 показывают эпюры сигналов применения 120 В, 60 Гц (то есть vm(rms)=120 В, fm=60 Гц) по первому варианту осуществления с напряжением цепочки СИД vo=250 В при 40 мА (iLED) для варианта осуществления устройства 50a драйвера, как показанное на фиг.3a, в течение одного цикла питающей сети. Сигнал iC_bus, здесь, предельный ток НЧ iC_bus, шины на фиг.6 иллюстрирует двунаправленную работу подпорного преобразователя в течение цикла питающей сети (фиг.6) и каким образом подпорный преобразователь поддерживает ZVS при выключении полумоста (фиг.3), здесь, ток катушки индуктивности ВЧ (= предельному току шины) iC_bus на фиг.7, то есть если коммутационный элемент 60 выключен, а коммутационный элемент 61 включен (как указано сигналами i60, i61). Что касается примера форм сигналов, показанных на фиг.6 и 7, применяются следующие дополнительные значения: P=10 Вт, PF=0,95, vbus(max)=185 В, C_bus=4,7 мкФ. Относительная длительность включения указана посредством d.

Третий вариант осуществления устройства 50c драйвера согласно настоящему изобретению схематически показан на фиг.4a. Этот вариант осуществления по существу идентичен варианту осуществления устройства 50a драйвера, за исключением того, что, в этом варианте осуществления, выходные клеммы 55c, 55d блока 71 повышающего входного фильтра присоединены к узлу 58 низкого напряжения и узлу 59 коммутации полумостового блока 70. Входные клеммы 56a, 56b упомянутого блока 72 подпорного выходного фильтра присоединены к узлу 59 коммутации и узлу 57 высокого напряжения полумостового блока 70. Блок 73 накопления энергии присоединен между узлом 57 высокого напряжения и узлом 58 низкого напряжения полумостового блока 70. Кроме того, клеммы 53, 54 вывода мощности и, таким образом, также нагрузка 22 непосредственно присоединены к выходным клеммам 56c, 56d упомянутого блока 72 подпорного выходного фильтра.

Четвертый вариант осуществления устройства 50d драйвера согласно настоящему изобретению схематически показан на фиг.4b. По сравнению с третьим вариантом осуществления устройства 50c драйвера, в этом варианте осуществления, как в варианте осуществления устройства 50b драйвера, выходные клеммы 55c, 55d блока 71 повышающего входного фильтра присоединены к узлу 57 высокого напряжения и узлу 59 коммутации полумостового блока 70. Кроме того, входные клеммы 56a, 56b упомянутого блока 72 подпорного выходного фильтра присоединены к узлу 57 коммутации и узлу 58 низкого напряжения полумостового блока 70.

Фиг.4c и 4d показывают пятый и шестой вариант осуществления устройства 50e, 50f драйвера. Вариант осуществления, показанный на фиг.4c, идентичен варианту осуществления, показанному на фиг.4b, но дополнительный диод D1 предусмотрен последовательно первой катушке L1 индуктивности. В варианте осуществления, показанном на фиг.4c, диод D1 и первая катушка L1 индуктивности предусмотрены в соединении между первой входной клеммой 55a и первой выходной клеммой 55c.

Согласно с третьего по шестой вариантам осуществления, повышающий преобразователь питает конденсатор C_bus на шине. Подпорный преобразователь питает нагрузку 22. Что касается самоустанавливающегося действия, подпорный преобразователь перевернут относительно повышающего преобразователя. Вновь, ток iLED нагрузки может поддерживаться постоянным на всем протяжении цикла питающей сети, так как часть входного тока im сети подается в конденсатор C_bus на шине, который питает нагрузку 22 на низких входных напряжениях сети.

Фиг.8 и 9 показывают эпюры сигналов в применении 230 В, 50 Гц (то есть vm(rms)=230 В, fm=50 Гц) третьего варианта осуществления с напряжением цепочки СИД 100 В при 100 мА. Сигнал iC_bus иллюстрирует двунаправленную работу повышающего преобразователя во время цикла питающей сети (фиг.7) и вновь каким образом подпорный преобразователь поддерживает ZVS при выключении (сигнал io на фиг.8). Что касается примера форм сигналов, показанных на фиг.8 и 9, применяются следующие дополнительные значения: P=10 Вт, PF=0,95, vbus(max)=475 В, C_bus=1 мкФ. Эта конфигурация показывает самые низкие токи RMS.

Седьмой вариант осуществления устройства 50g драйвера согласно настоящему изобретению схематически показан на фиг.5a. Этот вариант осуществления по существу идентичен варианту осуществления устройства 50c драйвера, но, в этом варианте осуществления, блок 73 накопления энергии присоединен последовательно с нагрузкой 22, то есть между клеммой 54 вывода мощности и клеммой 58 низкого напряжения полумостового блока 70.

Восьмой вариант осуществления устройства 50h драйвера согласно настоящему изобретению схематически показан на фиг.5b. По сравнению с седьмым вариантом осуществления устройства 50g драйвера, в этом варианте осуществления нагрузка 22 и блок 70 накопления энергии обменены, то есть нагрузка 22 присоединена между клеммой 54 вывода мощности и клеммой 58 низкого напряжения полумостового блока 70, а блок 70 накопления энергии присоединен между клеммой 57 высокого напряжения полумостового блока 70 и клеммой 53 вывода мощности.

В конкретных реализациях седьмого и восьмого вариантов осуществления конденсатор C_bus на шине и цепочка 22 СИД расположены друг над другом. Для самоустанавливающегося действия цепочка 22 СИД присоединена к коммутационному элементу противоположно тому, к которому присоединен повышающий преобразователь. Вновь, ток iLED нагрузки может поддерживаться постоянным на всем протяжении цикла питающей сети, так как часть входной мощности сети подается в конденсатор на шине, который питает нагрузку на низких входных напряжениях сети.

Фиг.10 и 11 показывают эпюры сигналов в применении 230 В, 50 Гц (то есть vm(rms)=230 В, fm=50 Гц) седьмого варианта осуществления с напряжением цепочки СИД 100 В при 100 мА. Сигнал iC_bus иллюстрирует двунаправленную работу повышающего преобразователя во время цикла питающей сети (фиг.10) и вновь каким образом подпорный преобразователь 11 поддерживает ZVS при выключении полумоста (сигнал io на фиг.7). Что касается примера форм сигналов, показанных на фиг.10 и 11, применяются следующие дополнительные значения: vo=100 В, P=10 Вт, PF=0,94, vbus(max)=380 В, C_bus=1 мкФ.

Затем будут пояснены способ управления и устройство согласно настоящему изобретению. Фиг.15 показывает еще один вариант осуществления устройства 50i драйвера, включающий в себя первый вариант осуществления блока 64' управления (другие части устройства драйвера схематически проиллюстрированы одиночным блоком 50'). Ток iLED СИД (который является составляющей постоянного тока у выходного тока io; сравните с фиг.14b) измеряется и сравнивается с (заранее заданным или переменным) опорным током iLED_ref на элементе 64a сравнения. Ошибка err_i управления обрабатывается в блоке 64b контроллера (указанном посредством PI), давая в результате относительную длительность d включения в качестве переменной манипулирования. Вместе с заранее заданной частотой fs переключения сигналы возбуждения затвор