Биполярно-полевой операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиоэлектроники. Технический результат - повышение коэффициента усиления разомкнутого операционного усилителя. Биполярно-полевой операционный усилитель содержит входной дифференциальный каскад, общая истоковая цепь которого связана с первой шиной источника питания, первый и второй входы входного дифференциального каскада, первый токовый выход входного дифференциального каскада, связанный с эмиттером первого выходного транзистора и через первый токостабилизирующий двухполюсник соединенный со второй шиной источника питания, второй токовый выход входного дифференциального каскада, связанный с эмиттером второго выходного транзистора и через второй токостабилизирующий двухполюсник соединенный со второй шиной источника питания, источник опорного напряжения, связанный с базами первого и второго выходных транзисторов, токовое зеркало, согласованное с первой шиной источника питания, выход которого соединен с токовым выходом устройства. Коллекторы первого и второго выходных транзисторов соединены с первой шиной источника питания, первый токовый выход входного дифференциального каскада связан с эмиттером первого выходного транзистора через первый дополнительный резистор, второй токовый выход входного дифференциального каскада связан с эмиттером второго выходного транзистора через второй дополнительный резистор, причем источник опорного напряжения выполнен на основе дополнительного инвертирующего усилителя синфазного сигнала, выход которого через вспомогательный источник опорного тока связан с первой шиной источника питания, первый вход дополнительного инвертирующего усилителя синфазного сигнала соединен с первым токовым выходом входного дифференциального каскада и базой первого дополнительного транзистора, второй вход дополнительного инвертирующего усилителя синфазного сигнала соединен со вторым токовым выходом входного дифференциального каскада и базой второго дополнительного транзистора, коллектор первого дополнительного транзистора соединен со входом токового зеркала, коллектор второго дополнительного транзистора подключен к выходу токового зеркала и выходу устройства, а эмиттеры первого и второго дополнительных транзисторов связаны со второй шиной источника питания. 1 з.п. ф-лы, 11 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе архитектуры так называемого «перегнутого каскода» [1-12]. Их основное достоинство - эффективное использование напряжения питания.

Для работы в условиях космического пространства, в экспериментальной физике необходимы радиационно-стойкие ОУ с повышенным коэффициентом усиления по напряжению (70-80 дБ) и малым напряжением смещения нуля (Uсм). Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно на основе новой схемотехники и использования биполярно-полевого технологического процесса [13], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходимы специальные схемотехнические решения, учитывающие ограничения биполярно-полевой технологии [13].

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту фирмы National Semiconductor US 5.963.085. Он содержит (фиг. 1) входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с эмиттером первого 7 выходного транзистора и через первый 8 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с эмиттером второго 11 выходного транзистора и через второй 12 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, источник опорного напряжения 13 связанный с базами первого 7 и второго 11 выходных транзисторов, токовое зеркало 14, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 15.

Существенный недостаток известного ОУ состоит в том, что при типовом построении его основных функциональных узлов коэффициент усиления по напряжению (Ку) разомкнутого ОУ получается сравнительно небольшим. Это связано с фундаментальными ограничениями операционных усилителей на основе «перегнутого» каскода, которые фактически имеют один каскад усиления по напряжению на первом 7 и втором 11 выходных транзисторах.

Кроме того, максимальная амплитуда выходного отрицательного напряжения в известной схеме всегда на 1,0-1,4 В меньше, чем напряжение на второй 9 отрицательной шине источника питания. Для схем с низковольтным питанием это неприемлемо.

Следует также отметить, что схема ОУ-прототипа в диапазоне рабочих, прежде всего низких температур, а также при воздействии потока нейтронов имеет повышенные значения напряжения смещения нуля (Uсм) (единицы-десятки милливольт). В конечном итоге это снижает прецизионность известного ОУ. Данный эффект объясняется повышенным влиянием на Uсм погрешностей токового зеркала 14, которое реализуется в практических схемах на p-n-р транзисторах.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления разомкнутого ОУ.

Первая дополнительная задача состоит в повышении эффективности использования напряжения отрицательного источника питания 9.

Вторая дополнительная задача - уменьшение напряжения смещения нуля.

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с эмиттером первого 7 выходного транзистора и через первый 8 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с эмиттером второго 11 выходного транзистора и через второй 12 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, источник опорного напряжения 13, связанный с базами первого 7 и второго 11 выходных транзисторов, токовое зеркало 14, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 15, предусмотрены новые элементы и связи - коллекторы первого 7 и второго 11 выходных транзисторов соединены с первой 3 шиной источника питания, первый 6 токовый выход входного дифференциального каскада 1 связан с эмиттером первого 7 выходного транзистора через первый 16 дополнительный резистор, второй 10 токовый выход входного дифференциального каскада 1 связан с эмиттером второго 11 выходного транзистора через второй 17 дополнительный резистор, причем источник опорного напряжения 13 выполнен на основе дополнительного инвертирующего усилителя синфазного сигнала 18, выход которого через вспомогательный источник опорного тока 19 связан с первой 3 шиной источника питания, первый вход 20 дополнительного инвертирующего усилителя синфазного сигнала 18 соединен с первым 6 токовым выходом входного дифференциального каскада 1 и базой первого 21 дополнительного транзистора, второй вход 22 дополнительного инвертирующего усилителя синфазного сигнала 18 соединен со вторым 10 токовым выходом входного дифференциального каскада 1 и базой второго 23 дополнительного транзистора, коллектор первого 21 дополнительного транзистора соединен со входом токового зеркала 14, коллектор второго 23 дополнительного транзистора подключен к выходу токового зеркала 14 и выходу устройства 15, а эмиттеры первого 21 и второго 23 дополнительных транзисторов связаны со второй 9 шиной источника питания.

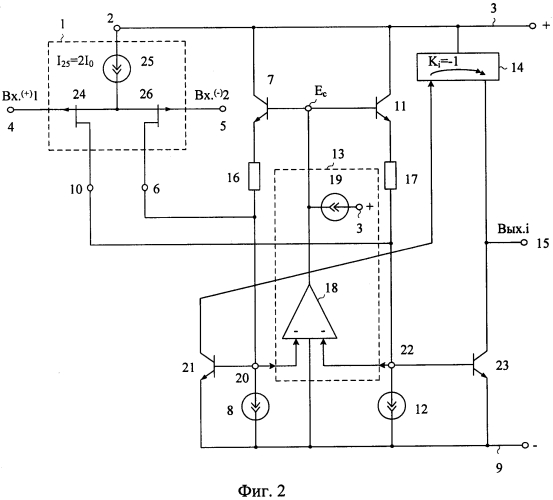

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 показана схема фиг. 2 с конкретным выполнением дополнительного инвертирующего усилителя синфазного сигнала 13 на основе транзисторов 27 и 28.

На чертеже фиг. 4 представлена схема ОУ в соответствии с п. 2 формулы изобретения.

На чертеже фиг. 5 приведена схема заявляемого устройства фиг. 3 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На чертеже фиг. 6 показана амплитудно-частотная характеристика коэффициента усиления по напряжению разомкнутого ОУ фиг. 3.

На чертеже фиг. 7 приведена зависимость напряжения смещения нуля ОУ фиг. 3 от температуры в диапазоне минус 60÷+80°С (а) и потока нейтронов в диапазоне Fn=1012÷1018 н/м2 (б). При этом предполагалось, что транзисторы схемы имеют достаточно высокую идентичность, а токовое зеркало 14 - идеально. Данный режим позволяет определить предельные параметры заявляемого устройства по Uсм.

На чертеже фиг. 8 приведена схема заявляемого устройства фиг. 4 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск) для случая, когда токовое зеркало 14 реализовано на p-n-р транзисторах АБМК_1_3, которые не отличаются высокой радиационной стойкостью [13].

На чертеже фиг. 9 приведена схема ОУ-прототипа фиг. 1 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск) для случая, когда токовое зеркало 14 так же ,как и в схеме фиг. 8, реализовано на p-n-р транзисторах АБМК_1_3.

На чертеже фиг. 10 представлены амплитудно-частотные характеристики заявляемого устройства и известного ОУ-прототипа. Из данных графиков следует, что предлагаемое устройство имеет более высокий (на 35,5 дБ) коэффициент усиления по напряжению.

На чертеже фиг. 11 приведена зависимость напряжения смещения нуля сравниваемых ОУ фиг. 8 и фиг. 9 от температуры в диапазоне минус 60÷+80°С (а) и от потока нейтронов в диапазоне (б). Из данных графиков следует, что предлагаемая схема ОУ имеет значительно меньшие напряжения смещения нуля при внешних воздействиях.

Биполярно-полевой операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с эмиттером первого 7 выходного транзистора и через первый 8 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, второй 10 токовый выход входного дифференциального каскада 1, связанный с эмиттером второго 11 выходного транзистора и через второй 12 токостабилизирующий двухполюсник соединенный со второй 9 шиной источника питания, источник опорного напряжения 13, связанный с базами первого 7 и второго 11 выходных транзисторов, токовое зеркало 14, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 15. Коллекторы первого 7 и второго 11 выходных транзисторов соединены с первой 3 шиной источника питания, первый 6 токовый выход входного дифференциального каскада 1 связан с эмиттером первого 7 выходного транзистора через первый 16 дополнительный резистор, второй 10 токовый выход входного дифференциального каскада 1 связан с эмиттером второго 11 выходного транзистора через второй 17 дополнительный резистор, причем источник опорного напряжения 13 выполнен на основе дополнительного инвертирующего усилителя синфазного сигнала 18, выход которого через вспомогательный источник опорного тока 19 связан с первой 3 шиной источника питания, первый вход 20 дополнительного инвертирующего усилителя синфазного сигнала 18 соединен с первым 6 токовым выходом входного дифференциального каскада 1 и базой первого 21 дополнительного транзистора, второй вход 22 дополнительного инвертирующего усилителя синфазного сигнала 18 соединен со вторым 10 токовым выходом входного дифференциального каскада 1 и базой второго 23 дополнительного транзистора, коллектор первого 21 дополнительного транзистора соединен со входом токового зеркала 14, коллектор второго 23 дополнительного транзистора подключен к выходу токового зеркала 14 и выходу устройства 15, а эмиттеры первого 21 и второго 23 дополнительных транзисторов связаны со второй 9 шиной источника питания.

В схеме фиг. 2 входной дифференциальный каскад 1 реализован на входных полевых транзисторах 24, 26 и источнике опорного тока 25.

В схеме фиг. 3 для уменьшения выходного сопротивления ОУ может применяться традиционный буферный усилитель 29 с низкоомным потенциальным выходом 30.

Кроме того, в схеме фиг. 3 дополнительный инвертирующий усилитель синфазного сигнала 13 реализован на транзисторах 27, 28.

На чертеже фиг. 4, в соответствии с п. 2 формулы изобретения, в схему введен дополнительный входной дифференциальный каскад 31, с первым 32 и вторым 33 дополнительными входами устройства, первый 34 токовый выход которого соединен с первым 6 токовым выходом входного дифференциального каскада 1, а второй 35 токовый выход дополнительного входного дифференциального каскада 31 соединен со вторым 10 токовым выходом входного дифференциального каскада 1, причем общая истоковая цепь 36 дополнительного входного дифференциального каскада 31 связана с первой 3 шиной источника питания.

При компьютерном моделировании заявляемых устройств в схемах фиг. 5, фиг. 8, фиг. 10 предусматривалось симметрирование статического режима транзисторов по напряжению коллектор-база с помощью источника напряжения V4.

Рассмотрим работу ОУ фиг. 3.

Статический режим транзисторов схемы фиг. 3 устанавливается входным дифференциальным каскадом 1 - его источником опорного тока 25, токостабилизирующим двухполюсником 19, а также дополнительным инвертирующим усилителем синфазного сигнала 13.

На основании первого закона Кирхгофа с учетом основных токовых соотношений в транзисторах при I8=2I0, I12=2I0, I19=2I0 можно найти, что статические токи истоков (Ici) и токи эмиттеров (Iэi) (коллекторов Iкi) в схеме фиг. 3 принимают следующие значения:

где I0 - заданный квант тока, например, 1 мА;

I8, I12 - токи первого 8 и второго 12 токостабилизирующих двухполюсников.

Коэффициент усиления по напряжению ОУ фиг. 3 определяется произведением

где - коэффициент передачи напряжения со входов 4, 5 ОУ ко входам 20 и 22 дополнительного инвертирующего усилителя синфазного сигнала 13;

- коэффициент передачи напряжения со входов 20, 22 дополнительного инвертирующего усилителя синфазного сигнала 13 на выход устройства 15.

Причем

где - эквивалентная крутизна входного дифференциального каскада 1 относительно токовых выходов 6 и 10;

S24, S26 - крутизна входных полевых транзисторов 24 и 26;

Rэкв6-10≈R16=R17 - эквивалентное сопротивление нагрузки входного дифференциального каскада 1 в узлах 6 и 10.

Коэффициент усиления второго каскада

где R15 - эквивалентное сопротивление в цепи выхода 15;

SПК - крутизна преобразования напряжения u20-22 в выходной ток устройства (ток узла 15).

Причем

где - сопротивления эмиттерных переходов транзисторов 21 и 23;

φт=26 мВ - температурный потенциал.

Таким образом, общий коэффициент усиления предлагаемого ОУ:

В схеме ОУ-прототипа фиг. 1 входной каскад не обеспечивает усиление по напряжению. Поэтому его общий коэффициент усиления

Следовательно, предлагаемый ОУ в разомкнутом состоянии имеет в Ny-раз больший коэффициент усиления по напряжению, где

При этом, в отличие от ОУ-прототипа, максимальные амплитуды положительных и отрицательных выходных напряжений здесь близки к соответствующим напряжениям на первой 3 и второй 9 шинах питания (Е3, Е9):

В ОУ-прототипе фиг. 1 условие (15) не выполняется:

где Uэб11≈0,7 В - напряжение эмиттер-база второго 11 выходного транзистора;

UR12 - напряжение на втором 12 токостабилизирующем двухполюснике.

Предлагаемый ОУ может послужить также основой для создания так называемых мультидифференциальных ОУ (фиг. 4), которые имеют ряд существенных преимуществ в сравнении с классическими ОУ [14-16].

За счет дополнительного усиления (Ky1) в заявляемой схеме фиг. 2 уменьшается в КУ1-раз величина Uсм, обусловленная влиянием на Uсм погрешностей токового зеркала 14 на p-n-р транзисторах (фиг. 10, фиг. 11).

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Библиографический список

1. Патентная заявка US 2002/0196079, fig. 1.

2. Патент US 4.600.893, fig. 7.

3. Патент US 4.387.309.

4. Патент GB 2.035.003, fig. 2.

5. Патент US 7.215.200, fig. 6.

6. Патент US 4.406.990, fig. 4.

7. Патент US 6.788.143.

8. Патент US 4.004.245

9. Патент US 4.406.990, fig. 4.

10. Патент US 5.420.540.

11. Патент US 5.963.085.

12. Патент US 4.390.850.

13. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

14. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы. Выпуск 2 (233), 2014 г. С. 53-64.

15. Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, Н.В. Бутырлагин, И.В. Пахомов // Проблемы разработки перспективных микро- и наноэлектронных систем - 2014. Сборник трудов. Часть 3 / под общ. ред. академика РАН А.Л. Стемпковского. - М: ИППМ РАН, 2014. - С. 111-116.

16. The main connection circuits of the radiation-hardened differential difference amplifier based on the bipolar and field effect technological process / N.N. Prokopenko, O.V. Dvornikov, N.V. Butyrlagin, A.V. Bugakova // 2014 12th International conference on actual problems of electronic instrument engineering (APEIE - 2014) proceedings in 7 Volumes; Novosibirsk, October 2-4, 2014. - Novosibirsk State Technical University. - Vol. 1. - P. 29-34 DOI: 10.1109/APEIE.2014.7040870.

1. Биполярно-полевой операционный усилитель, содержащий входной дифференциальный каскад (1), общая истоковая цепь которого (2) связана с первой (3) шиной источника питания, первый (4) и второй (5) входы входного дифференциального каскада (1), первый (6) токовый выход входного дифференциального каскада (1), связанный с эмиттером первого (7) выходного транзистора и через первый (8) токостабилизирующий двухполюсник соединенный со второй (9) шиной источника питания, второй (10) токовый выход входного дифференциального каскада (1), связанный с эмиттером второго (11) выходного транзистора и через второй (12) токостабилизирующий двухполюсник соединенный со второй (9) шиной источника питания, источник опорного напряжения (13), связанный с базами первого (7) и второго (11) выходных транзисторов, токовое зеркало (14), согласованное с первой (3) шиной источника питания, выход которого соединен с токовым выходом устройства (15), отличающийся тем, что коллекторы первого (7) и второго (11) выходных транзисторов соединены с первой (3) шиной источника питания, первый (6) токовый выход входного дифференциального каскада (1) связан с эмиттером первого (7) выходного транзистора через первый (16) дополнительный резистор, второй (10) токовый выход входного дифференциального каскада (1) связан с эмиттером второго (11) выходного транзистора через второй (17) дополнительный резистор, причем источник опорного напряжения (13) выполнен на основе дополнительного инвертирующего усилителя синфазного сигнала (18), выход которого через вспомогательный источник опорного тока (19) связан с первой (3) шиной источника питания, первый вход (20) дополнительного инвертирующего усилителя синфазного сигнала (18) соединен с первым (6) токовым выходом входного дифференциального каскада (1) и базой первого (21) дополнительного транзистора, второй вход (22) дополнительного инвертирующего усилителя синфазного сигнала (18) соединен со вторым (10) токовым выходом входного дифференциального каскада (1) и базой второго (23) дополнительного транзистора, коллектор первого (21) дополнительного транзистора соединен со входом токового зеркала (14), коллектор второго (23) дополнительного транзистора подключен к выходу токового зеркала (14) и выходу устройства (15), а эмиттеры первого (21) и второго (23) дополнительных транзисторов связаны со второй (9) шиной источника питания.

2. Биполярно-полевой операционный усилитель по п. 1, отличающийся тем, что в схему введен дополнительный входной дифференциальный каскад (31) с первым (32) и вторым (33) дополнительными входами устройства, первый (34) токовый выход которого соединен с первым (6) токовым выходом входного дифференциального каскада (1), а второй (35) токовый выход дополнительного входного дифференциального каскада (31) соединен со вторым (10) токовым выходом входного дифференциального каскада (1), причем общая истоковая цепь (36) дополнительного входного дифференциального каскада (31) связана с первой (3) шиной источника питания.