Дискретный согласованный фильтр

Иллюстрации

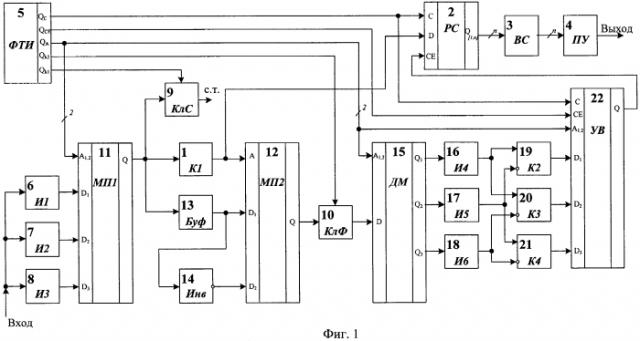

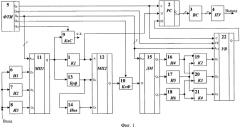

Показать всеИзобретение относится к технике цифровой связи и сигнализации и может быть использовано для квазиоптимального асинхронного приема сообщений. Технический результат - упрощение реализации и повышение надежности работы фильтра. Устройство содержит компаратор с порогом срабатывания по среднему уровню (1), n-разрядный регистр сдвига (2), весовой сумматор (3), пороговое устройство (4), формирователь тактовых импульсов (5), три интегратора (6-8) с малым значением постоянной времени, ключи сброса (9) и фиксации (10), мультиплексоры (11, 12), буферный усилитель (13), инвертор (14), демультиплексор (15), три интегратора с большим значением постоянной времени (16-18), три компаратора (19-21) и оригинальное устройство выбора интервала тактирования регистра сдвига (22). 1 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к технике цифровой связи и сигнализации и может быть использовано для квазиоптимального асинхронного приема сообщений.

Известно устройство тактовой синхронизации дискретного согласованного фильтра (патент Российской Федерации №2218668, МПК6 H03L 7/06), обеспечивающее, за счет введения кольца фазовой автоподстройки внутреннего тактового генератора, повышение среднего значения сигнал/помеха.

Недостатком данного устройства является неустойчивая работа системы автоподстройки при малых отношениях сигнал/шум на входе дискретного согласованного фильтра, а также при определенных исходных фазовых соотношениях входного сигнала и внутреннего тактового генератора.

Известен двухканальный дискретный согласованный фильтр (патент Российской Федерации №2310978, МПК6 H03H 17/00), обеспечивающий асинхронный прием кодовых последовательностей на видеочастоте по каналу с минимальным фазовым сдвигом символов сигнала и интервалов их обработки.

Недостатком данного фильтра является недостаточная чувствительность для наихудших фазовых соотношений входного сигнала и внутреннего тактового генератора, когда для принятия решения используется только половина энергии сигнала.

Наиболее близким по технической сущности к заявляемому изобретению является выбранный в качестве прототипа многоканальный дискретный согласованный фильтр (Быков Ю.Н., Дудко В.К., Сизов А.С. Оценка помехоустойчивости системы телеуправления с обработкой сигналов многоканальным дискретным согласованным фильтром // Телекоммуникации. 2008. №10. С. 29-33), обеспечивающий асинхронный прием кодовых последовательностей, близкий к оптимальному.

Недостатком многоканального дискретного согласованного фильтра является повышенная сложность конструкции, что определяет практическую непригодность его применения в мобильных устройствах для обработки сигналов с большой базой.

Целью изобретения является упрощение конструкции дискретного согласованного фильтра для обработки кодовых последовательностей с большой базой за счет использования только одного канала свертки и реализации функции его адаптивного тактирования в зависимости от фазовых соотношений входного сигнала и внутреннего тактового генератора.

Цель достигается тем, что в известный дискретный согласованный фильтр, содержащий последовательно соединенные первый компаратор, n-разрядный регистр сдвига, весовой сумматор и пороговое устройство, формирователь тактовых импульсов, три соединенных по входу интегратора с малым значением постоянной времени, ключ сброса и ключ фиксации, согласно изобретению введены первый и второй мультиплексоры, последовательно соединенные буферный усилитель и инвертор, демультиплексор, три интегратора с большим значением постоянной времени, три компаратора и устройство выбора интервала тактирования регистра сдвига, причем выход общего тактирования формирователя тактовых импульсов соединен с тактовыми входами регистра сдвига и устройства выбора интервала тактирования, выход разрешения тактирования формирователя тактовых импульсов соединен с одноименным входом устройства выбора интервала тактирования, адресные выходы формирователя тактовых импульсов соединены с одноименными входами первого мультиплексора, демультиплексора и устройства выбора интервала тактирования, а выходы управления ключами формирователя тактовых импульсов соединены со входами управления соответствующих ключей сброса и фиксации, выходы первого, второго и третьего интеграторов с малым значением постоянной времени соединены с соответствующими сигнальными входами первого мультиплексора, выход которого соединен с входами первого компаратора, ключа сброса и буферного усилителя, выходы буферного усилителя и инвертора соединены с первым и вторым сигнальными входами второго мультиплексора соответственно, выход ключа сброса соединен со средней точкой питания, адресный вход второго мультиплексора соединен с выходом первого компаратора, а выход - со входом ключа фиксации, выход ключа фиксации соединен со входом демультиплексора, первый, второй и третий информационные выходы которого соединены со входами четвертого, пятого и шестого интеграторов с большим значением постоянной времени соответственно, выход четвертого интегратора соединен с прямыми входами второго и третьего компараторов, выход пятого интегратора соединен с инверсным входом второго компаратора и прямым входом четвертого компаратора, выход шестого интегратора соединен с инверсными входами третьего и четвертого компараторов, выходы второго, третьего и четвертого компараторов соединены соответственно с первым, вторым и третьим информационными входами устройства выбора интервала тактирования, выход которого соединен с входом разрешения тактирования регистра сдвига.

Устройство выбора интервала тактирования содержит семь логических элементов 2И, у второго из которых первый вход является инверсным, логические элементы 2ИЛИ-НЕ, 2ИЛИ и 3ИЛИ, два логических элемента 3ИЛИ-НЕ, три реверсивных сдвиговых регистра, четыре D-триггера и мультиплексор, причем первый вход первого элемента 2И соединен с инверсным входом второго элемента 2И и является первым информационным входом устройства выбора интервала тактирования, второй вход первого элемента 2И соединен с первым входом элемента 2ИЛИ-НЕ и является вторым информационным входом устройства выбора интервала тактирования, прямой вход второго элемента 2И соединен со вторым входом элемента 2ИЛИ-НЕ и является третьим информационным входом устройства выбора интервала тактирования, выходы первого и второго элементов 2И и элемента 2ИЛИ-НЕ соединены соответственно с входами управления направлением сдвига первого, второго и третьего реверсивных сдвиговых регистров, информационные входы для сдвига вправо которых соединены с уровнем логической единицы, а информационные входы для сдвига влево - с уровнем логического нуля, тактовые входы регистров объединены между собой и с тактовыми входами D-триггеров и являются тактовым входом устройства выбора интервала тактирования, выход старшего разряда первого регистра соединен с D-входом первого триггера и первыми входами третьего элемента 2И и элемента 3ИЛИ, выход старшего разряда второго регистра соединен с D-входом второго триггера и вторыми входами четвертого элемента 2И и элемента 3ИЛИ, выход старшего разряда третьего регистра соединен с D-входом третьего триггера, вторым входом пятого элемента 2И и третьим входом элемента 3ИЛИ, выход первого D-триггера соединен с входом сброса первого регистра, первым входом четвертого элемента 2И, третьим входом первого элемента 3ИЛИ-НЕ и вторым входом элемента 2ИЛИ, выход второго D-триггера соединен с входом сброса второго регистра, первым входом пятого элемента 2И, вторым входом первого элемента 3ИЛИ-НЕ и вторым информационным входом мультиплексора, выход третьего D-триггера соединен с входом сброса третьего регистра, вторым входом третьего элемента И, первым входом первого элемента 3ИЛИ-НЕ и третьим информационным входом мультиплексора, выходы третьего, четвертого и пятого элементов 2И соединены соответственно с первым, вторым и третьим входами второго элемента 3ИЛИ-НЕ, выход которого соединен с D-входом четвертого триггера, выход первого элемента 3ИЛИ-НЕ соединен с первым входом элемента 2ИЛИ, выход которого соединен с первым информационным входом мультиплексора, вход выбора и адресные входы мультиплексора являются входами разрешения тактирования и адресными входами устройства выбора интервала тактирования соответственно, выход мультиплексора соединен с входом разрешения тактирования четвертого триггера и вторыми входами шестого и седьмого элементов 2И, выход элемента 3ИЛИ соединен с первым входом седьмого элемента 2И, выход которого соединен со входами разрешения тактирования первого, второго и третьего триггеров, выход четвертого триггера соединен с первым входом шестого элемента 2И, выход которого соединен с входами разрешения тактирования регистров и является выходом устройства выбора интервала тактирования.

Сопоставительный анализ технического решения с устройством, выбранным в качестве прототипа, показывает, что новизна технического решения заключается в ведении в заявленное устройство новых схемных элементов: двух мультиплексоров, буферного усилителя, инвертора, демультиплексора, трех интеграторов, трех компараторов и устройства выбора интервала тактирования.

Таким образом, заявляемое техническое решение соответствует критерию изобретения «новизна».

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в дискретный согласованный фильтр с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют упростить аппаратную реализацию дискретного согласованного фильтра при сохранении высокой помехоустойчивости приема информации.

Таким образом, техническое решение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано для квазиоптимального приема кодовых последовательностей в мобильных устройствах цифровой связи и сигнализации.

Таким образом, изобретение соответствует критерию "промышленная применимость".

На фиг. 1 представлена структурная блок-схема дискретного согласованного фильтра,

на фиг. 2 - структурная блок-схема устройства выбора интервала тактирования,

на фиг. 3-5 - временные диаграммы функционирования дискретного согласованного фильтра.

Дискретный согласованный фильтр (фиг. 1) содержит: компаратор с порогом срабатывания по среднему уровню 1, n-разрядный регистр сдвига 2, весовой сумматор 3, пороговое устройство 4, формирователь тактовых импульсов 5, три интегратора 6-8, значения постоянных времени которых согласованы с длительностью элемента сигнала, ключ сброса 9, ключ фиксации 10, мультиплексоры 11 и 12, буферный усилитель 13 и инвертор 14, демультиплексор 15, три интегратора с большим значением постоянной времени 16-18, три компаратора 19-21 и устройство выбора интервала тактирования регистра сдвига 22, причем выход компаратора 1 соединен с адресным входом А мультиплексора 12 и с D-входом регистра сдвига 2, выходы которого соединены с последовательно соединенными весовой матрицей 3 и пороговым устройством 4, выход порогового устройства 4 является выходом дискретного согласованного фильтра, входы интеграторов 6-8 объединены и являются входом дискретного согласованного фильтра, а выходы интеграторов 6-8 соединены с информационными входами D1, D2 и D3 мультиплексора 11 соответственно, выход мультиплексора 11 соединен со входами компаратора 1, ключа сброса 9 и буферного усилителя 13, выход которого соединен с информационным входом D1 мультиплексора 12 и входом инвертора 14, выход инвертора 14 соединен с информационным входом D2 мультиплексора 12, выход которого соединен со входом ключа фиксации 10, входы управления ключей сброса 9 и фиксации 10 соединены с выходами Qk1 и Qk2 формирователя тактовых импульсов 5 соответственно, выход ключа сброса 9 соединен со средней точкой питания дискретного согласованного фильтра, выход ключа фиксации 10 соединен с информационным входом D демультиплексора 15, выходы Q1, Q2 и Q3 которого соединены с входами интеграторов 16, 17 и 18 соответственно, выход интегратора 16 соединен с прямыми входами компараторов 19 и 20, выход интегратора 17 соединен с инверсным входом компаратора 19 и прямым входом компаратора 21, выход интегратора 18 соединен с инверсными входами компараторов 20 и 21, выходы компараторов 19-21 соединены с информационными входами D1, D2 и D3 устройства выбора интервала тактирования 22 соответственно, выход которого соединен с входом разрешения тактирования CE регистра сдвига 2, тактовые входы C регистра сдвига 2 и устройства выбора интервала тактирования 22 объединены и соединены с выходом тактирования QC формирователя тактовых импульсов 5, выход разрешения тактирования QCE которого соединен с входом разрешения тактирования CE устройства выбора интервала тактирования 22, адресные входы A мультиплексора 11, демультиплексора 15 и устройства выбора интервала тактирования 22 объединены с соответствующими адресными выходами QA формирователя тактовых импульсов 5.

Устройство выбора интервала тактирования (фиг. 2) содержит: шесть логических элементов 2И 23, 25-29, логический элемент 2И с инверсным первым входом 24, логические элементы 2ИЛИ-НЕ 30, 2ИЛИ 31 и 3ИЛИ 32, два логических элемента 3ИЛИ-НЕ 33 и 34, три трехразрядных реверсивных сдвиговых регистра 35-37, четыре D-триггера 38-41 и мультиплексор 42, причем первый вход элемента 2И 23 соединен с инверсным входом элемента 2И 24 и является первым информационным входом D1 устройства выбора интервала тактирования, второй вход элемента 2И 23 соединен с первым входом элемента 2ИЛИ-НЕ 30 и является вторым информационным входом D2 устройства выбора интервала тактирования, второй вход элемента 2И 24 соединен со вторым входом элемента 2ИЛИ-НЕ 30 и является третьим информационным входом D3 устройства выбора интервала тактирования, выходы элементов 2И 23, 24 и элемента 2ИЛИ-НЕ 30 соединены соответственно с входами управления направлением сдвига информации +/- регистров 35-37, тактовые входы которых объединены между собой и с тактовыми входами триггеров 38-41 и являются тактовым входом C устройства выбора интервала тактирования, информационные входы регистров 35-37 для сдвига вправо RSI соединены с уровнем логической единицы (шиной питания), а информационные входы для сдвига влево LSI - с уровнем логического нуля (общей шиной), выход старшего разряда регистра 35 соединен с D-входом триггера 38 и первыми входами элемента 2И 25 и элемента 3ИЛИ 32, выход старшего разряда регистра 36 соединен с D-входом триггера 39 и вторыми входами элемента 2И 26 и элемента 3ИЛИ 32, выход старшего разряда регистра 37 соединен с D-входом триггера 40, вторым входом элемента 2И 27 и третьим входом элемента 3ИЛИ 32, выход триггера 38 соединен с входом сброса регистра 35, первым входом элемента 2И 26, третьим входом элемента 3ИЛИ-НЕ 33 и вторым входом элемента 2ИЛИ 31, выход триггера 39 соединен с входом сброса регистра 36, первым входом элемента 2И 27, вторым входом элемента 3ИЛИ-НЕ 33 и информационным входом D2 мультиплексора 42, выход триггера 40 соединен с входом сброса регистра 37, вторым входом элемента 2И 25, первым входом элемента 3ИЛИ-НЕ 33 и информационным входом D3 мультиплексора 42, выходы элементов 2И 25-27 соединены соответственно с первым, вторым и третьим входами элемента 3ИЛИ-НЕ 34, выход которого соединен с D-входом триггера 41, выход элемента 3ИЛИ-НЕ 33 соединен с первым входом элемента 2ИЛИ 31, выход которого соединен с первым информационным входом D1 мультиплексора 42, вход выбора CE и адресные входы A1, А2 мультиплексора 42 являются одноименными входами устройства выбора интервала тактирования, выход мультиплексора 42 соединен с входом разрешения тактирования триггера 41 и вторыми входами элементов 2И 28 и 29, выход элемента 3ИЛИ 32 соединен с первым входом элемента 2И 29, выход которого соединен со входами разрешения тактирования триггеров 38-40, выход триггера 41 соединен с первым входом элемента 2И 28, выход которого соединен с входами разрешения тактирования регистров 35-37 и является выходом устройства выбора интервала тактирования.

Предлагаемый дискретный согласованный фильтр (ДСФ) работает следующим образом.

На входе ДСФ действует нормальный белый шум при отсутствии сигналов или смесь сигнала и шума. На фиг. 3а показан пример сигнала, поступающего на вход ДСФ с выхода детектора приемного устройства при большом отношении сигнал/шум.

Сигнал (шум) интегрируется относительно средней точки питания интеграторами 6-8 отрезками, равными длительности элементарного символа кода, как показано на соответствующих эпюрах фиг. 3б-3г.

Границы интервалов интегрирования и их сдвиг относительно друг друга определяются формирователем тактовых импульсов 5. На фиг. 3д, 3е показаны адресные сигналы формирователя тактовых импульсов 5, определяющие коммутацию интеграторов 6-8 и 16-18, на фиг. 3ж показаны интервалы включения ключа сброса 9, определяющие установку выбранного входного интегратора 6, 7 или 8 в исходное состояние (приведение значения напряжения к средней точке), а на фиг. 3з - интервалы включения ключа фиксации 10, определяющие заряд/разряд выбранного выходного интегратора 16, 17 или 18.

В момент включения ключа фиксации 10 положительные относительно средней точки значения амплитуд с выхода выбранного входного интегратора через буферный усилитель 13, мультиплексор 12, ключ 10 и демультиплексор 15 подаются на соответствующие интеграторы с большой постоянной времени 16-18, как показано на фиг. 3и-3л. Отрицательные относительно средней точки значения амплитуд подаются на интеграторы 16-18 через дополнительный инвертор 14. Таким образом на интеграторах 16-18 создается положительное относительно средней точки напряжение, пропорциональное степени согласованности символов сообщения с интервалами интегрирования соответствующих входных интеграторов 6-8.

На фиг. 4а в сжатом масштабе показана динамика изменения напряжений к концу интервалов интегрирования на интеграторах 16 (сплошной линией), 17 (пунктирной линией) и 18 (штрихпунктирной линией), обусловленная разницей частот сигнала и дискретного согласованного фильтра.

Напряжения на интеграторах 16-18 попарно сравниваются компараторами 19-21, как показано на фиг. 4б-4г, сигналы от которых являются информацией для вырабатывания устройством выбора интервала тактирования 22 соответствующего решения о приеме символов кода - разрешения записи в регистр сдвига 2.

Устройство выбора интервала тактирования 22 обеспечивает корректную работу регистра сдвига 2 и ДСФ в целом.

На фиг. 5 показан принцип работы устройства выбора интервала тактирования 22 в случае, когда тактовая частота фильтра выше тактовой частоты входного сигнала.

На фиг. 5а представлен пример входного сигнала, на фиг. 5б и 5в - напряжения на входных и выходных интеграторах соответственно (вид линий соответствует представленным на фиг. 4а), импульсы сброса и фиксации для каждой из пар интеграторов (6, 16), (7, 17) и (8, 18) условно показаны парами эпюр (фиг. 5г, 5д), (фиг. 5е, 5ж), (фиг. 5з, 5и) соответственно, на фиг. 5к-5м показаны сигналы на выходах компараторов 19-21, на фиг. 5н показан сигнал на выходе устройства выбора интервала тактирования 22, а на фиг. 5о - сигнал на выходе первого разряда регистра сдвига 2.

Например, во время действия на входе ДСФ элемента сигнала III (фиг. 5а) наибольшее напряжение будет на интеграторе 17 (пунктирная линия). Если бы в качестве устройства тактирования 22 был применен простой мультиплексор, в регистр сдвига были записаны два значения вместо одного. Устройство выбора интервала тактирования 22 обеспечивает исключение ложного интервала записи (показан зачеркнутым на фиг. 5н).

В случае, когда тактовая частота фильтра ниже тактовой частоты входного сигнала, устройство выбора интервала тактирования 22 работает без исключения интервалов записи.

На фиг. 5к-5м, кроме того, серым фоном показано наличие интервалов «дребезга» выходных сигналов компараторов, задача устранения влияния которых также ложится на устройство выбора интервала тактирования 22.

Устройство выбора интервала тактирования 22 работает следующим образом.

На выходах логических элементов 23, 29 и 30 формируется сигнал логической 1 в случаях наибольшего напряжения на интеграторах 19, 20 или 21 соответственно (фиг. 4д-4ж). При удержании логической единицы в течение трех интервалов подряд на выходе старшего разряда соответствующего регистра 35, 36 или 37 появляется уровень логической 1, который на следующем интервале изменяется на уровень логического 0 одновременно с появлением на выходе соответствующего триггера 38, 39 или 40 состояния логической 1. Уровень логической 1 на выходе одного из триггеров 38, 39 или 40 посредством мультиплексора 42 определяет выбор интегратора 6, 7 или 8, с которого будет осуществляться запись нормированного посредством компаратора 1 сигнала в регистр сдвига 2.

В случае, когда тактовая частота фильтра выше тактовой частоты входного сигнала, возникает ситуация, когда уровни логических 1 одновременно появляются на выходах регистра 35 и триггера 40, или на выходах регистра 36 и триггера 38, или на выходах регистра 37 и триггера 39. Посредством логических элементов 25-27 и 34 данные состояния переводят триггер 41 в состояние логического 0 на один интервал, запрещая, тем самым, посредством элемента 28 запись в регистр сдвига 2 лишнего значения.

Возможная неоднозначность работы устройства выбора интервала тактирования 22 при первоначальном включении устраняется логическими элементами 31 и 33.

Таким образом, достигнут положительный эффект, заключающийся в упрощении реализации и повышении надежности работы дискретного согласованного фильтра. Испытания опытного образца предложенного дискретного согласованного фильтра показали, что количество задействованных триггеров регистра сдвига относительно трехканального ДСФ, построенного по структуре прототипа, примерно в 3 раза меньше, а предложенная реализация взамен подстройки частоты в аналогичном устройстве работает более устойчиво, особенно для коротких сообщений.

Для реализации заявляемого устройства использованы известные элементы и схемы, выпускаемые отечественной и зарубежной промышленностью. Регистр сдвига 2, весовая матрица 3, пороговое устройство 4, формирователь тактовых импульсов 5 и устройство выбора интервала тактирования 22 реализованы на ППЛИС XILINX типа XC2C512-7FT256I. В качестве мультиплексора 11 и демультиплексора 15 применен сдвоенный аналоговый мультиплексор ADG 659 YCP, в качестве ключа сброса 9 использован аналоговый ключ MAX 7414 EXT-T, мультиплексор 12 и ключ фиксации 10 построены на сдвоенном аналоговом ключе MAX 4684 ETB+T, в качестве компараторов использованы микросхемы LMV 331H AXK-T, буферный усилитель и инвертор построены на сдвоенном операционном усилителе OPA 333 AIDCKT, интеграторы 6-8, 16-18 пассивные резистивно-емкостные.

1. Дискретный согласованный фильтр, содержащий последовательно соединенные первый компаратор 1, n-разрядный регистр сдвига 2, весовой сумматор 4 и пороговое устройство 4, формирователь тактовых импульсов 5, три соединенных по входу интегратора с малым значением постоянной времени 6-8, ключ сброса 9 и ключ фиксации 10, отличающийся тем, что введены, первый 11 и второй 12 мультиплексоры, последовательно соединенные буферный усилитель 13 и инвертор 14, демультиплексор 15, три интегратора с большим значением постоянной времени 16-18, три компаратора 19-21 и устройство выбора интервала тактирования регистра сдвига 22, причем выход общего тактирования формирователя тактовых импульсов 5 соединен с тактовыми входами регистра сдвига 2 и устройства выбора интервала тактирования 22, выход разрешения тактирования формирователя тактовых импульсов 5 соединен с одноименным входом устройства выбора интервала тактирования 22, адресные выходы формирователя тактовых импульсов 5 соединены с одноименными входами первого мультиплексора 11, демультиплексора 15 и устройства выбора интервала тактирования 22, а выходы управления ключами формирователя тактовых импульсов 5 соединены со входами управления соответствующих ключей сброса 9 и фиксации 10, выходы первого 6, второго 7 и третьего 8 интеграторов с малым значением постоянной времени соединены с соответствующими сигнальными входами первого мультиплексора 11, выход которого соединен с входами первого компаратора 1, ключа сброса 9 и буферного усилителя 13, выходы буферного усилителя 13 и инвертора 14 соединены с первым и вторым сигнальными входами второго мультиплексора 12 соответственно, выход ключа сброса 9 соединен со средней точкой питания, адресный вход второго мультиплексора 12 соединен с выходом первого компаратора 1, а выход - со входом ключа фиксации 10, выход ключа фиксации 10 соединен со входом демультиплексора 15, первый, второй и третий информационные выходы которого соединены со входами четвертого 16, пятого 17 и шестого 18 интеграторов с большим значением постоянной времени соответственно, выход четвертого интегратора 16 соединен с прямыми входами второго 19 и третьего 20 компараторов, выход пятого интегратора 17 соединен с инверсным входом второго 19 компаратора и прямым входом четвертого 21 компаратора, выход шестого интегратора 18 соединен с инверсными входами третьего 20 и четвертого 21 компараторов, выходы второго 19, третьего 20 и четвертого 21 компараторов соединены, соответственно, с первым, вторым и третьим информационными входами устройства выбора интервала тактирования 22, выход которого соединен с входом разрешения тактирования регистра сдвига 2.

2. Устройство по п. 1, отличающееся тем, что устройство выбора интервала тактирования содержит семь логических элементов 2И 23-29, у второго из которых первый вход является инверсным, логические элементы 2ИЛИ-НЕ 30, 2ИЛИ 31 и 3ИЛИ 32, два логических элемента 3ИЛИ-НЕ 33 и 34, три реверсивных сдвиговых регистра 35-37, четыре D-триггера 38-41 и мультиплексор 42, причем первый вход первого элемента 2И 23 соединен с инверсным входом второго элемента 2И 24 и является первым информационным входом устройства выбора интервала тактирования, второй вход первого элемента 2И 23 соединен с первым входом элемента 2ИЛИ-НЕ 30 и является вторым информационным входом устройства выбора интервала тактирования, прямой вход второго элемента 2И 24 соединен со вторым входом элемента 2ИЛИ-НЕ 30 и является третьим информационным входом устройства выбора интервала тактирования, выходы первого 23 и второго 24 элементов 2И и элемента 2ИЛИ-НЕ 30 соединены, соответственно, с входами управления направлением сдвига первого 35, второго 36 и третьего 37 реверсивных сдвиговых регистров, информационные входы для сдвига вправо которых соединены с уровнем логической единицы, а информационные входы для сдвига влево - с уровнем логического нуля, тактовые входы регистров 35-37 объединены между собой и с тактовыми входами D-триггеров 38-41 и являются тактовым входом устройства выбора интервала тактирования, выход старшего разряда первого регистра 35 соединен с D-входом первого триггера 38 и первыми входами третьего элемента 2И 25 и элемента 3ИЛИ 32, выход старшего разряда второго регистра 36 соединен с D-входом второго триггера 39 и вторыми входами четвертого элемента 2И 26 и элемента 3ИЛИ 32, выход старшего разряда третьего регистра 37 соединен с D-входом третьего триггера 40, вторым входом пятого элемента 2И 27 и третьим входом элемента 3ИЛИ 32, выход первого D-триггера 38 соединен с входом сброса первого регистра 35, первым входом четвертого элемента 2И 26, третьим входом первого элемента 3ИЛИ-НЕ 33 и вторым входом элемента 2ИЛИ 31, выход второго D-триггера 39 соединен с входом сброса второго регистра 36, первым входом пятого элемента И 27, вторым входом первого элемента 3ИЛИ-НЕ 33 и вторым информационным входом мультиплексора 42, выход третьего D-триггера 40 соединен с входом сброса третьего регистра 37, вторым входом третьего элемента 2И 25, первым входом первого элемента 3ИЛИ-НЕ 33 и третьим информационным входом мультиплексора 42, выходы третьего 25, четвертого 26 и пятого 27 элементов 2И соединены, соответственно, с первым, вторым и третьим входами второго элемента 3ИЛИ-НЕ 34, выход которого соединен с D-входом четвертого триггера 41, выход первого элемента 3ИЛИ-НЕ 33 соединен с первым входом элемента 2ИЛИ 31, выход которого соединен с первым информационным входом мультиплексора 42, вход выбора и адресные входы мультиплексора 42 являются входами разрешения тактирования и адресными входами устройства выбора интервала тактирования соответственно, выход мультиплексора 42 соединен с входом разрешения тактирования четвертого триггера 41 и вторыми входами шестого 28 и седьмого 29 элементов 2И, выход элемента 3ИЛИ 32 соединен с первым входом седьмого элемента 2И 29, выход которого соединен со входами разрешения тактирования первого 38, второго 39 и третьего 40 триггеров, выход четвертого триггера 41 соединен с первым входом шестого элемента 2И 28, выход которого соединен с входами разрешения тактирования регистров 35-37 и является выходом устройства выбора интервала тактирования.