Устройство формирования изображений, система формирования изображений и способ производства устройства формирования изображений

Иллюстрации

Показать всеИспользование: для формирования изображения. Сущность изобретения заключается в том, что устройство формирования изображений содержит полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке, при этом полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости, первую область затвора второго типа проводимости, вторую область затвора второго типа проводимости, третью область затвора второго типа проводимости и четвертую область затвора второго типа проводимости, первая область затвора и вторая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки, третья область затвора и четвертая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки, первая область затвора и третья область затвора расположены в направлении глубины полупроводниковой подложки, первая область затвора расположена между упомянутой поверхностью и третьей областью затвора, вторая область затвора и четвертая область затвора расположены в направлении глубины, вторая область затвора расположена между упомянутой поверхностью и четвертой областью затвора, область канала включает в себя первую область, которая расположена между первой областью затвора и третьей областью затвора, и вторую область, которая расположена между второй областью затвора и четвертой областью затвора, истоковая область расположена между первой областью затвора и второй областью затвора, и полупроводниковая область второго типа проводимости, имеющая концентрацию примеси, которая ниже, чем концентрация примеси третьей области затвора, и ниже, чем концентрация примеси четвертой области затвора, расположена между третьей областью затвора и четвертой областью затвора. Технический результат: обеспечение возможности улучшения характеристик полевого транзистора с p-n-переходом. 5 н. и 15 з.п. ф-лы, 9 ил.

Реферат

УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее раскрытие относится к устройству формирования изображений, системам формирования изображений и способам производства устройства формирования изображений.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Было предложено устройство формирования изображений, в котором используются полевые транзисторы с p-n-переходом. В японском выложенном патенте №2007-165736 описывается устройство формирования изображений, включающее в себя множество пикселов. Каждый пиксел включает в себя полевой транзистор с p-n-переходом. В полевом транзисторе с p-n-переходом, описанном в японском выложенном патенте № 2007-165736, область канала расположена между слоями поверхностной области затвора и скрытой области затвора. Область канала соединена с стоковой областью в оконечной части скрытой области затвора.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Согласно первому аспекту настоящего раскрытия, обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости, и с первой по четвертую области затвора второго типа проводимости. Первая область затвора и вторая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Третья область затвора и четвертая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Первая область затвора и третья область затвора расположены в направлении глубины полупроводниковой подложки. Первая область затвора расположена между поверхностью и третьей областью затвора. Вторая область затвора и четвертая область затвора расположены в направлении глубины. Вторая область затвора расположена между поверхностью и четвертой областью затвора. Область канала включает в себя первую область и вторую область. Первая область расположена между первой областью затвора и третьей областью затвора. Вторая область расположена между второй областью затвора и четвертой областью затвора. Истоковая область расположена между первой областью затвора и второй областью затвора. Полупроводниковая область второго типа проводимости расположена между третьей областью затвора и четвертой областью затвора. Полупроводниковая область второго типа проводимости имеет концентрацию примеси, которая ниже, чем концентрация примеси третьей области затвора, и ниже, чем концентрация примеси четвертой области затвора.

[0004] Согласно другому аспекту настоящего раскрытия обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости, и с первой по четвертую области затвора второго типа проводимости. Первая область затвора и вторая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Третья область затвора и четвертая область затвора расположены в направлении вдоль поверхности полупроводниковой подложки. Первая область затвора и третья область затвора расположены в направлении глубины полупроводниковой подложки. Первая область затвора расположена между поверхностью и третьей областью затвора. Вторая область затвора и четвертая область затвора расположены в направлении глубины. Вторая область затвора расположена между поверхностью и четвертой областью затвора. Область канала включает в себя первую область и вторую область. Первая область расположена между первой областью затвора и третьей областью затвора. Вторая область расположена между второй областью затвора и четвертой областью затвора. Истоковая область расположена между первой областью затвора и второй областью затвора. Полупроводниковая область первого типа проводимости обеспечена таким образом, чтобы продолжаться в пространственном отношении от третьей области затвора до четвертой области затвора.

[0005] Согласно другому аспекту настоящего раскрытия обеспечено устройство формирования изображений. Устройство формирования изображений включает в себя полевой транзистор с p-n-переходом, обеспеченный на полупроводниковой подложке. Полевой транзистор с p-n-переходом включает в себя область канала первого типа проводимости, истоковую область первого типа проводимости и полупроводниковую область второго типа проводимости. Область канала расположена между полупроводниковой областью и поверхностью полупроводниковой подложки. По меньшей мере, часть истоковой области расположена между областью канала и поверхностью. Полупроводниковая область включает в себя первую часть, вторую часть и третью часть. Концентрация примеси первой части ниже, чем концентрация примеси второй части и ниже чем концентрация примеси третьей части. Первая часть расположена между второй частью и третьей частью. Ортогональная проекция первой части на плоскость, параллельную поверхности, накладывается на ортогональную проекцию истоковой области на плоскости.

[0006] Согласно другому аспекту настоящего раскрытия, обеспечена система формирования изображений. Система формирования изображений включает в себя устройство формирования изображений, описанное выше, и блок обработки сигналов, сконфигурированный для обработки сигнала, выведенного из устройства формирования изображений.

[0007] Кроме того, отличительные признаки настоящего раскрытия станут очевидны из последующего описания иллюстративных вариантов осуществления со ссылкой на сопроводительные чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0008] Фиг. 1 изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений.

[0009] Фиг. 2 изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0010] Фиг. 3A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0011] Фиг. 3B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0012] Фиг. 4A-4C изображают графические представления, используемые для объяснения способа производства устройства формирования изображений.

[0013] Фиг. 5A-5B изображают графические представления, схематично иллюстрирующие маски, используемые при производстве устройства формирования изображений.

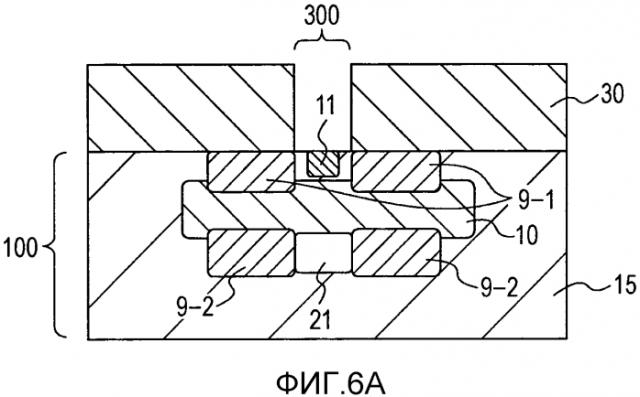

[0014] Фиг. 6A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0015] Фиг. 6B изображает графическое представление, схематично иллюстрирующее маски, используемые при производстве устройства формирования изображений.

[0016] Фиг. 7A изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений.

[0017] Фиг. 7B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений.

[0018] Фиг. 8A-8C изображают графические представления, используемые для объяснения способа производства устройства формирования изображений.

[0019] Фиг. 9 изображает блок схему системы формирования изображений.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0020] Согласно некоторым вариантам осуществления настоящего раскрытия могут быть улучшены характеристики полевого транзистора с p-n-переходом.

[0021] В полевом транзисторе с p-n-переходом, известном изобретателю, часть области затвора расположена или размещена под истоковой областью. Профиль концентрации примеси, или распределение, является однородным. Соответственно, если область затвора имеет высокую концентрацию примеси, то концентрация примеси области под истоковой областью может быть высокой.

[0022] Если концентрация примеси области под истоковой областью является высокой, то ток канала, выводимый из полевого транзистора с p-n-переходом, может варьироваться вследствие обеднения истоковой области. Другими словами, характеристики полевого транзистора с p-n-переходом могут ухудшиться.

[0023] Некоторые варианты осуществления настоящего раскрытия обеспечивают устройство формирования изображений, включающее в себя полевой транзистор с p-n-переходом, где его характеристики могут быть улучшены.

[0024] Вариант осуществления настоящего раскрытия обеспечивает устройство формирования изображений, включающее в себя множество пикселов. Каждый пиксел включает в себя полевой транзистор с p-n-переходом (далее в настоящем документе, называемый транзистором JFET). Транзистор JFET включает в себя область затвора, область канала, стоковая область и истоковую область, сформированные, соответственно, на полупроводниковой подложке. В транзисторе JFET, тип проводимости области затвора отличается от типов проводимости области канала, стоковой области и истоковой области. В настоящем варианте осуществления, в устройстве формирования изображений используется транзистор JFET с горизонтальной структурой, в котором направление тока канала параллельно поверхности полупроводниковой подложки.

[0025] Варианты осуществления согласно настоящему раскрытию представляют собой структуру полупроводниковой области, обеспеченную в более глубоком положении, чем область канала, и/или способ ее производства.

[0026] Далее в настоящем документе, варианты осуществления настоящего раскрытия будут подробно описаны со ссылкой на приложенные чертежи. Настоящее раскрытие не ограничено одним только вариантом осуществления, который будет описан ниже. Кроме того, примеры, в которых частичная конфигурация одного из следующих вариантов осуществления добавлена к другому варианту осуществления или заменена частичной конфигурацией другого варианта осуществления, также являются вариантами осуществления настоящего раскрытия.

[0027] В вариантах осуществления, которые будут описаны, область затвора имеет P-тип, а область канала, стоковая область и истоковая область имеют N-тип. Настоящее раскрытие включает в себя варианты осуществления, где тип проводимости каждой полупроводниковой области является обратным.

ПЕРВЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

[0028] Фиг. 1 изображает графическое представление, схематично иллюстрирующее планарную структуру устройства формирования изображений из настоящего варианта осуществления. Фиг. 1 иллюстрирует один пиксел. Пиксел включает в себя часть фотоэлектрического преобразования, такую, как фотодиод, транзистор переноса, транзистор сброса и транзистор JFET. Устройство формирования изображений из настоящего варианта осуществления включает в себя множество пикселов, иллюстрированных на Фиг. 1.

[0029] В настоящем варианте осуществления, часть фотоэлектрического преобразования является фотодиодом. Фотодиод включает в себя полупроводниковую область 1 N-типа, сформированную на поверхности полупроводниковой подложки, и полупроводниковую область 2 P-типа, сформированную под полупроводниковой областью 1 N-типа. Полупроводниковая область 1 N-типа и полупроводниковая область 2 P-типа формируют P-N-переход. Дырка, сгенерированная посредством падающего света, накапливается в полупроводниковой области 2 P-типа в качестве информационного заряда. Информационный заряд, накопленный в полупроводниковой области 2 P-типа, переносится в плавающую диффузионную область 3 (далее в настоящем документе, называемую областью 3 FD). Область 3 FD является полупроводниковой областью P-типа. Электрод 4 затвора переноса переносит информационный заряд из полупроводниковой области 2 P-типа в область 3 FD.

[0030] Транзистор JFET включает в себя область 9 затвора P-типа, область 10 канала N-типа и истоковую область 11 N-типа. Канал сформирован, по меньшей мере, в части области 10 канала N-типа. Канал управляется посредством напряжения в области 9 затвора. Транзистор JFET из настоящего варианта осуществления включает в себя множество областей 9 затвора. Область 10 канала пересекает каждую из областей 9 затвора, при его рассмотрении в плане. Область 10 канала расположена или размещена таким образом, чтобы пересекать область 9 затвора со стороны истока до стороны стока.

[0031] В настоящей спецификации, при выполнении ссылки на размещение, положения или формы элементов при их рассмотрении в плане, или только в плане, это означает размещение, положения или формы ортогональных проекций элементов, которые вертикально спроецированы на плоскость, параллельную поверхности полупроводниковой подложки. Следовательно, ортогональная проекция области затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекают друг друга на плоскости. Поверхность полупроводниковой подложки определена как граница между полупроводниковой областью и изолятором. Проекция может являться тенью объекта, которая произведена на плоскости во время экспонирования объекта параллельными лучами, которые проходят под прямым углом к плоскости.

[0032] Часть области 10 канала (обозначенная как область 10d на Фиг. 1) формирует стоковая область транзистора JFET. Канал транзистора JFET сформирован в части пересечения между областью 9 затвора и областью 10 канала. Концентрация примеси истоковой области 11 выше, чем концентрация примеси области 10 канала. Истоковая область 11 электрически соединена с выходной линией 14 при помощи контактного штыря 12. Область 3 FD электрически соединена с областью 9 затвора. В вышеописанной конфигурации, транзистор JFET выводит сигнал на основе напряжения области 3 FD.

[0033] МОП (металл-оксид-полупроводник) транзистор сброса включает в себя стоковая область 5 P-типа, истоковую область 7 P-типа и электрод 8 затвора. Стоковая область 5 электрически соединена с проводом 13 сброса напряжения стоковой области при помощи контактного штыря 6. Истоковая область 7 МОП транзистора сброса электрически соединена с областью 9 затвора транзистора JFET. В вышеописанной конфигурации, МОП транзистор сброса сбрасывает напряжение затвора транзистора JFET. Может быть легко использован МОП транзистор для транзистора сброса. Другой тип транзисторов, включая транзистор JFET, может быть использован для транзистора сброса.

[0034] Транзистор JFET включает в себя множество областей 9 затвора, которые являются развернутыми при их рассмотрении в плане. Области 9 затвора расположены или размещены таким образом, чтобы размещать между их слоями истоковую область 11 в плане. Другими словами, ортогональная проекция истоковой области 11 на плоскости, параллельной поверхности полупроводниковой подложки, расположена, в плоскости, между ортогональными проекциями областей 9 затвора на плоскости. Кроме того, транзистор JFET включает в себя множество стоковых областей. Точнее, область 10 канала включает в себя множество частей 10d со стороны стока. Каждая из стоковых областей расположена или размещена на противоположной стороне от истоковой области 10 относительно соответствующей одной из областей 9 затвора. Канал сформирован для каждой из областей 9 затвора. Области 9 затвора могут быть расположены или размещены параллельно друг к другу при их рассмотрении в плане. Области 9 затвора электрически соединены друг с другом посредством полупроводниковой области, имеющей тот же тип проводимости, что и область 9 затвора. В настоящем варианте осуществления, область 3 FD и истоковая область 7 МОП транзистора сброса осуществляют электрическое соединение области 9 затвора друг с другом.

[0035] Согласно вышеописанной конфигурации, может быть расширена эффективная ширина канала транзистора JFET. Другими словами, может быть улучшена запирающая способность вентиля транзистора JFET. Следовательно, устройство формирования изображений может работать с высокой скоростью. Транзистор JFET может включать в себя только одну область затвора. В частности, одна из двух областей 9 затвора, иллюстрированных на Фиг. 1 и соответствующих стоковой области, может быть удалена.

[0036] Пиксел включает в себя полупроводниковую область 21 P-типа. Полупроводниковая область 21 накладывается на истоковую область 11 при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области 21 P-типа на плоскость, параллельную поверхности полупроводниковой подложки, накладывается на ортогональную проекцию истоковой области 11 на плоскость. Полупроводниковая область 21 P-типа расположена или размещена между двумя областями 9 затвора при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области 21 P-типа на плоскость, параллельную поверхности полупроводниковой подложки, расположена между ортогональными проекциями двух областей 9 затвора на плоскость. Полупроводниковая область 22 P-типа накладывается на часть области 10 канала при их рассмотрении в плане. Другими словами, ортогональная проекция полупроводниковой области P-типа на плоскость, параллельную поверхности полупроводниковой подложки, накладывается на часть ортогональной проекции области 10 канала на плоскость.

[0037] Фиг. 2 изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 2 схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1. Элементы на Фиг. 2, соответствующие иллюстрированным на Фиг. 1, обозначены посредством тех же самых ссылочных обозначений, что и на Фиг. 1.

[0038] Фиг. 2 иллюстрирует полупроводниковую подложку 100. Изоляционная пленка, которая не иллюстрирована, обеспечена на полупроводниковой подложке 100. Поверхность SR полупроводниковой подложки 100 определена в качестве границы между полупроводниковой подложкой 100 и изоляционной пленкой, которая не иллюстрирована. Направление длины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 2, так и поверхности SR. Направление глубины полупроводниковой подложки 100 определено как направление, перпендикулярное поверхности SR.

[0039] Фотодиод и транзистор JFET сформированы в полупроводниковой области 15 N-типа. Ток стока (или, ток канала) транзистора JFET обеспечены посредством полупроводниковой области 15 N-типа. Часть для обеспечения тока стока, сконфигурированная для обеспечения тока стока для полупроводниковой области 15 N-типа, сформирована в части области пиксела или за пределами области пиксела. Часть для обеспечения тока стока, например, включает в себя контактный штырь, соединяющий полупроводниковую подложку и электрические провода.

[0040] Под полупроводниковой областью 15 N-типа находится полупроводниковая область 16 N-типа, которая имеет более высокую концентрацию примеси, чем концентрация примеси в полупроводниковой области 15 N-типа. Сопротивление полупроводниковой подложки 100 может быть понижено посредством полупроводниковой области 16 N-типа. Соответственно, может быть возможно понизить падение напряжения вследствие тока стока, обеспеченного для транзистора JFET. Следовательно, может быть возможно уменьшить помехи, такие как темное пятно, которые происходят вследствие изменения напряжения полупроводниковой подложки в зависимости от местоположений. В результате, качество изображения может быть улучшено. В других случаях, ток стока может быть повышен. В результате, устройство формирования изображений может работать с высокой скоростью.

[0041] Часть 10d со стороны стока области 10 канала может быть опущена, и часть полупроводниковой области 15 N-типа может формировать стоковая область. Стоковая область может быть определена как полупроводниковая область N-типа, которая расположена или размещена, в плане, рядом с областью, в которой должен быть сформирован канал.

[0042] Область 9 затвора включает в себя поверхностную область 9-1 затвора и скрытую область 9-2 затвора. Как поверхностная область 9-1 затвора, так и скрытая область 9-2 затвора имеют P-тип. Две поверхностные области 9-1 затвора расположены или размещены в направлении вдоль поверхности SR, две скрытые области 9-2 затвора расположены или размещены в направлении вдоль поверхности SR, поверхностная область 9-1 затвора и скрытая область 9-2 затвора расположены или размещены в направлении глубины. Поверхностная область 9-1 затвора расположена или размещена между поверхностью SR полупроводниковой подложки 100 и скрытой областью 9-2 затвора.

[0043] Область 10 канала расположена или размещена на глубине между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора. Транзистор JFET с горизонтальной структурой сформирован в вышеописанной конфигурации. В транзисторе JFET с горизонтальной структурой направление длины канала параллельно поверхности SR полупроводниковой подложки 100.

[0044] Поверхностная область 9-1 затвора и скрытая область 9-2 затвора электрически соединены друг с другом. Соединительная часть между поверхностной областью 9-1 затвора и скрытой областью 9-2 затвора расположена или размещена таким образом, чтобы не накладываться на область 10 канала при их рассмотрении в плане. Согласно вышеописанной конфигурации, канал транзистора JFET может управляться как посредством поверхностной области 9-1 затвора, так и посредством скрытой области 9-2 затвора.

[0045] Поверхностная область 9-1 затвора и скрытая область 9-2 затвора накладываются друг на друга при их рассмотрении в плане. Другими словами, ортогональная проекция поверхностной области 9-1 затвора на плоскость, параллельную поверхности полупроводниковой подложки, идентична ортогональной проекции скрытой области 9-2 затвора на плоскость. В вышеописанной конфигурации, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы при помощи одной и той же маски, которая является предпочтительной для уменьшения колебаний характеристик транзистора JFET.

[0046] Не требуется, чтобы ортогональная проекция поверхностной области 9-1 затвора была идентична ортогональной проекции скрытой области 9-2 затвора. Например, поверхностная область 9-1 затвора, скрытая область 9-2 затвора и область 10 канала могут быть расположены или размещены таким образом, чтобы поверхностная область 9-1 затвора пересекала область 10 канала в плане, и, при этом, скрытая область 9-2 затвора содержала всю область 10 канала в плане. В вышеописанной конфигурации, поверхностная область 9-1 затвора и скрытая область затвора сформированы при помощи разных масок.

[0047] Либо поверхностная область 9-1 затвора, либо скрытая область 9-2 затвора могут быть опущены. В настоящем варианте осуществления, каждая из областей 9 затвора, которые развернуты при их рассмотрении в плане, включает в себя поверхностную область 9-1 затвора и скрытую область 9-2 затвора. Однако, по меньшей мере, одна из областей 9 затвора, которые развернуты в плане, могут иметь поверхностную область 9-1 затвора или скрытую область 9-2 затвора.

[0048] Как иллюстрировано на Фиг. 2, полупроводниковая область 21 P-типа расположена или размещена между двумя скрытыми областями 9-2 затвора. Полупроводниковая область 21 P-типа расположена или размещена в глубже, чем область 10 канала. Если полупроводниковая область 21 P-типа и область 10 канала сформированы посредством ионных имплантаций, то пик в профиле концентрации примеси, или распределении, вдоль направления глубины полупроводниковой области 21 P-типа расположен в глубже, чем пик в профиле концентрации примеси вдоль направления глубины области 10 канала. Направление глубины определено как направление, перпендикулярное к поверхности SR.

[0049] В настоящем варианте осуществления, вся полупроводниковая область 21 P-типа расположена или размещена на той же самой глубине, что и скрытая область 9-2 затвора. В одном из вариантов осуществления, только часть полупроводниковой области P-типа может быть расположена или размещена на той же самой глубине, что и скрытая область 9-2 затвора

[0050] Концентрация примеси полупроводниковой области 21 P-типа ниже, чем концентрация примеси скрытой области 9-2 затвора. Полупроводниковая область 21 P-типа и скрытая область 9-2 затвора электрически соединены друг с другом. В частности, полупроводниковая область P-типа продолжается в пространственном отношении от полупроводниковой области 21 P-типа до скрытой области 9-2 затвора.

[0051] В качестве изменения настоящего варианта осуществления, может существовать обедненный слой между полупроводниковой областью 21 P-типа и скрытой областью 9-2 затвора. Другими словами, может существовать полупроводниковая область N-типа, обеднение которой происходит между полупроводниковой областью 21 P-типа и скрытой областью 9-2 затвора.

[0052] В конфигурации, где концентрация примеси полупроводниковой области 21 P-типа ниже, чем концентрация примеси скрытой области 9-2 затвора, может быть трудно осуществить обеднение истоковой области 11. В результате, электрическая характеристика транзистора JFET может быть улучшена. Полупроводниковая область 21 P-типа, обеспеченная между двумя скрытыми областями 9-2 затвора, может понизить паразитный ток, который проходит через область между двумя скрытыми областями 9-2 затвора.

[0053] В изменении настоящего варианта осуществления, полупроводниковая область N-типа может быть непрерывно расположена или размещена между двумя скрытыми областями 9-2 затвора, вместо полупроводниковой области 21 P-типа. В вышеописанной конфигурации, могут быть уменьшены колебания электрической характеристики транзистора JFET. Может быть осуществлено обеднение всей полупроводниковой области N-типа, непрерывно расположенного или размещенного между двумя скрытыми областями 9-2 затвора. Другими словами, две скрытые области 9-2 затвора могут быть соединены посредством обедненного слоя. В этой конфигурации, между двумя скрытыми областями 9-2 затвора сформирован, потенциальный барьер, созданный посредством обедненного слоя, который может понизить паразитный ток, проходящий через область между двумя скрытыми областями 9-2 затвора.

[0054] В данном случае будет описан другой аспект структуры в поперечном разрезе, иллюстрированной на Фиг. 2. Полупроводниковая область P-типа, расположенная или размещенная глубже, чем область 10 канала, имеет профиль концентрации примеси, или распределение, который является характерным. Полупроводниковая область P-типа включает в себя первую часть, вторую часть и третью часть. Концентрация примеси второй части и концентрация примеси третьей части соответственно выше, чем концентрация примеси первой части. Первая часть расположена или размещена между второй частью и третьей частью. Полупроводниковая область 21 P-типа может соответствовать первой части. Две скрытые области 9-2 затвора могут соответствовать второй и третьей частям.

[0055] Первая часть накладывается на истоковую область 11 при их рассмотрении в плане. Другими словами, ортогональная проекция первой части на плоскость, параллельная поверхности SR полупроводниковой подложки, накладывается на ортогональную проекцию истоковой области 11 на плоскости. В настоящем варианте осуществления, вторая часть и третья часть не накладываются на истоковую область при их рассмотрении в плане. В другом варианте осуществления, вторая часть и третья часть могут накладываться на истоковую область при их рассмотрении в плане.

[0056] Согласно вышеописанной конфигурации, поскольку концентрация примеси первой части является низкой, может быть сложно осуществить обеднение истоковой области. В результате электрическая характеристика транзистора JFET может быть улучшена.

[0057] Фиг. 3A изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 3 схематично иллюстрирует структуру в поперечном разрезе вдоль линии C-D на Фиг. 1. Элементы Фиг. 3A, соответствующие иллюстрированным на Фиг. 1 и/или на Фиг. 2, определяются посредством тех же самых ссылочных обозначений, что и на Фиг. 1 и/или на Фиг. 2. Направление ширины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 3A, так и поверхности SR.

[0058] Как иллюстрировано на Фиг. 3А, полупроводниковая область 21 P-типа является более широкой, чем область 10 канала в направлении ширины канала. В настоящем варианте осуществления, полупроводниковая область 21 P-типа тянется в пределах, в которых полупроводниковая область 21 P-типа достигает области, находящейся непосредственно под областью 3 FD, и области, находящейся непосредственно под истоковой областью 7 МОП транзистора сброса. Полупроводниковая область 21 P-типа может предотвращать омическую проводимость между областью 10 канала и полупроводниковой областью 15 N-типа. Фактически, профили распределения потенциалов могут быть разработаны таким образом, чтобы электрическое сопротивление, вдоль направления, перпендикулярного к поверхности SR, между областью 10 канала и полупроводниковой областью 15 N-типа, могло быть выше, чем электрическое сопротивление, вдоль направления длины канала, между источником и стоковой областью транзистора JFET.

[0059] Фиг. 3B изображает графическое представление, схематично иллюстрирующее структуру в поперечном разрезе устройства формирования изображений из настоящего варианта осуществления. Фиг. 3B схематично иллюстрирует структуру в поперечном разрезе вдоль линии E-F на Фиг. 1. Элементы Фиг. 3B? соответствующие иллюстрированным в любой из с Фиг. 1 по 3A обозначены посредством тех же самых ссылочных обозначений, что и на с Фиг. 1 по Фиг. 3А. Направление ширины канала определено как направление, которое параллельно как плоскости бумаги на Фиг. 3B, так и поверхности SR.

[0060] Как было упомянуто выше, поверхностная область 9-1 затвора и скрытая область 9-2 затвора электрически соединены друг с другом. В настоящем варианте осуществления, область, имеющая тот же самый тип проводимости, осуществляет электрическое соединение поверхностной области 9-1 затвора и скрытой области 9-2 затвора. Например, на Фиг. 3B, область 3 FD и истоковая область 7 МОП транзистора сброса могут тянуться в направлении глубины полупроводниковой подложки в пределах, в которых они могут осуществлять электрическое соединение поверхностной области 9-1 затвора и скрытой области 9-2 затвора. Несмотря на то что на Фиг. 3 поверхностная область 9-1 затвора и скрытая область 9-2 затвора расположены или размещены на расстоянии друг от друга, поверхностная область 9-1 затвора и скрытая область 9-2 затвора могут быть сформированы, в качестве другого варианта, в непрерывно в пространственном отношении посредством диффузии примеси вдоль направления, перпендикулярного к поверхности SR.

[0061] В настоящем варианте осуществления, область 9 затвора и область 10 канала пересекают друг друга в планарной структуре, иллюстрированной на Фиг. 1. Другими словами, ортогональная проекция области 9 затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области 10 канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекают друг друга.

[0062] Пересечение области 9 затвора и области 10 канала означает, что каждая область расположена или размещена таким образом, чтобы пересекать другую область. Другими словами, по меньшей мере, две части области 9 затвора выступают из области 10 канала и, по меньшей мере, две части области 10 канала выступают из области 9 затвора.

[0063] Часть области канала, которая расположена или размещена между двумя областями 9 затвора при их рассмотрении в плане на Фиг. 1, определена как часть 10s со стороны истока области 10 канала. Часть, в пределах области 10 канала, расположенная или размещенная на противоположной стороне к области 10s со стороны истока относительно области 9 затвора, определена как часть 10d со стороны стока области 10 канала. На Фиг. 2 также указаны часть 10s со стороны истока и часть 10d со стороны стока, соответственно. Каждая из части 10s со стороны истока и части 10d со стороны стока области 10 канала не накладываются на область 9 затвора. Другими словами, часть 10s со стороны истока и часть 10d со стороны стока ортогональной проекции области 10 канала, соответствующим образом выступают из ортогональной проекции области 9 затвора. Соответственно, как иллюстрировано на Фиг. 2, длина канала транзистора JFET ограничена посредством конца области 9 затвора. Как иллюстрировано на Фиг. 3B, ширина канала транзистора JFET ограничена посредством конца области 10 канала.

[0064] В соответствии с вышеописанной конфигурацией, даже при том, что могут иметься ошибки совмещения между маской, используемой для формирования области 9 затвора, и маской, используемой для формирования области 10 канала, форма канала транзистора JFET является фактически устойчивой, или постоянной, или неизменной. Следовательно, колебания длины канала и ширины канала транзистора JFET могут быть уменьшены. В результате, колебания характеристики транзистора JFET могут быть уменьшены.

[0065] Уменьшение колебаний в электрической характеристики транзистора JFET может быть достигнуто независимо от формы области 9 затвора или формы области 10 канала. Уменьшение колебаний может быть получено вследствие структуры, в которой область 9 затвора и область канала пересекают друг друга при их рассмотрении в плане. Периферийная поверхность, в плане, области 9 затвора может включать в себя две параллельные линии вдоль направления ширины канала, как иллюстрировано на Фиг. 1. В этой конфигурации, колебание электрической характеристики может быть дополнительно уменьшено. Периферийная поверхность, в плане, области 10 канала может включать в себя две параллельные линии вдоль направления длины канала, как иллюстрировано на Фиг. 1. В этой конфигурации, колебание электрической характеристики может быть дополнительно уменьшено. Область 9 затвора и/или область 10 канала могут иметь прямоугольные формы, соответственно, для того, чтобы маски, используемые для формирования области 9 затвора и области канала, могли быть упрощены. Периферийные поверхности области 9 затвора и области 10 канала могут включать в себя кривые линии. В этой конфигурации, могут быть уменьшены колебания электрической характеристики транзистора JFET вследствие ошибки совмещения при вращении.

[0066] Длина канала транзистора JFET образована как расстояние между концом со стороны стока и концом со стороны истока области 9 затвора. Часть 10d со стороны стока и часть 10s со стороны истока области 10 канала разделены на обе стороны области 9 затвора при их рассмотрении в плане, что дает в результате уменьшение колебаний характеристик. Другими словами, уменьшение колебаний характеристик может быть получено посредством того, что каждая части 10s со стороны истока и части 10d со стороны стока ортогональной проекции области 10 канала выступают из ортогональной проекции области 9 затвора.

[0067] Далее в настоящем документе, будет объяснен пример способа производства устройства формирования изображений из настоящего варианта осуществления. Фиг. 4A-4C изображают графическое представление, предназначенное для объяснения способа производства устройства формирования изображений из настоящего варианта осуществления. Каждая из Фиг. 4A-4C схематично иллюстрирует структуру в поперечном разрезе вдоль линии A-B на Фиг. 1. Элементы из Фиг. 4A-4C, соответствующие иллюстрированным в любой из с Фиг. 1 по 3B, обозначаются посредством тех же самых ссылочных обозначений, что и с Фиг. 1 по 3B.

[0068] На этапе, иллюстрированном на Фиг. 4A, сформирована область 9 затвора транзистора JFET. На этом этапе используется первая маска 17, которая задает первое окно 209. Первая маска 17, например, получается посредством формирования рисунка в фоторезисте посредством способа фотолитографии.

[0069] Осуществляется легирование примесями, являющимися акцепторами, такими, как бор, полупроводниковой подложки 100 через первое окно 209, в результате чего область 9 затвора формируется в области, соответствующей первому окну