Многоканальный анализатор

Иллюстрации

Показать всеРеферат

259I53

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сава Советских

Социалистических

Республик

Зависимое от авт. свидетельс;ва №

Кл;- 21ат, 37/02 ., С- /

Заявлено 02.1Х.1968 (№ 1267857i18-24) с присоединением заявки №

Приоритет

МПК G 11с

УДК 681.327.02 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Опубликовано 12.Х11.1969. Бюллетень ¹ 2 за 1970

Дата опубликования описания 23.IV.1970

Авторы изобретения

С. С. Курочкин, А. Л. Белоус, А. И. Козырь, К. Ф. Кузнецов и И, И. Рогушин

Заявитель

МНОГОКАНАЛЬНЫЙ АНАЛИЗАТОР

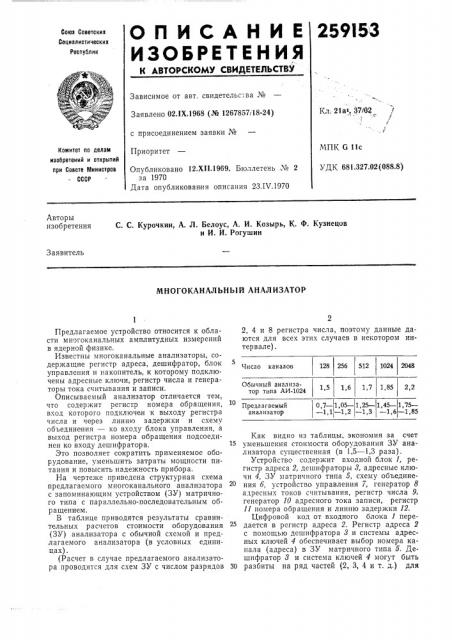

Число каналов

1024 2048

128

256

512

1,5 (Обычный анализатор типа АИ-1024

1,7

1,85 2,2

1,6

Предл агаемый анализатор

1,05— — 1,2

1,45 в 1,75— — 1,6 — 1,85

0,7— — 1,1

1,25— — 1,3

Предлагаемое устройство относится к области многоканальных амплитудных измерений в ядерной физике.

Известны многоканальные анализаторы, содержащие регистр адреса, дешифратор, блок управления и накопитель, к которому подключены адресные ключи, регистр числа и генераторы тока считывания и записи.

Описываемый анализатор отличается тем, что содержит регистр номера обращения, вход которого подключен к выходу, регистра числа и через линию задержки и схему объединения — ко входу блока управления, а выход регистра номера обращения подсоединен ко входу дешифратора.

Это позволяет сократить применяемое оборудование, уменьшить затраты мощности питания и повысить надежность прибора.

На чертеже приведена структурная схема предлагаемого многоканального анализатора с запоминающим устройством (ЗУ) матричного типа с параллельно-последовательным обр а щением.

В таблице приводятся результаты сравнительных расчетов стоимости оборудования (ЗУ) анализатора с обычной схемой и предлагаемого анализатора (в условных единицах) . (Расчет в случае предлагаемого анализатора проводится для схем ЗУ с числом разрядов

2, 4 и 8 регистра числа, поэтому данные даются для всех этих случаев в некотором интервале) .

Как видно из таблицы, экономия за счет

15 уменьшения стоимости оборудования ЗУ анализатора существенная (в 1,5 — 1,3 раза).

Устрочство содержит входной блок 1, регистр адреса 2, дешифраторы 8, адресные ключи 4, ЗУ матричного типа 5, схему объединения б, устройство управления 7, генератор 8 адресных токов считывания, регистр числа 9, генератор 10 адресного тока записи, регистр

11 номера обращения и линию задержки 12.

Цифровой код от входного блока 1 передается в регистр адреса 2. Регистр адреса 2 с помощью дешифратора 8 и системы адресных ключей 4 обеспечивает выбор номера канала (адреса) в ЗУ матричного типа 5. Дешифратор 8 и система ключей 4 могут быть

30 разбиты на ряд частей (2, 3, 4 и т. д.) для

259153

Составитель В. М. Щеглов

Редактор Е. В. Семанова Текред 3. Н. Тараненко Корректоры: В. Петрова и Е. Ласточкина

Заказ 900i8 Тираж 499 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

3 обеспечения привода двух координатных проводов Х и У матричного ЗУ.

Второй сигнал от входного блока 1 через схему объединения б поступает на вход устройства управления 7. При этом в определенной последовательности с выходов устройства управления 7 следуют импульсы на запуск Ieнератора 8 адресного тока считывания (операция а); на добавление единицы в регистр числа 9 (операция б); на запуск генератора 10 адресного тока записи (операция в). В результате этого обеспечивается выемка числа из выбранного канала ЗУ в регистр числа 9, добавление единицы к нему и запись измененного числа обратно в тот же канал, Так как в предлагаемом устройстве регистр числа имеет уменьшенное число разрядов

lг (n, где n — число разрядов хранимого числа, то при операции а считывается не все число, а только часть его. Если при операции б регистр числа не переполняется, то производится операция в. Однако, если при операции б регистр числа переполняется, то импульс переполнения добавляет единицу в регистр 11 номера обращения, а также, пройдя линию задержки 12, запускает вновь устройство управления 7, Так как выходы регистра 11 номера обращения подключены к части дешифратора

8, то при этом выбирается следующая по старшинству группа разрядов того же канала.

Далее повторяются операции а и б. Если регистр числа 9 при этом не переполняется, то цикл регистрации заканчивается операцией в.

Если регистр числа 9 переполнится вновь, выбирается следующая по старшинству группа разрядов того же канала и т. д. Процесс про10 текает до тех пор, пока при операции б регистр числа 9 не переполнится, или прсисходит обращение к самой старшей группе разрядов выбранного канала.

15 Предмет изобретения

Многоканальный анализатор, содержащий регистр адреса, дешифратор, блок управления и накопитель, к которому подключены адресные ключи, регистр числа и генераторы тока

20 считывания и записи, отличающийся тем, что, с целью упрощения анализатора, он содержит регистр номера обращения, вход которого подключен к выходу регистра числа и через линию задержки и схему объединения — ко

25 входу блока управления, а выход регистра номера обращения подсоединен ко входу дешифратора.