Генератор опорного напряжения с низким импедансом

Иллюстрации

Показать всеУстройство и система генератора опорного напряжения с низким импедансом. Устройство содержит: контур регулирования напряжения, включающий в себя первый транзистор для обеспечения выходного напряжения, и контур регулирования тока для определения тока через первый транзистор относительно опорного тока. Технический результат - обеспечение опорных напряжений с низким импедансом при низком энергопотреблении. 3 н. и 18 з.п. ф-лы, 5 ил.

Реферат

Уровень техники

Цепи, обеспечивающие опорные напряжения с низким импедансом, обладают высоким энергопотреблением. Например, при напряжении питания 1 В обычные генераторы опорного напряжения с низким импедансом могут потреблять более 5 мА для обеспечения опорного напряжения с низким импедансом. Современные компьютеры и аналоговые цепи функционируют при низких напряжениях питания, при этом предпочтительно, чтобы они обладали низким энергопотреблением и размером, что является сложной задачей при использовании обычных генераторов опорного напряжения с низким импедансом.

Краткое описание чертежей

Варианты осуществления изобретения будут более понятны из подробного описания, приведенного ниже, и из сопровождающих чертежей различных вариантов осуществления изобретения, которые, тем не менее, не ограничивают изобретение определенными вариантами осуществления, а приведены только для объяснения и лучшего понимания.

На фиг. 1 показана схема генератора опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения.

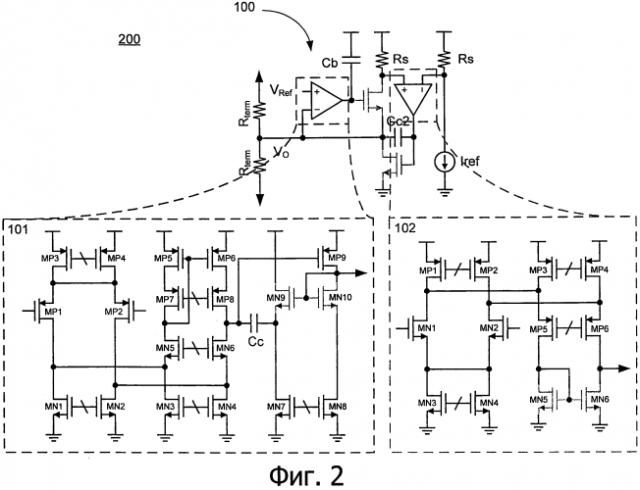

На фиг. 2 показана принципиальная схема, показывающая подробности цепи, изображенной на фиг. 1 в соответствии с одним вариантом осуществления изобретения.

На фиг. 3 показана система ввода-вывода (I/O), использующая генератор опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения.

На фиг. 4 показана схема генератора опорного напряжения с низким импедансом в соответствии с другим вариантом осуществления изобретения.

На фиг. 5 показана диаграмма системного уровня интеллектуального устройства, содержащего процессор с генератором опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения.

Подробное описание изобретения

Обеспечение опорных напряжений с низким импедансом при низком энергопотреблении является хорошо известной задачей. Приведенные в этом документе варианты осуществления относятся к устройству и системе генератора опорного напряжения с низким импедансом, который по существу потребляет меньше энергии по сравнению с обычными опорными генераторами.

Описанные в этом документе варианты осуществления используют активную межэлектродную проводимость выходных транзисторов для достижения низкого выходного импеданса. В одном варианте осуществления при высоком отношении активной межэлектродной проводимости к току (gm:Id) в выходных транзисторах опорного генератора с низким импедансом снижается ток покоя по сравнению с обычными генераторами напряжения. Высокое отношение gm:Id составляет примерно 15:1 для n-канальных или р-канальных металл-оксидных полупроводниковых (NMOS/PMOS) устройств, а низкое отношение gm:Id составляет примерно 6:1. Отношение gm:Id для биполярных плоскостных транзисторов (BJT) при комнатной температуре составляет примерно 40:1

В вариантах осуществления, обсуждаемых в этом документе, для обеспечения опорного напряжения с низким импедансом в дополнение к контуру регулирования напряжения применяют контур токочувствительности и контур регулирования тока. Контур регулирования тока, обсуждаемый в этом документе, фиксирует ток покоя посредством выходных транзисторов, отделяя их от значения смещающего напряжения. В вариантах осуществления, обсуждаемых в этом документе, в контуре регулирования тока применяют транзисторы с общим истоком (или общим эмиттером), чтобы предотвратить проблемы, связанные с ограниченным диапазоном выхода, встречающиеся в обычных топологиях схемы опорного напряжения с двухтактным истоковым повторителем (эмиттерным повторителем), получая широкий выходной диапазон напряжений. Например, для цепи, обсуждаемой в этом документе, выходной диапазон напряжений составляет примерно 600 мВ, если она сконструирована для работы с напряжением питания, равным 1 В. В отличие от этого, выходной диапазон напряжений двухтактного каскада, предназначенного для работы с напряжением питания, равным 1 В, составляет примерно 300 мВ. Транзистор с общим истоком, обсуждаемый в этом документе, также предоставляет средство для управления/регулирования тока покоя.

В одном варианте осуществления устройство содержит: контур регулирования напряжения, включающий в себя первый транзистор, предназначенный для обеспечения выходного напряжения; и контур регулирования тока, предназначенный для определения тока через первый транзистор относительно опорного тока. В одном варианте осуществления контур регулирования тока содержит второй транзистор, последовательно соединенный с первым транзистором, причем второй транзистор предназначен для обеспечения постоянного тока через первый и второй транзисторы.

В одном варианте осуществления устройство содержит первый конденсатор с первым контактным выводом, соединенный с выходом второго усилителя контура регулирования тока и входом второго транзистора, и со вторым контактным выводом, соединенным с контактом первого транзистора и второго транзистора. В одном варианте осуществления устройство дополнительно содержит: второй конденсатор, первый контактный вывод которого соединен с выходом первого усилителя контура регулирования напряжения, а второй контактный вывод соединен с контактом питания или землей. В одном варианте осуществления первый транзистор является истоковым повторителем (или эмиттерным повторителем), а второй транзистор является транзистором с общим истоком (или с общим эмиттером).

В одном варианте осуществления первый усилитель может использоваться, чтобы обеспечить выходное напряжение относительно опорного напряжения с помощью первого транзистора, соединенного с первым усилителем. В одном варианте осуществления второй усилитель может использоваться, чтобы выработать входной сигнал для второго транзистора, соединенного последовательно с первым транзистором, причем второй транзистор предназначен для того, чтобы обеспечить постоянный ток через первый и второй транзисторы относительно опорного тока.

В одном варианте осуществления первый конденсатор первым контактным выводом соединен с выходом второго усилителя и входом второго транзистора. В одном варианте осуществления второй контактный вывод первого конденсатора соединен с контактом первого транзистора и контактом второго транзистора, причем второй контактный вывод первого конденсатора соединен с входом первого усилителя, при этом второй контактный вывод первого конденсатора обеспечивает опорное напряжение. В одном варианте осуществления первый контактный вывод второго конденсатора соединен с выходом первого усилителя и входом первого транзистора, причем второй контактный вывод второго конденсатора соединен с контактом питания или землей.

В одном варианте осуществления устройство дополнительно содержит: первый резистор, первый контактный вывод которого соединен с первым входом второго усилителя и контактом первого транзистора. В одном варианте осуществления устройство дополнительно содержит: второй резистор, первый контактный вывод которого соединен со вторым входом второго усилителя и с генератором опорного тока, который обеспечивает опорный ток.

В одном варианте осуществления система содержит: процессор с опорным генератором в соответствии с устройством, описанным в этом документе; и антенну беспроводной связи, предназначенную для соединения процессора с беспроводной сетью. В одном варианте осуществления опорный генератор предназначен для обеспечения, по меньшей мере, одного из следующего: синфазного напряжения на резисторах оконечной нагрузки приемника ввода-вывода (I/O), опорного напряжения для I/O передатчика или опорного напряжения для аналоговой цепи. В одном варианте осуществления I/O приемник представляет собой I/O приемник PCIe в соответствии со спецификацией, описанной в базовой спецификации разъема взаимодействия периферийных компонент типа экспресс (PCIe), например, в базовой спецификации разъема взаимодействия периферийных компонент типа экспресс (PCIe), редакция 3.0, версия 0.9, 10.08.2010. В одном варианте осуществления система дополнительно содержит дисплей, представляющий собой сенсорный дисплей.

Обсуждаемые в этом документе варианты осуществления обладают множеством технических эффектов. Например, варианты осуществления генератора опорного напряжения с низким импедансом, обсуждаемые в этом документе, обеспечивают обратные потери синфазного режима (СМ), равные - 6 дБ относительно нуля в диапазоне частот 4 ГГц, и - 3 дБ в диапазоне частот свыше 4 ГГц. Опорный генератор с низким импедансом, обсуждаемый в этом документе, обеспечивает опорное напряжение с низким импедансом при энергопотреблении, составляющем менее половины энергопотребления обычных генераторов опорного напряжения с низким импедансом.

Например, опорный генератор с низким импедансом, обсуждаемый в этом документе, потребляет 2 мА по сравнению с более чем 5 мА, потребляемыми обычными генераторами опорного напряжения с низким импедансом. То, что генератор опорного напряжения с низким импедансом, обсуждаемый в этом документе, обеспечивает широкий выходной диапазон напряжений и неизменное постоянное энергопотребление при функционировании, температуру и колебания напряжения питания (PVT), а также различные выходные напряжения, увеличивает возможность его многократного использования в аналоговых схемах общего назначения. Варианты осуществления, обсуждаемые в этом документе, предполагают и другие технические эффекты.

В последующем описании обсуждают множество подробностей, чтобы дать более полное объяснение вариантов осуществления настоящего изобретения. Тем не менее, специалистам в области техники будет очевидно, что варианты осуществления настоящего изобретения могут быть реализованы на практике без этих специфических подробностей. В других случаях широко известные структуры и устройства показаны в виде структурной схемы, а не подробно, чтобы варианты осуществления настоящего изобретения были более понятными.

Отметим, что на соответствующих чертежах вариантов осуществления сигналы представлены в виде линий. Некоторые линии могут быть более толстыми, чтобы показать более существенные пути прохождения сигнала, и/или могут иметь на одном или нескольких концах стрелки, показывающие основное направление потока информации. Такие обозначения не следует понимать как ограничивающие. Наоборот, линии используют применительно к одному или нескольким примерам осуществления, чтобы упростить понимание схемы или логического блока. Любой представленный сигнал, в соответствии с потребностями проектирования или предпочтениями, может в действительности содержать один или несколько сигналов, которые могут проходить в любом направлении и могут быть реализованы посредством сигнальной схемы любого подходящего типа.

Всюду далее в описании и в формуле изобретения термин "соединенный" означает непосредственное электрическое соединение между соединяемыми элементами, без каких-либо промежуточных устройств. Термин "связанный" означает либо непосредственное электрическое соединение между соединяемыми элементами, либо опосредованное соединения через одно или несколько пассивных или активных промежуточных устройств. Термин "цепь" означает один или несколько пассивных и/или активных компонентов, установленных так, чтобы взаимодействовать друг с другом для обеспечения желаемой функции. Термин "сигнал" означает, по меньшей мере, один из следующих сигналов: токовый сигнал, сигнал напряжения или информационный сигнал. Использование форм единственного числа включает в себя множественное число. Значение "в" включает в себя "в" и "на".

В этом документе, если не указано иное, использование порядковых числительных "первый", "второй" и "третий" и т.д. для описания одного объекта, просто указывает на то, что ссылаются на различные экземпляры одинаковых объектов, и не предполагается, что описываемые таким образом объекты должны следователь в заданном порядке во времени, в пространстве, в иерархии или как-либо иначе. Термин "по существу" в этом документе означает в пределах 10% от намеченного.

В описанных в этом документе вариантах осуществления транзисторы представляют собой металл-оксидные полупроводниковые (МОП) транзисторы, которые включают в себя сток, исток, затвор и выводные контакты. Электроды истока и стока являются идентичными контактами и используются в этом документе взаимозаменяемо. Специалистам в области техники понятно, что, не отклоняясь от объема изобретения, можно использовать другие транзисторы (биполярные плоскостные транзисторы - BJT PNP/NPN, BiCMOS, CMOS, eFET и т.д.). Выражение "MN" в этом документе обозначает транзистор n-типа (напр., NMOS, NPN BJT и т.д.), a "MP" обозначает транзисторы р-типа (напр., PMOS, PNP BJT и т.д.).

На фиг. 1 показана схема генератора 100 опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом содержит: контур регулирования напряжения, включающий в себя первый транзистор MN1 для обеспечения выходного напряжения на выводном контакте Vo. Контур регулирования напряжения показан замкнутой цепью, образованной из первого усилителя 101, первого транзистора MN1 и контактного вывода выходного напряжения Vo. В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом дополнительно содержит контур регулирования тока, предназначенный для определения тока через первый транзистор MN1 относительно опорного тока Iref. В одном варианте осуществления контур регулирования тока содержит второй транзистор MN2, последовательно соединенный с первым транзистором MN1, причем второй транзистор MN2 предназначен для обеспечения постоянного тока через первый и второй транзисторы (MN1 и MN2 соответственно). Контур регулирования тока показан замкнутой цепью, образованной из второго усилителя 102, второго транзистора MN2 и контактного вывода напряжения Vo.

В одном варианте осуществления первый транзистор MN1 является истоковым повторителем или эмиттерным повторителем, в то время как второй транзистор MN2 является транзистором с общим истоком или с общим эмиттером. Первый и второй усилители 101 и 102 соответственно представляют собой однокаскадные или многокаскадные операционные усилители (ОРАМР). В одном варианте осуществления первый и второй усилители 101 и 102 минимизируют разность напряжений между Vo и Vref, и разность напряжений между контактами 104 и 106 соответственно. В одном варианте осуществления транзисторы первого и второго усилителей соответствуют друг другу, чтобы компенсировать систематические погрешности, вызванные колебаниями процесса, температуры и напряжения (PVT).

В одном варианте осуществления генератор опорного напряжения с низким импедансом содержит первый конденсатор Сс2 с первым контактным выводом 103, соединенным с выходом второго усилителя 102 контура регулирования тока. В этом варианте осуществления первый контактный вывод 103 первого конденсатора Сс2 также соединен с входом второго транзистора MN2. Вход второго транзистора MN2 представляет собой вывод затвора, если второй транзистор MN2 является NMOS-транзистором. Аналогично, вход второго транзистора MN2 представляет собой вывод базы, если второй транзистор MN2 является NPN BJT-транзистором.

В одном варианте осуществления второй контактный вывод Vo первого конденсатора Сс2 соединен с выводом первого транзистора MN1. В этом варианте осуществления вывод первого транзистора MN1, который соединен со вторым контактным выводом первого конденсатора Сс2, представляет собой электрод истока (если MN1 является NMOS-транзистором) или электрод эмиттера (если MN1 является NPN BJT-транзистором).

В одном варианте осуществления второй контакт (соединенный с выходным контактным выводом Vo) первого конденсатора Сс2 также соединен с выводом второго транзистора. В этом варианте осуществления вывод второго транзистора MN2, который соединен со вторым контактным выводом первого конденсатора Сс2, представляет собой электрод стока (если MN2 является NMOS-транзистором) или электрод коллектора (если MN2 является NPN BJT-транзистором). В одном варианте осуществления второй контактный вывод (соединенный с выходным контактным выводом Vo) первого конденсатора Сс2 соединен с входом первого усилителя 101, причем второй контактный вывод (соединенный с выходным контактным выводом Vo) обеспечивает выходное опорное напряжение с низким импедансом. В этом варианте осуществления вход первого усилителя 101, который соединен с выходным контактным выводом Vo, является отрицательным входом первого усилителя 101, в то время как опорное напряжение Vref соединено с положительным контактом первого усилителя 101. В одном варианте осуществления первый конденсатор Сс2 обладает емкостью от 500 фФ до 1 пФ.

В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом дополнительно содержит: второй конденсатор Cb, первый контактный вывод 107 которого соединен с выходом первого усилителя MN1 контура регулирования напряжения, а второй контактный вывод соединен с контактом Vcc питания (или землей в случае фиг. 4). Ссылаясь снова на фиг. 1, в одном варианте осуществления первый контактный вывод 107 второго конденсатора Cb соединен с входом первого транзистора MN1. Вход первого транзистора MN1 представляет собой вывод затвора, если первый транзистор MN1 является NMOS-транзистором. Аналогично, вход первого транзистора MN1 представляет собой вывод базы, если первый транзистор MN1 является NPN BJT-транзистором. В одном варианте осуществления емкость второго конденсатора Cb равна примерно 1 пФ.

В одном варианте осуществления первый усилитель 101 может применяться, чтобы обеспечить выходное напряжение Vo (также именуемое выходным контактным выводом Vo) относительно опорного напряжения Vref посредством первого транзистора MN1, соединенного с первым усилителем 101. В одном варианте осуществления опорное напряжение Vref может быть получено с помощью любого известного источника. Например, Vref может быть получено посредством схемы бандгапа, делителя напряжения и т.д. Хотя диапазон значений Vref зависит от приложения, при работе с напряжением питания, равным IB, Vref обычно имеет значение из диапазона от 50 мВ до 650 мВ.

В одном варианте осуществления второй усилитель 102 может использоваться, чтобы обеспечить протекание постоянного тока через первый транзистор MN1 относительно опорного тока Iref. В одном варианте осуществления Iref вырабатывают с помощью любого известного генератора опорного тока. В одном варианте осуществления второй усилитель может использоваться, чтобы выработать входной сигнал 103 для второго транзистора MN2, последовательно соединенного с первым транзистором MN1, причем второй транзистор MN2 предназначен для обеспечения постоянного тока через первый и второй транзисторы MN1 и MN2 соответственно.

В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом дополнительно содержит первый резистор 108, включающий в себя первый контактный вывод 104, соединенный с первым входом второго усилителя 102 и контактом первого транзистора MN1. В этом варианте осуществления вывод первого транзистора MN1, который соединен с первым резистором 108, представляет собой электрод 104 стока MN1 (или электрод коллектора, если MN1 является BJT). В одном варианте осуществления первый вход второго усилителя 102, который соединен с выводом первого транзистора MN1, представляет собой положительный вывод второго усилителя 102.

В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом дополнительно содержит второй резистор 109, включающий в себя первый контактный вывод 106, соединенный со вторым входом второго усилителя 102 и с генератором опорного тока Iref, который обеспечивает опорный ток. В этом варианте осуществления второй вход второго усилителя 102 представляет собой отрицательный вывод второго усилителя 102. В одном варианте осуществления второй резистор 109 имеет сопротивление NRs, кратное первому сопротивлению Rs (первого резистора 108), где "N" - целое число. В других вариантах осуществления "N" является дробью.

Хотя в представленных вариантах осуществления первый резистор 108 и второй резистор 109 показаны в виде дискретного пассивного резистора, первый резистор 108 и второй резистор 109 могут представлять собой активные устройства. В одном варианте осуществления первый резистор 108 и второй резистор 109 выполнены в виде переключающих полевых транзисторов р-типа, подключенных параллельно с транзисторами n-типа. В одном варианте осуществления первый резистор 108 и второй резистор 109 выполнены в виде транзисторов n-типа. В одном варианте осуществления первый резистор 108 и второй резистор 109 выполнены в виде транзисторов р-типа. В одном варианте осуществления транзисторы n-типа и р-типа, образующие первый резистор 108 и второй резистор 109, обладают программируемым сопротивлением, т.е. транзисторы n-типа и р-типа могут быть включены или выключены в любом сочетании, чтобы обеспечить желаемое сопротивление. В одном варианте осуществления первый резистор 108 и второй резистор 109 обладают сопротивлением, равным 150 Ом.

В вариантах осуществления, обсуждаемых в этом документе, первый резистор 108 и второй резистор 109 являются согласованными резисторами. Термин "согласованные" в этом документе относится к идентичной конфигурации резисторов, включая кратное целое идентичных конфигураций, что выражается в том, что вольт-амперные характеристики одного устройства являются фиксированными кратными характеристик другого устройства. Например, второй резистор 109 имеет сопротивление, которое является долей или кратным сопротивления первого резистора 108.

В одном варианте осуществления выходной контактный вывод Vo обеспечивает обратные потери синфазного режима в соответствии со спецификацией PCIe на оконечной нагрузке 105, как показано на фиг. 1. В других вариантах осуществления выходной контактный вывод Vo может быть использован для обеспечения опорного напряжения на других цепях. Например, выходной контактный вывод Vo может быть использован для обеспечения опорного напряжения на цепи передатчика. В качестве другого примера, выходной контактный вывод Vo также может быть использован для снижения переходной помехи на линии напряжения смещения.

В одном варианте осуществления сигнал смещения с низким импедансом вырабатывают на выходном контактном выводе Vo, устанавливая ток покоя через транзистор MN1 истокового повторителя (или эмиттерного повторителя), а также устанавливая напряжение на затворном выводе (или базе) транзистора MN1 истокового повторителя (или эмиттерного повторителя). В таком варианте осуществления контур регулирования напряжения, образованный первым усилителем 101 в отрицательной обратной связи, сравнивает напряжение на истоке (контактном выводе Vo) транзистора MN1 истокового повторителя с опорным напряжением Vref. В этом варианте осуществления первый усилитель 101 усиливает разность между напряжением на истоке (контактном выводе Vo) и опорным напряжением Vref. В одном варианте осуществления первый усилитель 101 управляет выводом затвора транзистора MN1 истокового повторителя, так, чтобы минимизировать (напр., в пределах 10 мВ) разницу между выходным напряжением Vo и опорным напряжением Vref. В одном варианте осуществления разница между выходным напряжением Vo и опорным напряжением Vref минимизируют до нуля.

В одном варианте осуществления, в то время как контур регулирования напряжения минимизирует разницу (напр., доводя ее до значений в пределах 10 мВ) между выходным напряжением на контактном выводе Vo и опорным напряжением Vref, одновременно функционирует контур регулирования тока. В одном варианте осуществления ток покоя через транзистор MN1 истокового повторителя определяют через первый резистор 108 посредством второго усилителя 102.

В таком варианте осуществления второй усилитель 102 сравнивает ток через первый резистор 108 с опорным током Iref, который протекает через соответствующий второй резистор 109. В этом варианте осуществления разница между токами через первый резистор 108 и кратным опорного тока Iref усиливают посредством второго усилителя 102. В одном варианте осуществления второй усилитель 102 используют, чтобы управлять выводом затвора (или базы) транзистора MN2 с общим истоком (или с общим эмиттером) так, чтобы минимизировать разницу между кратным опорного тока Iref и током покоя и транзистора MN1 истокового повторителя, и транзистора MN2 с общим истоком. В этом варианте осуществления контур регулирования напряжения и контур регулирования тока фиксируют и выходное напряжение на контактном выводе Vo, и ток покоя через первый и второй транзисторы MN1 и MN2 соответственно. Как объясняется в этом документе, контур регулирования напряжения и контур регулирования тока снижают импеданс сигнала смещения на контактном выводе V0 на всех частотах.

В одном варианте осуществления на низких частотах низкого импеданса на контактном выводе Vo достигают посредством одновременной работы и контура обратной связи регулирования напряжения, и контура обратной связи регулирования тока. Выражение "низкие частоты" в этом документе относится к частотам менее 100 МГц или к частотам, на которых конденсаторы Cb и Сс2 являются функционально электрически разомкнутыми.

Например, если напряжение на контактном выводе Vo сигнала смещения снижают, то отрицательная обратная связь через контур регулирования напряжения приводит к увеличению напряжения затвора (или базы) на контактном выводе 107 транзистора MN1 истокового повторителя (или эмиттерного повторителя). По мере того, как напряжение затвора (или базы) на контактном выводе 107 транзистора MN1 первого транзистора) истокового повторителя или эмиттерного повторителя) возрастает, транзистор MN1 истокового повторителя выдает больше тока, чтобы противодействовать снижению напряжения на контактном выводе Vo сигнала смещения. В то же время, увеличение тока через транзистор MN1 истокового повторителя (или эмиттерного повторителя) определяют посредством контура регулирования тока, что приводит к тому, что транзистор MN2 (второй транзистор) с общим истоком (или с общим эмиттером) пропускает меньше тока. В этом варианте осуществления контур регулирования тока также противодействует снижению напряжения на контактном выводе Vo сигнала смещения. Увеличение напряжения на контактном выводе Vo сигнала смещения вызывает аналогичный эффект и в контуре регулирования напряжения, и в контуре регулирования тока.

На средних и высоких частотах первый конденсатор Сс2 (также называемый пропускающим конденсатором) и второй конденсатор Cb (также называемый развязывающим конденсатором) закорачиваются, приводя к снижению коэффициента усиления через первый и второй усилители 101 и 102 соответственно. Если второй конденсатор Сс2 закорачивают, то на контактном выводе Vo обеспечивают импеданс 1/gm, рассматривая вывод истока (или эмиттера) первого транзистора MN1, и обеспечивают импеданс 1/gm, рассматривая сток второго транзистора MN2, где gm - активная межэлектродная проводимость первого и второго транзисторов MN1 и MN2 соответственно. Это приводит к тому, что импеданс на контактном выводе Vo пропорционален 1/gm, рассматривая цепь 100.

Выражение "средние и высокие частоты" в этом документе относится к частотам более 100 МГц или к частотам, на которых конденсаторы Cb и Сс2 являются функционально электрически закороченными.

Например, если напряжение на контактном выводе Vo сигнала смещения уменьшается, то транзистор MN1 истокового повторителя выдает больше тока. В то же время, напряжение затвора на контактном выводе 103 транзистора MN2 с общим истоком уменьшается, приводя, тем самым, к тому, что транзистор MN2 пропускает меньше тока. Оба этих действия противодействуют снижению напряжения сигнала смещения на контактном выводе Vo. Увеличение напряжения на контактном выводе Vo сигнала смещения вызывает аналогичный эффект в первом и втором транзисторах MN1 и MN2 соответственно.

На фиг. 2 показана принципиальная схема цепи 100, изображенной на фиг. 1 в соответствии с одним вариантом осуществления изобретения. На фиг. 2 приведены подробности цепей усилителей, которые могут быть использованы соответственно для первого и второго усилителей 101 и 102 в соответствии с одним вариантом осуществления изобретения. В других вариантах осуществления без изменения сущности вариантов осуществления изобретения могут быть использованы другие цепи для первого и второго усилителей 101 и 102. Чтобы не усложнять описание вариантов осуществления изобретения, функционирование конструкций первого и второго усилителей не обсуждается. Косые черты на затворах транзисторов (напр., косые черты на затворах транзисторов MN3 и MN4) показывают, что затвор транзистора присоединен к соответствующей цепи смещения. Чтобы не усложнять описание вариантов осуществления изобретения, цепи смещения не показаны.

В одном варианте осуществления первый усилитель 101 выполнен в виде дифференциального усилителя р-типа с входными транзисторами МР1 и МР2. Одна из причин выбора дифференциального усилителя р-типа с входными транзисторами МР1 и МР2 заключается в том, чтобы компенсировать низкое входное синфазное напряжение первого усилителя 101, которое является результатом требования низкого выходного напряжения Vo и Vref. В одном варианте осуществления транзисторы MN9 и MN10 n-типа первого усилителя 101 согласованы с транзистором MN1 истокового повторителя (или эмиттерного повторителя) (см. фиг. 1) и с транзистором MN2 с общим истоком (или общим эмиттером) (см. фиг. 1) основной выходной ветви. Транзисторы MP3 и МР4 первого усилителя 101 обеспечивают источник тока для входной пары транзисторов МР1 и МР2, в то время как транзисторы MN1 и MN2 обеспечивают активные нагрузки для входной пары транзисторов МР1 и МР2.

Транзисторы MN3, MN4, MN5, MN6, МР7, МР8, МР5 и МР6 образуют остальную часть первого каскада первого усилителя 101, который в этом варианте осуществления представляет собой свернутый каскодный каскад. Транзисторы MN8, MN10 и МР9 образуют второй усилительный каскад в усилителе 101, который обеспечивает дополнительное усиление для усилителя, устанавливает корректное напряжение смещения для первого транзистора MN1 (см. фиг. 1) основной выходной ветви, и отсоединяет напряжение затвора первого транзистора MN1 (см. фиг. 1) от выходного напряжения покоя первого каскада усилителя 101. В одном варианте осуществления плотность тока смещения транзистора во втором каскаде усилителя 101 - транзистора MN10 первого усилителя 101 - согласована с плотностью тока через транзисторы MN1 (см. фиг. 1) и MN2 (см. фиг. 1) основной выходной ветви. Конденсатор Сс представляет собой компенсирующий конденсатор первого усилителя 101. Транзисторы MN9 и MN7 образуют истоковый повторитель обратной связи для предотвращения прямой связи через Сс.

В одном варианте осуществления второй усилитель 102 выполнен в виде дифференциального усилителя n-типа с входными транзисторами MN1 и MN2. Одна из причин выбора дифференциального усилителя n-типа с входными транзисторами MN1 и MN2 заключается в высоком входном синфазном напряжении усилителя 102, которое является результатом малого падения напряжения на первом резисторе 108 и втором резисторе 109 между источником питания и входами второго усилителя 102. В одном варианте осуществления транзисторы MN5 и MN6 второго усилителя 102 согласованы с транзистором MN1 истокового повторителя (первым транзистором на фиг. 1) и с транзистором MN2 с общим истоком (вторым транзистором на фиг. 1), тем самым минимизируя воздействие изменений параметров процесса. Транзисторы MN3 и MN4 второго усилителя 102 обеспечивают источник тока на входную пару транзисторов MN1 и MN2, в то время как транзисторы МР1, МР2, MP3 и МР4 обеспечивают высокий импеданс на выводах стока первого и второго транзисторов MN1 и MN2 (см. фиг. 1), что приводит к прохождению тока сигнала через каскодные устройства МР5 и МР6. Транзисторы MP3 и МР6 образуют каскодные устройства, которые смещают уровень высоких напряжений покоя на выводах стока входных устройств MN1 и MN2 до низких напряжений покоя, необходимых на стоках устройств MN5 и MN6.

На фиг. 3 показана система 300 ввода-вывода (I/O), использующая генератор 100 опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления система 300 включает в себя процессор 301, связанный с процессором 303 через дифференциальную среду 304 передачи. В одном варианте осуществления среда 304 передачи представляет собой одностороннюю среду передачи. В одном варианте осуществления генератор 100 опорного напряжения с низким импедансом используют для обеспечения опорного напряжения с низким импедансом для I/О-передатчика 302. В одном варианте осуществления генератор 100/307 опорного напряжения с низким импедансом соединен с приемником 306, чтобы обеспечить опорное напряжение синфазного режима (СМ) с низким импедансом при обратных потерях СМ - 6 дБ на частоте от 0 до 4 ГГц и при обратных потерях СМ - 3 дБ на частоте свыше 4 ГГц. В таком варианте осуществления выходной контактный вывод Vo соединен с сопротивлениями оконечной нагрузки, как показано на фиг. 1, причем выходной контактный вывод также соединен с контактной площадкой 305 I/O и приемником 306. В других вариантах осуществления опорный генератор 100 с низким импедансом может быть использован для любой цепи, в которой требуется опорное напряжение с низким импедансом.

На фиг. 4 показана схема генератора 400 опорного напряжения с низким импедансом в соответствии с другим вариантом осуществления изобретения. Вариант осуществления, приведенный на фиг. 4, аналогичен варианту осуществления, показанному на фиг. 1, за исключением того, что конструкция перевернута. На фиг. 4 показана реализация р-типа генератора 100 опорного напряжения с низким импедансом на основе электропроводности n-типа, приведенного на фиг. 1.

В этом варианте осуществления первый транзистор MN1 (истоковый повторитель n-типа) на фиг. 1 заменили на транзистор МР1 р-типа истокового повторителя (или эмиттерного повторителя), в то время как второй транзистор MN2 n-типа (транзистор n-типа с общим эмиттером) на фиг. 1 заменили на транзистор МР2 р-типа с общим истоком (или общим эмиттером). В одном варианте осуществления первый усилитель 401 реализован дифференциальной входной парой транзисторов n-типа, а второй усилитель 402 реализован дифференциальной входной парой транзисторов р-типа.

В этом варианте осуществления первый конденсатор Сс2 подключен, как и первый конденсатор Сс2 на фиг. 1. В одном варианте осуществления первый контактный вывод второго конденсатора Cb соединен с выходом первого усилителя 401, в то время как второй контактный вывод второго конденсатора Cb соединен с контактом питания или землей. Первый резистор 408 и второй резистор 409 в этом варианте осуществления подключены между землей и входными контактными выводами второго усилителя 402. В одном варианте осуществления первый резистор 408 и второй резистор 409, как показано, выполнены в виде проходных транзисторов. В других вариантах осуществления могут быть использованы другие виды линейных резисторов. Вариант осуществления, показанный на фиг. 4, обеспечивает более высокое опорное напряжение, чем опорное напряжение, достигаемое в варианте осуществления, приведенном на фиг. 1

На фиг. 5 показана диаграмма системного уровня интеллектуального устройства 1600, содержащего процессор с генератором 100/400 опорного напряжения с низким импедансом в соответствии с одним вариантом осуществления изобретения. На фиг. 5 также показана блок-схема варианта осуществления мобильного устройства, в котором могут быть использованы разъемы интерфейса с плоской поверхностью. В одном варианте осуществления вычислительное устройство 1600 представляет собой такое вычислительное устройство, как планшет, мобильный телефон или смартфон, беспроводное устройство чтения электронных книг или другое беспроводное мобильное устройство. Понятно, что некоторые из компонентов показаны в общем виде, и не все компоненты такого устройства показаны в устройстве 1600.

В одном варианте осуществления вычис