Десятичный двухразрядный сумматор в коде «2 из 5^

Иллюстрации

Показать всеРеферат

259480

ОПИСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соввтокнв

Социалксткчеокнв

Рвдпуйлнв

Зависимое от авт. свидетельства ¹

Заявлено 25.IV.1968 (№ 1236799/18-24} с присоединением заявки №

Приоритет

МПК G 065

УДК 681.325,54(088.8}

Комитвт по делам изобретений н открытий орк Совете Министров

СССР

Опубликовано 12.XI1.1969. Бюллетень ¹ 2 за 1970

Дата опубликования описания 28.IV.1970

Авторы изобретения

Г. Н. Киселева, А. В. Дроздов и В. А. Андреев

Заявитель Государственное союзное конструкторско-технологическое бюро по проектированию счетных машин

ДЕСЯТИЧНЫЙ ДВУХРАЗРЯДНЪ|Й СУММАТОР В КОДЕ «2 из 5»

Изобретение относится к области вычислительной техники и предназначено для сложения и вычитания чисел, представленных в коде

«2 из 5».

Известен десятичный одноразрядный сумматор в коде «2 из 5», содержащий преобразователи кодов слагаемых, матрицу сложения размером 5 5 элементов, схему коррекции результата, схему переносов. Выходы преобразователей кодов слагаемых соединены со входами матрицы сложения и схемы коррекции результата, выходы матрицы сложения соеди,нены со входами схемы коррекции и через схему переносов с преобразователямп кода первого слагаемого. Сложение (вычитание) одного разряда выполняется за четыре такта.

Для быстродействия в предлагаемом сумматоре схема местного управления соединена с преобразователями кодов младшего разряда первого и второго слагаемых и с преобразователем кода сгаршего разряда второго слагаемого, выходы схемы переноса младшего разряда соединены со входами схем

;выдачи старших разрядов суммы, выходы схемы переноса старшего разряда соединены с управляющими входами преобразователя кода младшего разряда первого слагаемого; кроме того, в качестве элементов матрицы, соответствующих каждому одинаковому результату сложения, использованы многовходовые элементы.

Это позволяет выполнять сложение или вычитание в обоих разрядах сумматора за три такта, а также позволяет уменьшить количество элементов в матрице сложения до минимально возможного (до девяти элементов).

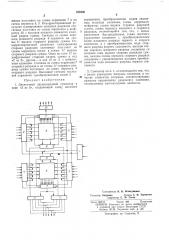

Схема сумматора изображена на чертеже.

Он содержит схему местного управления I, преобразователи кодов 2 — 5 соответственно младшего разряда первого слагаемого, младшего разряда второго слагаемого, старшего разряда первого слагаемого и старшего разряда второго слагаемого, матрицы сложения б, схемы коррекции 7, схемы переноса 8 и 9 младшего и старшего разрядов, шифратор И и схемы 11 выдачи старшего разряда суммы.

Сумматор работает следующим образом.

Сигналы, соответствующие командам «сложить» или «вычесть», поступают через схему местного управления на управляющие входы преобразователей кодов 2, 8 и 5. Преобразователи 2 — 5 расшифровывают подаваемые на них слагаемые в код «1 из 10» и посылают:гх на матрицы сложения б. Одновременно указанные преобразователи посылают сообщения в схемы коррекции 7 о четности или печетности прошедших через них слагаемых. Матр цы сложения б выполняют суммирование или

30 вычитание слагаемых, Сигналы с матриц сло259480 жения поступают на схемы коррекции 7 и на схемы, переноса 8, 9. Откорректированный результат суммирования младших разрядов слагаемых поступает из схемы коррекции в шифратор 10, с выходов которого снимается младший разряд суммы. Сигналы со схемы переноса младшего разряда 8 подаются на схемы 11 выдачи старшего разряда суммы. Откорректированный результат суммирования старших разрядов слагаемых поступает из схемы коррекции также в схемы 11 выдачи старшего разряда суммы, Одна из схем 11 зашифровывает старший разряд суммы в код

«2 из 5», другая — в код «2 из 5 с добавлением единицы». Сигналы из схемы коррекции 7 старшего, разряда и из схемы 11 старшего разряда суммы поступают на схему переноса 9 старшего разряда. Выходные сигналы последней управляют преобразователем кодов 2.

Предмет изобретения

1. Десятичный двухразрядный сумматор в коде «2 из 5», содержащий схему местного управления, .преобразователи кодов слагаемых, матрицы сложения, схемы коррекции, шифратор, схемы выдачи старших разрядов суммы, схемы переноса младшего и старшего разрядов, отличающийся тем, что, с целью увеличения быстродействия, схема местного управления соединена с преобразователями кодов младшего разряда первого и второго слагаемых и с преобразователем кода старшего разряда второго слагаемого, выходы схемы переноса младшего разряда соединены со входами схем выдачи старших разрядов суммы, выходы схемы переноса старшего разряда соединены с управляющими входами преобразователя кода младшего разряда первого слагаемсго.

2. Сумматор по п. 1, отличающийся тем, что, с целью упрощения матрицы сложения, в качестве элементов матрицы, соответствующих каждому одинаковому результату сложения, использованы многовходовые элементы.

Составитель В. В. Игнатущенко

Редактор Андреева Техред 3. Н, Тараненко

Корректор С. М. Сигал

3 ак аз 855/17 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совсте Министров СССР

Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2