Устройство выборки и хранения

Иллюстрации

Показать всеИзобретение относится к автоматике и измерительной технике и может быть использовано в аналого-цифровых системах обработки сигналов. Техническим результатом является повышение точности запоминания величины напряжения входного сигнала при одновременной стабилизации интервалов времени выборки Δtвыб. и времени хранения Δtхр. Устройство выборки и хранения содержит: элемент задержки, триггер, неинвертирующий усилитель на операционном усилителе, два аналоговых ключа, повторитель на операционном усилителе, конденсатор хранения, три компаратора, логический инвертор, два элемента 2И, элемент 2ИЛИ, формирователь укороченного импульса и связи между ними. 8 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к автоматике и измерительной технике и может быть использовано в аналого-цифровых системах обработки сигналов.

Уровень техники

Известно устройство выборки и хранения, содержащие аналоговый ключ, два операционных усилителя, конденсатор хранения, резистор цепи обратной связи, резистор ограничения, два встречно включенных диода ([1, с. 102, рис. 3] - Жаворонкова М.С., Бондарь С.Н. Разработка быстродействующего устройства выборки и хранения повышенной точности // Методы и технические средства повышения эффективности использования электрооборудования в промышленности и сельском хозяйстве: сб. науч. тр. по материалам 75-й научно-практической конференции электроэнергетического факультета СтГАУ. - Ставрополь: АГРУС, 2011. С.100-104).

Особенностью данного устройства является выполнение условия:

где Δtвыб - время выборки;

τз - постоянная времени цепи заряда конденсатора хранения.

На этапе выборки напряжение на конденсаторе хранения UC(t) описывается выражением:

где Uвх - напряжение входного сигнала в момент выборки;

UС.оз - остаточное напряжение заряда конденсатора хранения в период выборки, соответствует (без учета спада выходного напряжения) UС(t=tвыб.-1) предыдущей выборки.

Недостатком указанного способа является низкая точность запоминания величины напряжения входного сигнала и большое значение величины времени выборки Δtвыб.

Наиболее близким аналогом-прототипом к заявляемому техническому решению является устройство выборки и хранения ([2] - патент RU 2389070, МПК G06G 7/00).

Устройство выборки и хранения содержит дифференциальный усилитель напряжения, схему сравнения, повторитель на операционном усилителе, триггер, формирователь укороченного импульса, элемент задержки, элемент И, аналоговый ключ, конденсатор хранения, причем информационный вход устройства выборки и хранения одновременно является неинвертирующим входом дифференциального усилителя напряжения и вторым входом схемы сравнения, первый вход которой соединен одновременно с инвертирующим входом дифференциального усилителя напряжения и выходом повторителя на операционном усилителе, выход которого служит выходом устройства выборки и хранения; выход схемы сравнения подключен к R-входу триггера, S-вход которого через формирователь укороченного импульса одновременно соединен с входом управления устройства выборки и хранения и входом элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с прямым выходом триггера; выход элемента И подключен к входу управления аналогового ключа, вход которого соединен с выходом дифференциального усилителя напряжения, а выход одновременно подключен к входам конденсатора хранения и повторителя на операционном усилителе; схема сравнения содержит два компаратора и элемент И, входы которого являются выходами компараторов, а выход служит выходом схемы сравнения, разноименные входы компараторов соединены между собой и со входами схемы сравнения.

В силу условия

где K - коэффициент усиления дифференциального усилителя, напряжение на конденсаторе хранения, на этапе выборки Δtвыб., в общем случае, описывается выражением:

где ±E - напряжение питания дифференциального усилителя, к которому будет стремиться выходное напряжение дифференциального усилителя Uвых, с учетом условия:

Фактически, в устройстве имеет место ускоренный перезаряд конденсатора хранения, а сам процесс запоминания аналогового напряжения реализуется в ходе выполнения ряда операций.

1) Преобразования амплитуды входного аналогового сигнала до напряжения питания дифференциального усилителя (приведение |Uвх(t)| к |E|).

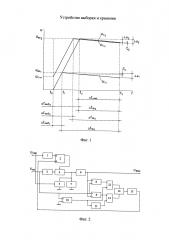

2) Ускоренного перезаряда конденсатора хранения (первое слагаемое выражения (4), фиг. 1, кривая UC1, UC2) с учетом остаточного напряжения заряда конденсатора хранения (второе слагаемое выражения (4), фиг. 1, кривая UC3) в течение интервала выборки Δtвыб., определяемый, в свою очередь, условием (6))

3) Считывания запомненного напряжения в течение времени Atc4KT на интервале времени хранения Δtxp. (фиг. 1), причем согласно условию (7)

Второе слагаемое выражения (4) (его знак и величина) приводит к неопределенности значения времени выборки Δtвыб. (может способствовать как уменьшению, так и увеличению времени выборки (фиг. 1, кривая UC3 →Δtвыб.3).

Как следует из анализа первого слагаемого выражения (4), укоренный заряд конденсатора хранения, с опорой на напряжение питания дифференциального усилителя Eп, сопровождается значительной неравномерностью скорости заряда конденсатора, а значит и временем выборки (фиг. 1: кривая UC1→Δtвыб.1; UС2→Δtвыб.2)

В силу резкой неравномерности времени выборки Δtвыб. время хранения Δtxp., до момента завершения считывания информации (фиг. 1, t3), так как считывающие устройства, например АЦП, функционируют в синхронном режиме (в интервале времени Δtсчит=t3-t2, фиг. 1), будет также неравномерно (фиг. 1: кривая UC1→Δtxp.1; кривая UC2→Δtxp.2; кривая UC3→Δtxp.3)

а значит, в силу разряда конденсатора ΔU на этапе хранения (фиг. 1, кривая UC2→ΔU2) и причем, с учетом дополнительного времени хранения Δtдоп.хр. (фиг. 1: кривая UC1→Δtдоп.хр.1 кривая UC3→Δtдоп.хр.3), выражение (10)

будет иметь большая погрешность выборки мгновенного значения аналогового напряжения (фиг. 1: кривая UC1→ΔU1; кривая UC2→ΔU2; кривая UC3→ΔU3), выражение (11)

где ξ - дополнительный разряд конденсатора на этапе дополнительного хранения.

Таким образом, недостатком указанного устройства является низкая точность запоминания величины напряжения входного сигнала и неопределенность значения величины времени выборки Δtвыб.

Раскрытие изобретения

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, сводится к повышению точности запоминания величины напряжения входного сигнала при одновременной стабилизации интервалов времени выборки Δtвыб. и времени хранения Δtхр.

Технический результат достигается тем, что в устройство выборки и хранения, содержащее элемент задержки, вход которого соединен со входом управления устройством, а выход соединен с S-входом триггера, R-вход которого соединен с выходом формирователя укороченного импульса, выход триггера соединен с входом управления первого аналогового ключа, выход которого непосредственно соединен с первым входом конденсатора хранения, второй вход которого заземлен, и через повторитель на операционном усилителе - с выходом устройства, а так же неинвертирующим входом первого компаратора и инвертирующим входом второго компаратора, выходы которых соединены с первыми входами элементов 2И, введены неинвертирующий усилитель на операционном усилителе, второй аналоговый ключ, третий компаратор, логический инвертор, элемент 2ИЛИ, причем выход неинвертирующего усилителя на операционном усилителе соединен с входом первого аналогового ключа, а выход соединен со входом устройства, а так же инвертирующим входом первого компаратора, неинвертирующими входами второго и третьего компараторов, инвертирующий вход третьего компаратора заземлен, а выход соединен непосредственно со вторым входом первого элемента 2И и через логический инвертор - со вторым входом второго элемента 2И, выходы элементов 2И соединены со входами элемента 2ИЛИ, выход которого соединен со входом формирователя укороченного импульса.

Краткое описание чертежей

На фиг. 1, 3÷8 приведены временные диаграммы, поясняющие работу устройства.

На фиг. 2 приведена функциональная схема устройства выборки и хранения.

Осуществление изобретения

Устройство выборки и хранения содержит элемент задержки 1, триггер 2, неинвертирующий усилитель на операционном усилителе 3, первый аналоговый ключ 4, второй аналоговый ключ 5, повторитель на операционном усилителе 6, конденсатор хранения 7, первый компаратор 8, второй компаратор 9, третий компаратор 10, логический инвертор 11, первый элемент 2И 12, второй элемент 2И 13, элемент 2ИЛИ 14, формирователь укороченного импульса 15, причем вход управления устройством соединен со входом управления второго аналогового ключа 5, параллельно подключенного к конденсатору хранения 7, и входом элемента задержки 1, выход которого соединен с S-входом триггера 2, R-вход которого соединен с выходом формирователя укороченного импульса 15; выход триггера 2 соединен с входом управления первого аналогового ключа 4, выход которого непосредственно соединен с первым входом конденсатора хранения 7, второй вход которого заземлен, и через повторитель на операционном усилителе 6 с выходом устройства, а так же неинвертирующим входом первого компаратора 8 и инвертирующим входом второго компаратора 9, выходы которых соединены с первыми входами элементов 2И 12 и 13; выход неинвертирующего усилителя на операционном усилителе 3 соединен с входом первого аналогового ключа 4, а выход соединен со входом устройства, а так же инвертирующим входом первого компаратора 8, неинвертирующими входами второго компаратора 9 и третьего компаратора 10; инвертирующий вход третьего компаратора 10 заземлен, а выход соединен непосредственно со вторым входом первого элемента 2И 12 и через логический инвертор 11 - со вторым входом второго элемента 2И 13; выходы элементов 2И 13 соединены со входами элемента 2ИЛИ 14, выход которого соединен со входом формирователя укороченного импульса 15.

В основе принципа функционирования предлагаемого устройства выборки и хранения лежит ряд операций.

1) Принудительный ускоренный разряд (ПУР) конденсатора хранения 7 согласно выражению (12)

где τпур - постоянная времени цепи принудительного ускоренного разряда конденсатора хранения.

Причем:

и в пределе

что обеспечивается аналоговым ключом 5. А значит, интервал времени принудительного ускоренного разряда конденсатора хранения Δtпур, фиг. 3, характеризуется условием

2) Ускоренный заряд конденсатора хранения согласно выражению (16)

где K - коэффициент усиления неинвертирующего усилителя на операционном усилителе 3 (с напряжением питания |Е|) предлагаемого устройства выборки и хранения, причем:

где Uвх.max - максимальная амплитуда запоминаемого сигнала.

С учетом выражений (6), (16) и (17) будут иметь место соотношения:

Из которых следует возможность стабилизации интервала выборки Δtвыб., (фиг. 3: кривая UC1→Δtвыб.1; кривая UC2→Δtвыб.2; Δtвыб.=Δtвыб.1=Δtвыб.2).

3) Считывание запомненного напряжения в течение времени Δtсчит на интервале времени хранения Δtхр. (фиг. 3: кривая UС1→Δtхр.1; кривая UC2→Δtхр.2; Δtсчит.=Δtхр.1=Δtхр.2) - имеет место стабилизация интервала хранения Δtхр.

Работа устройства поясняется временными диаграммами (фиг. 4÷8), на которых показаны:

- импульс запуска устройства выборки и хранения (входное управляющее напряжение uупр) (фиг. 4, а);

- выходное напряжение u1 элемента задержки 1 (фиг. 4, б);

- выходное напряжение u2 триггера 2 (фиг. 4, в);

- выходное напряжение u3 неинвертирующего усилителя на операционном усилителе 3 (фиг. 4, г);

- входное напряжение устройства uвх, выходное напряжение u6 повторителя на операционном усилителе 6 (фиг. 4, д; фиг. 5, а; фиг. 6, а; фиг. 7, а; фиг. 8, а);

- выходное напряжение u10 третьего компаратора 10 (фиг. 4, е);

- выходное напряжение u11 логического инвертора 11 (фиг. 4, ж);

- выходное напряжение u15 формирователя укороченного импульса 15 (фиг. 4, и).

- выходное напряжение u8 первого компаратора 8 (фиг. 5, б; фиг. 6, б; фиг. 7, б; фиг. 8, б);

- выходное напряжение u12 первого элемента 2И 12 и элемента 2ИЛИ 14 (фиг. 5, б; фиг. 6, б);

- выходное напряжение u9 второго компаратора 9 (фиг. 5, в; фиг. 6, в; фиг. 7, в; фиг. 8, в);

- выходное напряжение u13 второго элемента 2И 13 и элемента 2ИЛИ 14 (фиг. 7, в; фиг. 8, в).

На фиг. 5÷8 приведены выходные сигналы компараторов 8, 9 и элементов 2И 12, 13 и 2ИЛИ 14 для различных случаев формы входного сигнала.

Устройство выборки и хранения работает следующим образом. Сигнал uвх (фиг. 4, д), подаваемый на неинвертирующий вход усилителя на операционном усилителе 3, линейно усиливается в K раз (фиг. 4, г).

Импульс запуска uупр, поступающий на вход управления устройства выборки и хранения в интервале времени Δtпур=t1-t0 (фиг. 2; фиг. 4, a) (Δtпур=t7-t6 (фиг. 4, а)), обеспечивает замыкание контактов второго аналогового ключа 5 и шунтирование конденсатора хранения 7, выражение (14), и, тем самым, осуществляет принудительный ускоренный разряд конденсатора хранения (фиг. 2), выражения (12) и (15).

Импульс, сформированный на выходе элемента задержки 1 (фиг. 4, б), переводит триггер 2 в единичное состояние (фиг. 4, в), а первый аналоговый ключ 4 - в замкнутое состояние, обеспечивая тем самым заряд конденсатора хранения 7 согласно выражению (16) - с момента времени t1 начинается интервал выборки.

Так как конденсатор хранения 7 подключен ко входу повторителя на операционном усилителе 6, то на выходе последнего, служащего выходом устройства, будет напряжение, соответствующее значению напряжения Uc (фиг. 4, д; фиг. 5, а; фиг. 6, а; фиг. 7, а; фиг. 8, а).

Так как компараторы 8 и 9 включены параллельно, а их входы соединены встречно, выходные сигналы будут противофазны (фиг. 5, 6, в; фиг. 6, 6, в; фиг. 7, 6, в; фиг. 7, 6, в).

В момент времени t3 (t8) (фиг. 4, д), t2 (фиг. 5, а; фиг. 6, а; фиг. 7, а; фиг. 8, а) напряжение u6 будет равно мгновенному значению аналогового входного напряжения u в х ( t = t 3 ( t 8 ) ) (фиг. 4, д), u в х ( t = t 2 ) (фиг. 5, а; фиг. 6, а; фиг. 7, а; фиг. 8, а) устройства, но, в силу конечного времени срабатывания цепи управления первым аналоговым ключом 4, то есть выполнения условия (21)

на выходе компараторов 8 (при uвх>0, фиг. 5, б; фиг. 6, б) и 9 (при uвх<0, фиг. 7, в; фиг. 8, в) будут ненулевые уровни напряжения, которые с учетом выходного напряжения третьего компаратора 10 (фиг. 4, е) и логического инвертора 11 (фиг. 4, ж) обеспечат перепад напряжения «0-1» на выходе первого элемента 2И 12 (при uвх>0), второго элемента 2И 13 (при uвх<0), элемента 2ИЛИ 14 (фиг. 5, б; фиг. 6, б; фиг. 7, в; фиг. 8, в) и последующий переброс триггера 2 в состояние логического «0» (фиг. 4, в), под действием выходного импульса формирователя укороченного импульса 15 (фиг. 4, и), что приводит к размыканию первого аналогового ключа 4.

В итоге, конденсатор 7 запоминает напряжение, которое равно мгновенному значению входного напряжения в момент времени t3 (t8) (фиг. 4, д), t2 (фиг. 5, а; фиг. 6, а; фиг. 7, а; фиг. 8, а), т.е. производится формирование выборки мгновенного значения. Время хранения равно Δtхр=t6-t3 (фиг. 4, д) (Δtхр=t3-t2 (фиг. 2)), в течение которого можно использовать полученную информацию о значении выборки в соответствии с решаемыми задачами.

В момент времени t6 (фиг. 4) начинается следующий цикл работы устройства.

Формирователь укороченного импульса 15 может быть выполнен по обычной схеме на основе ждущего мультивибратора или одновибратора, запускающегося перепадом выходного напряжения элемента 2ИЛИ 14.

Так как, в предлагаемом устройстве первый этап (принудительного ускоренного разряда конденсатора хранения) и второй этап (ускоренного заряда конденсатора хранения - этап выборки), с учетом выражений (12)÷(20), стабилизированы по времени (неопределенность значения величины времени выборки Δtвыб устранена), то и третий этап (считывания - хранения), так же может быть стабилизирован, а значит условие (7) прототипа для предлагаемого устройства примет вид (8)

и с учетом выражений (10), (11) (фиг. 1) правомерно утверждать о повышении точности запоминания величины напряжения входного сигнала.

Устройство выборки и хранения, содержащее элемент задержки, вход которого соединен со входом управления устройством, а выход соединен с S-входом триггера, R-вход которого соединен с выходом формирователя укороченного импульса, выход триггера соединен с входом управления первого аналогового ключа, выход которого непосредственно соединен с первым входом конденсатора хранения, второй вход которого заземлен, и через повторитель на операционном усилителе с выходом устройства, а также неинвертирующим входом первого компаратора и инвертирующим входом второго компаратора, выходы которых соединены с первыми входами двух элементов 2И, отличающееся тем, что в устройство введены неинвертирующий усилитель на операционном усилителе, второй аналоговый ключ, третий компаратор, логический инвертор, элемент 2ИЛИ, причем выход неинвертирующего усилителя на операционном усилителе соединен с входом первого аналогового ключа, а выход соединен со входом устройства, а также инвертирующим входом первого компаратора, неинвертирующими входами второго и третьего компараторов, инвертирующий вход третьего компаратора заземлен, а выход соединен непосредственно со вторым входом первого элемента 2И и через логический инвертор со вторым входом второго элемента 2И, выходы элементов 2И соединены со входами элемента 2ИЛИ, выход которого соединен со входом формирователя укороченного импульса.