Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеГруппа изобретений относится к области передачи данных и может быть использована для кодирования/декодирования с использованием LDPC-кода. Техническим результатом является повышение устойчивости к ошибке данных. LDPC-код, имеющий кодовую длину, равную 16200 битов, и скорость кодирования, равную 1/3, модулируется с помощью 16QAM, если кодовый бит из 4×2 битов и (i+1)-ый бит из наиболее значимого бита символьных битов из 4×2 битов двух последовательных символов установлены в битах b#i и y#i, при этом демультиплексор выполняет перестановку для назначения битов b0, b1, b2, b3, b4, b5, b6 и b7 битам y6, y0, y3, y4, y5, y2, y1 и y7 соответственно. 8 н.п. ф-лы, 178 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и способу обработки данных и, в частности, к устройству обработки данных и способу обработки данных, которые позволяют повысить устойчивость к ошибке данных.

Уровень техники

LDPC (код контроля четности с низкой плотностью) имеет высокую способность коррекции ошибок и в последнее время широко принят в передающей системе, включающей в себя спутниковое цифровое широковещание, такое как DVB (цифровое видеошироковещание)-S.2, выполненное в Европе (например, смотри непатентную литературу 1). В дополнение к этому, проведены исследования принятия LDPC-кода к наземному цифровому широковещанию следующего поколения.

Из приведенных недавно исследований известно, что производительность, близкая к пределу Шеннона, получается из LDPC-кода, когда длина кода увеличивается, аналогично турбокоду. Так как LDPC-код имеет свойство, которое состоит в том, что кратчайшее расстояние пропорционально длине кода, LDPC-код имеет преимущества, связанные с превосходными характеристиками вероятности блочной ошибки, и редко встречается так называемое явление минимального уровня ошибок, наблюдаемого в характеристике декодирования турбокода, в качестве его характеристики.

В дальнейшем будет, главным образом, описан LDPC-код. LDPC-код является линейным кодом, и LDPC-код необязательно должен представлять собой двоичный код. Однако, в этом случае, предполагается, что LDPC-код является двоичным кодом.

Максимальная характеристика LDPC-кода состоит в том, что матрица контроля четности, определяющая LDPC-код, является разреженной. В этом случае, разреженная матрица представляет собой матрицу, в которой число 1 элементов матрицы является очень маленьким (то есть матрицу, в которой большая часть элементов равна 0).

Фиг.1 иллюстрирует пример матрицы Н контроля четности LDPC-кода.

В матрице H контроля четности, показанной на фиг.1, вес каждого столбца (вес столбца) (число 1) становится равным "3", и вес каждой строки (вес строки) становится равным "6".

При кодировании с использованием LDPC-кода (LDPC-кодирование), например, порождающая матрица G генерируется на основе матрицы Н контроля четности, и порождающая матрица G умножается на двоичные информационные биты таким образом, чтобы сгенерировать кодовое слово (LDPC-код).

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет порождающую матрицу G, в которой выполняется выражение GHT=0, между транспонированной матрицей HT матрицы Н контроля четности и порождающей матрицей G. В этом случае, когда порождающая матрица G представляет собой матрицу K×N, устройство кодирования перемножает порождающая матрица G с битовой строкой (вектором и) информационных бит, включающих в себя N битов, и генерирует кодовое слово с (= uG), включающее в себя N битов. Кодовое слово (LDPC-код), которое генерируется с помощью кодирующего устройства, принимается на приемной стороне через заданный канал связи.

LDPC-код можно декодировать с помощью алгоритма, который называется вероятностным декодированием, предложенным Галлагером (Gallager), то есть алгоритм передачи сообщений, использующий распространение степени уверенности на так называемом графе Таннера (Tanner), включающим в себя переменный узел (который также называется узлом сообщения) и проверочный узел. В дальнейшем переменный узел и проверочный узел будут, соответственно, называться просто узлами.

Фиг.2 иллюстрирует последовательность декодирования LDPC-кода.

В дальнейшем, действительное значение, которое получается путем представления правдоподобия, равного 0, значения i-того бита кода LDPC-кода (одного кодового слова), принятого на приемной стороне с помощью отношения логарифмического правдоподобия, соответственно, называется как значение u0i приема. В дополнение к этому, сообщение, выводимое из проверочного узла, называется как uj, и сообщение, выводимое из переменного узла, называется как vi.

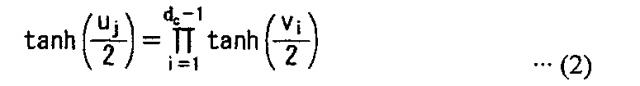

Сначала, при декодировании LDPC-кода, как иллюстрировано на фиг.2, на этапе S11 принимают LDPC-код, сообщению (сообщению проверочного кода) uj присваивают начальное значение 0, и переменной k, принимающей целочисленные значения в качестве счетчика процесса повторения, присваивают начальное значение 0, и процесс продолжается на этапе S12. На этапе S12 сообщение (сообщение переменного узла) vi вычисляется путем выполнения операции (операции переменного узла), представленной выражением (1), на основании значения u0i приема, полученного путем приема LDPC-кода, и сообщение uj вычисляется путем выполнения операции (операции проверочного узла) представленной выражением (2) на основании сообщения vi.

(Выражение 1)

(Выражение 2)

В этом случае, dv и dc в выражениях (1) и (2) представляют собой параметры, которые показывают числа 1 матрицы H контроля четности в продольном направлении (столбец) и в поперечном направлении (строка), соответственно, и можно произвольно установить, соответственно. Например, в случае кода (3, 6), dv принимает значение 3, и dc принимает значение 6.

При работе переменного узла согласно выражению (1) и при работе проверочного узла согласно выражению (2), так как сообщение, выходящее из ребра графа (линия, связывающая переменный узел и проверочный узел) для вывода сообщения, не является целью работы, рабочий диапазон становится равным от 1 до dv - 1 или от 1 до dc - 1. Работа проверочного узла согласно выражению (2) выполняется фактически за счет предварительного создания таблицы функции R (v1, v2), представленной выражением (3), определенным одним входом по отношению к двум выходам v1 и v2 и использующего таблицу последовательно (рекурсивно), как представлено выражением (4).

(Выражение 3)

(Выражение 4)

На этапе S12 переменная k увеличивает свое значение на 1, и процесс переходит к этапу S13. На этапе S13 определяют, больше ли значение переменной k, чем заданное число раз C повторного декодирования. Когда на этапе S13 определено, что переменная k не больше, чем C, процесс возвращается на этап S12, и в дальнейшем повторяется тот же самый процесс.

Когда на этапе S13 определено, что переменная k больше, чем C, процесс переходит на этап S14, сообщение vi, которое соответствует результату декодирования, который будет окончательно выводиться, вычисляется путем выполнения операции, представленной выражением (5), и выводится, и процесс декодирования LDPC-кода заканчивается.

(Выражение 5)

В этом случае, работа согласно выражению (5) выполняется с использованием сообщений uj из всех ребер, соединенных с переменным узлом, которая отличается от работы переменного узла согласно выражению (1).

Фиг.3 иллюстрирует пример матрицы Н контроля четности LDPC-кода (3, 6) (скорость кодирования равна 1/2, и длина кода равна 12).

В матрице H контроля четности, показанной на фиг.3, вес столбца установлен на 3, и вес строки установлен на 6 аналогично фиг.1.

Фиг.4 иллюстрирует граф Таннера матрицы H контроля четности, показанной на фиг.3.

На фиг.4 проверочный узел представлен знаком "+", и переменный узел представлен знаком "=". Проверочный узел и переменный узел соответствуют строке и столбцу матрицы H контроля четности. Линия, которая соединяет проверочный узел и переменный узел, представляет собой ребро и соответствует значению 1 элементов матрицы контроля четности.

Иными словами, когда элемент j-ой строки и i-го столбца матрицы контроля четности равен 1, как показано на фиг.4, i-ый переменный узел (узел "=") с верхней стороны и j-ый проверочный узел (узел "+") с верхней стороны соединены ребром. Ребро показывает, что бит кода, соответствующий переменному узлу, имеет условие ограничения, соответствующее проверочному узлу.

В алгоритме суммы произведений, который представляет собой способ декодирования LDPC-кода, операция переменного узла и операция проверочного узла выполняются последовательно одна за другой.

Фиг.5 иллюстрирует операцию переменного узла, которая выполняется с помощью переменного узла.

В переменном узле сообщение vi, которое соответствует ребру для вычисления, вычисляется с помощью операции переменного узла согласно выражению (1) с использованием сообщений u1 и u2 из оставшихся ребер, соединенных с переменным узлом, и значения u0i приема. Сообщения, которые соответствуют другим ребрам, также вычисляются тем же самым способом.

Фиг.6 иллюстрирует операцию проверочного узла, которая выполняется с помощью проверочного узла.

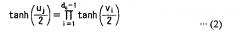

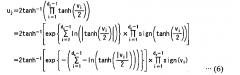

В этом случае, операцию проверочного узла согласно выражению 2 можно переписать с помощью выражения 6, используя уравнение в виде выражения a×b=exp{ln(|a|)+ln(|b|)}×sign(a)×sign(b). Однако значение sign(x) равно 1 в случае x≥0, и равно -1 в случае x<0.

(Выражение 6)

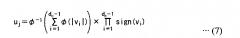

При x≥0, если функция ϕ(x) задана в виде выражения ϕ(x)=ln(tanh(x/2)), выполняется выражение ϕ-1(x)=2tanh-1 (e-x). По этой причине выражение (6) можно заменить на выражение (7).

(Выражение 7)

В проверочном узле операция проверочного узла согласно выражению (2) выполняется согласно выражению (7).

Иными словами, в проверочном узле, как иллюстрировано на фиг.6, сообщение uj, которое соответствуют ребру графа для вычисления, вычисляется с помощью операции проверочного узла согласно выражению (7) с использованием сообщений v1, v2, v3, v4, и v5 из оставшихся ребер, соединенных с проверочным узлом. Сообщения, которые соответствуют другим ребрам, также вычисляются с помощью того же самого способа.

Функцию ϕ(x) из выражения (7) можно представить в виде ϕ(x)=ln((ex+1)/(ex-1)), и условие ϕ(x)=ϕ-1(x) выполняется при x>0. Когда функции ϕ(x) и ϕ-1(x) осуществлены в аппаратных средствах, функции ϕ(x) и ϕ-1(x) можно осуществить с использованием LUT (справочная таблица). Однако обе функции ϕ(x) и ϕ-1(x) принимают вид той же самой LUT.

Цитируемая литература

Непатентная литература

Непатентная литература 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Техническая задача

LDPC-код принят для DVB-S.2 в качестве стандарта спутникового цифрового широковещания или DVB-T.2 в качестве стандарта наземного цифрового широковещания следующего поколения. Помимо этого планируется принятие LDPC-кода в DVB-C.2 в качестве стандарта цифрового широковещания следующего поколения CATV (кабельного телевидения).

При цифровом широковещании на базе стандарта DVB, такого как DVB-S.2, LDPC-код принимает вид символа (символизируется) ортогональной модуляцией (цифровой модуляцией), такой как QPSK (квадратурная фазовая манипуляция), и символ отображается в сигнальную точку и передается.

При символизации LDPC-кода выполняется перестановка кодовых битов LDPC-кода в блоке кодовых битов из двух битов или более, и переставленные кодовые биты принимают вид битов символа.

В качестве способа перестановки кодовых бит для символизации LDPC-кода предложены различные способы. Например, способ перестановки определен в DVB-T.2.

Между тем, DVB-T.2 является стандартом цифрового широковещания, который используется исключительно для фиксированного оконечного устройства, такого как телевизионный приемник, установленный дома, и который не может соответствовать предъявляемым требованиям при цифровом широковещании, которое используется исключительно для портативного оконечного устройства.

Иными словами, по сравнению с фиксированном оконечным устройством, в портативном оконечном устройстве необходимо уменьшить размеры схемы и уменьшить потребляемую мощность. Поэтому в цифровом широковещании, которое используется исключительно для портативного оконечного устройства, для того, чтобы облегчить нагрузку, необходимую для обработки, такой как декодирование LDPC-кода в портативном оконечном устройстве, число раз повторений (число раз C повторного декодирования) декодирования LDPC-кода или кодовой длины LDPC-кода можно сократить больше, чем в случае цифрового широковещания, используемого исключительно для фиксированного оконечного устройства.

Однако в рамках ограничений необходимо поддерживать до некоторой степени устойчивость к ошибке.

Настоящее изобретение было выполнено с учетом вышеупомянутых обстоятельств, и оно позволяет обеспечить устойчивость к ошибке данных, таких как LDPC-код.

Решение задачи

Согласно первому варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок кодирования или этап кодирования, для выполнения LDPC-кодирования, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, на основе матрицы контроля четности LDPC-кода, и блок перестановки или этап перестановки, для выполнения перестановки кодовых битов кодированного LDPC-кода с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

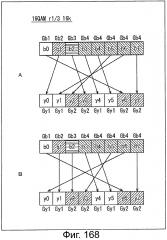

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y6, y0, y3, y4, y5, y2, y1 и y7, соответственно.

Согласно второму варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок кодирования или этап кодирования, для выполнения LDPC-кодирования, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, на основе матрицы контроля четности LDPC-кода, и блок перестановки или этап перестановки, для выполнения перестановки кодовых битов кодированного LDPC-кода с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 в области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y7, y5 y4, y0, y3, y1, y2 и y6, соответственно.

Согласно третьему варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок обратной перестановки или этап обратной перестановки, для выполнения перестановки символьных битов символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, и блок декодирования или этап декодирования, для декодирования LDPC-кода, переставленного с помощью блока обратной перестановки или этапа обратной перестановки, на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок обратной перестановки или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y6, y0, y3, y4, y5, y2, y1 и y7 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Согласно четвертому варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок обратной перестановки или этап обратной перестановки, для выполнения перестановки символьных битов символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, и блок декодирования или этап декодирования, для декодирования LDPC-кода, переставленного с помощью блока обратной перестановки или этапа обратной перестановки, на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти, равный 16200/8 битам, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок обратной перестановки или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y7, y5, y4, y0, y3, y1, y2 и y6 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Согласно первому варианту осуществления настоящей технологии LDPC-кодирование, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, выполняется на основе матрицы контроля четности LDPC-кода, и кодовые биты кодированного LDPC-кода перестанавливаются с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y6, y0, y3, y4, y5, y2, y1 и y7, соответственно.

Согласно второму варианту осуществления настоящей технологии LDPC-кодирование, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, выполняется на основе матрицы контроля четности LDPC-кода, и кодовые биты кодированного LDPC-кода перестанавливаются с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y7, y5 y4, y0, y3, y1, y2 и y6, соответственно.

Согласно третьему варианту осуществления настоящей технологии символьные биты символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, перестанавливаются с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, и LDPC-код с выполненной перестановкой декодируется на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y6, y0, y3, y4, y5, y2, y1 и y7 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Согласно четвертому варианту осуществления настоящей технологии символьные биты символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, перестанавливаются с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, и LDPC-код с выполненной перестановкой декодируется на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y7, y5, y4, y0, y3, y1, y2 и y6 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Устройство обработки данных может представлять собой независимое устройство и может представлять собой внутренний блок, образующий одно устройство.

Полезные эффекты изобретения

Согласно настоящему изобретению можно повысить устойчивость к ошибке.

Краткое описание чертежей

Фиг.1 - иллюстрация матрицы Н контроля четности LDPC-кода.

Фиг.2 - схема последовательности операций, иллюстрирующая последовательность декодирования LDPC-кода.

Фиг.3 - иллюстрация примера матрицы контроля четности LDPC-кода.

Фиг.4 - иллюстрация графа Таннера (Tanner) матрицы контроля четности.

Фиг.5 - иллюстрация переменного узла.

Фиг.6 - иллюстрация проверочного узла.

Фиг.7 - иллюстрация примера конфигурации варианта осуществления передающей системы, к которой применимо настоящее изобретение.

Фиг.8 - блок-схема, иллюстрирующая пример конфигурации передающего устройства 11.

Фиг.9 - блок-схема, иллюстрирующая пример конфигурации битового перемежителя 116.

Фиг.10 - иллюстрация матрицы контроля четности.

Фиг.11 - иллюстрация матрицы четности.

Фиг.12 - иллюстрация матрицы контроля четности LDPC-кода, заданного в стандарте DVB-S.2.

Фиг.13 - иллюстрация матрицы контроля четности LDPC-кода, заданного в стандарте DVB-S.2.

Фиг.14 - иллюстрация размещения сигнальных точек для формата модуляции 16QAM.

Фиг.15 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.16 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.17 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.18 - иллюстрация процесса, выполняемого демультиплексором 25.

Фиг.19 - иллюстрация процесса, выполняемого демультиплексором 25.

Фиг.20 - иллюстрация графа Таннера для декодирования LDPC-кода.

Фиг.21 - иллюстрация матрицы четности HT, которая принимает вид ступенчатой структуры, и графа Таннера, соответствующего матрице HT четности.

Фиг.22 - иллюстрация матрицы HT четности матрицы H контроля четности, соответствующей LDPC-коду после перемежения четности.

Фиг.23 - иллюстрация преобразованной матрицы контроля четности.

Фиг.24 - иллюстрация процесса, выполняемого перемежителем 24 с закручиванием столбцов.

Фиг.25 - иллюстрация количества столбцов памяти 31, необходимого для перемежения с закручиванием столбцов, и адреса начальной позиции записи.

Фиг.26 - иллюстрация количества столбцов памяти 31, необходимого для перемежения с закручиванием столбцов, и адреса начальной позиции записи.

Фиг.27 - схема последовательности операций, иллюстрирующая процесс, выполняемый битовым перемежителем 116 и QAM-кодером 117.

Фиг.28 - иллюстрация модели канала связи, принятой за основу моделирования.

Фиг.29 - иллюстрация зависимости частоты появления ошибок, которая принята за основу моделирования и допплеровской частоты fd дрожания.

Фиг.30 - иллюстрация зависимости частоты появления ошибок, которая принята за основу моделирования и допплеровской частоты fd дрожания.

Фиг.31 - блок-схема, иллюстрирующая пример конфигурации LDPC-кодера 115.

Фиг.32 - схема последовательности операций, иллюстрирующая процесс, выполняемый LDPC-кодером 115.

Фиг.33 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 16200.

Фиг.34 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 16200.

Фиг.35 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 16200.

Фиг.36 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 16200.

Фиг.37 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 16200.

Фиг.38 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 16200.

Фиг.39 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 16200.

Фиг.40 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/5, и длина кода составляет 16200.

Фиг.41 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 16200.

Фиг.42 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 16200.

Фиг.43 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 64800.

Фиг.44 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 64800.

Фиг.45 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 64800.

Фиг.46 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 64800.

Фиг.47 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 64800.

Фиг.48 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 64800.

Фиг.49 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.50 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.51 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.52 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.53 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.54 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.55 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.56 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.57 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.58 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.59 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.60 - иллюстрация примера таблицы исходны