Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеИзобретение относится к устройству обработки данных и к способу обработки данных. Технический результат - повышение устойчивости данных к ошибке. Для этого в случае, когда код LDPC (проверки на четность низкой плотности), имеющий длину кода 16200 битов и скорость кодирования 8/15, отображают на 16 сигнальных точек, если (#i+1)-е биты из старших значащих битов знаковых битов для 4×2 битов и символьных битов для 4×2 битов из двух последовательных символов устанавливают в качестве битов b#i и y#i, соответственно, демультиплексор выполняет взаимную замену для выделения b0, b1, b2, b3, b4, b5, b6 и b7 для y0, y4, y3, y1, y2, y5, y6 и y7, соответственно. Настоящая технология может применяться в передающей системе и т.п., которая передает код LDPC. 12 н.п. ф-лы, 78 ил.

Реферат

Область техники, к которой относится изобретение

Существующая технология относится к устройству обработки данных и к способу обработки данных, и, в частности, к устройству обработки данных и способу обработки данных, которые позволяют повысить устойчивость к ошибкам данных.

Уровень техники

Код проверки на четность низкой плотности (LDPC) обладает высокими способностями коррекции ошибок и в последнее время был широко принят в системах передачи данных, включая в себя спутниковую цифровую широковещательную передачу, такую как цифровая широковещательная передача видеоданных (DVB)-S.2, развернутая в Европе (например, см. Непатентный документ 1). Кроме того, исследуется возможность использования кода LDPC для наземной цифровой широковещательной передачи данных следующего поколения.

В последних исследованиях определили, что рабочие характеристики рядом с пределом Шеннона могут быть получены в коде LDPC, при увеличении длины кода, аналогично турбокоду. Кроме того, поскольку код LDPC имеет свойство, состоящее в том, что самое короткое расстояние пропорционально длине кода, код LDPC имеет преимущества характеристики высокой вероятности ошибки блока и для него характерно, что редко генерируется так называемое явление минимального уровня ошибок в характеристике декодирования турбокода и т.п.

Далее, в частности, будет описан код LDPC. Код LDPC представляет собой линейный код, и не обязательно этот код LDPC должен быть двоичным кодом. Однако здесь предполагается, что код LDPC представляет собой двоичный код.

Характеристика максимума кода LDPC состоит в то, что матрица проверки на четность, определяющая код LDPC, является разреженной. Здесь разреженная матрица представляет собой матрицу, в которой количество "1" среди элементов матрицы очень мало (матрица, в которой большинство элементов равно 0).

На фиг.1 иллюстрируется пример матрицы Н проверки на четность кода LDPC.

В матрице Н проверки на четность по фиг.1 вес каждого столбца (вес столбца) (количество "1") становится равным "3", и вес каждого ряда (вес ряда) становится равным "6".

При кодировании, используя код LDPC (кодирование LDPC), например, порождающую матрицу G генерируют на основе матрицы Н проверки на четность, и порождающую матрицу G умножают на двоичные информационные биты, таким образом, что генерируют кодовое слово (код LDPC).

В частности, устройство кодирования, которое выполняет кодирование LDPC, вначале вычисляет порождающую матрицу G, в которой выражение GH=0 реализовано между транспонированной матрицей Н матрицы Н проверки на четность и порождающей матрицей G. Здесь, когда порождающая матрица G представляет собой матрицу K×N, устройство кодирования умножает порождающую матрицу G на строку битов (вектор и) информационных битов, состоящих из K битов, и генерирует кодовое слово с (=uG), состоящее из N битов. Кодовое слово (код LDPC), генерируемое устройством кодирования, принимают на стороне приема по заданному каналу передачи данных.

Код LDPC может быть декодирован с помощью алгоритма, называемого вероятностным декодированием, предложенным Галагером, который представляет собой алгоритм передачи сообщения, используя распространение доверительности по, так называемому, графу Таннера, состоящему из переменного узла (также называемого узлом сообщения) и проверочного узла. Здесь переменный узел и проверочный узел, соответственно, называются ниже просто узлами.

На фиг.2 иллюстрируется последовательность декодирования кода LDPC.

Ниже действительное значение (прием LLR), который получают, представляя вероятность, равную "0" для значения i-го знакового бита кода LDPC (одно кодового слова) принятого стороной приема, используя логарифмическое отношение вероятности, соответствующим образом, соотносят со значением u0i приема. Кроме того, сообщение, выводимое из узла проверки, называется uj, и сообщение, выводимое из переменного узла, называется Vi.

Вначале, при декодировании кода LDPC, как представлено на фиг.2, на этапе S11, принимают код LDPC, сообщение (сообщение узла проверки) uj инициализируют в "0", и переменную к, принимая целое число, как счетчик обработки повторения, инициализируют в "0", и обработка переходит на этап S12. На этапе S12, сообщение Vi (сообщение переменного узла) получают, выполняя операцию (операцию переменного узла), представленную выражением (1), на основе значения u0i приема, полученного путем приема кода LDPC, и сообщение uj получают, выполняя операцию (операцию проверочного узла), представленную выражением (2), на основе сообщения vi.

[Формула 1]

[Формула 2]

Здесь dv и dc в выражениях (1) и (2) представляют параметры, которые представляют количество "1" в матрице Н проверки на четность в вертикальном направлении (столбец) и в горизонтальном направлении (ряд), соответственно, и могут быть установлены произвольно, соответственно. Например, в случае кода (3, 6), dv=3 и dc=6.

В операции переменного узла, в соответствии с выражением (1) и в операции проверочного узла по выражению (2), поскольку сообщение, вводимое из ребра (линия, соединяющая переменный узел и проверочный узел), для вывода сообщения, не является целью операции, диапазон операции становится равным от 1 до dv - 1 или от 1 до dc - 1. Операцию проверочного узла по выражению (2) выполняют фактически, формируя заранее таблицу функции R (v1, v2), представленной выражением (3), определенным по одному выходу в отношении двух входных значений v1 и v2, и используя таблицу последовательно (рекурсивно), как представлено в выражении (4).

[Формула 3]

[Формула 4]

На этапе S12 выполняют последовательное приращение переменной k на "1", и обработка переходит на этап S13. На этапе S13 определяют, является ли переменная к большей, чем заданная величина подсчета С повторений декодирования. Когда определяют на этапе S13, что переменная k не больше, чем С, обработка возвращается на этап S12, и далее повторяют ту же самую обработку.

Когда на этапе S13 определяют, что переменная k больше, чем С, обработка переходит на этап S14, сообщение vi, которое соответствует результату декодирования, который должен быть, в конечном итоге выведен, получают, выполняя операцию, представленную выражением (5), и выводят, и обработка декодирования кода LDPC заканчивается.

[Формула 5]

Здесь выполняют операцию, в соответствии с выражением (5), используя сообщения uj со всех ребер, соединенных с переменным узлом, отличающимся от операции переменного узла по выражению (1).

На фиг.3 иллюстрируется пример матрицы Н проверки на четность для кода LDPC (3, 6) (для скорости кодирования 1/2 и длины кода 12).

В матрице Н проверки на четность по фиг.3, вес столбца установлен равным 3, и вес ряда установлен равным 6, аналогично фиг.1.

На фиг.4 иллюстрируется граф Таннера матрицы Н проверки на четность по фиг.

3.

На фиг.4 проверочный узел представлен плюсом "+", и переменный узел представлен знаком равенства "=". Проверочный узел и переменный узел соответствуют ряду и столбцу матрицы Н проверки на четность. Линия, которая соединяет проверочный узел и переменный узел, представляет собой ребро и соответствует "1" элементам матрицы проверки на четность.

Таким образом, когда элемент j-го ряда и i-го столбца матрицы проверки на четность равен 1, на фиг.4, i-й переменный узел (узел "=") с верхней стороны и j-й проверочный узел (узел "+") с верхней стороны соединяются ребром. Ребро представляет, что знаковый бит, соответствующий переменному узлу, имеет состояние ограничения, соответствующее проверочному узлу.

В алгоритме произведения суммы, который представляет собой способ декодирования кода LDPC, многократно выполняются операции переменного узла и операции проверочного узла.

На фиг.5 иллюстрируется операция переменного узла, которую выполняют с помощью переменного узла.

В переменном узле сообщение V;, которое соответствует ребру для вычисления, получают с помощью операции переменного узла по выражению (1), используя сообщения u1 и u2 из остальных ребер, соединенных с переменным узлом, и значение u0i приема. Сообщения, которые соответствуют другим ребрам, также получают, используя тот же способ.

На фиг.6 иллюстрируется операция проверочного узла, которую выполняет проверочный узел.

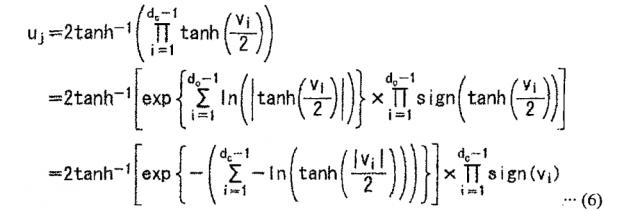

Здесь операция проверочного узла по выражению (2) может быть переписана в соответствии с выражением (6), используя соотношение выражения а×b=ехр{ln(|а|)+ln(|b|)}×sign(a)×sign(b). Однако sin(x) равен 1 в случае x≥0, и равен -1, в случае x<0.

[Формула 6]

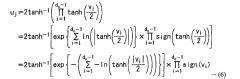

При x≥0, если функция ϕ(x) определена, как выражение ϕ(x)=ln(tanh(x/2)), реализуется выражение ϕ-1(x)=2tanh-1(е-x). По этой причине, выражение (6) может быть преобразовано в выражение (7).

[Формула 7]

В проверочном узле операцию проверочного узла по выражению (2) выполняют в соответствии с выражением (7).

Таким образом, в проверочном узле, как показано на фиг.6, сообщение uj, которое соответствует ребру для вычисления, получают, используя операцию проверочного узла по выражению (7), используя сообщения v1, v2, v3, v4 и v5 от остальных ребер, соединенных с проверочным узлом. Сообщения, которые соответствуют другим ребрам, также получают, используя тот же способ.

Функция ϕ(x) по выражению (7) может быть представлена, как выражение ϕ(x)==ln((ех+1)/(ex-1)), и ϕ(x)=ϕ-1(x) удовлетворяется при x>0. Когда функции ϕ(x) и ϕ-1(x) монтируют, как аппаратные средства, функции ϕ(x) и ϕ-1(x) могут быть установлены, используя справочную таблицу (LUT). Однако обе функции ϕ(x) и ϕ-1(x) становятся одной и той же LUT.

Список литературы

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Задачи, решаемые изобретением

Код LDPC принят в DVB-S.2, как стандарт при спутниковой цифровой широковещательной передаче, или в DVB-T.2, как стандарт для наземной цифровой широковещательной передачи следующего поколения. Кроме того, планируется использование кода LDPC в DVB-C.2 в качестве стандарта цифровой широковещательной передачи кабельного телевидения (CATV) следующего поколения.

В цифровой широковещательной передаче на основе стандарта DVB, такого как DVB-S.2, код LDPC становится символом (символизирован) ортогональной модуляции (цифровой модуляции), такой как квадратурная фазовая манипуляция (QPSK), и этот символ отображают на точку сигнала и передают.

При преобразовании в символы кода LDPC выполняют взаимную замену знаковых битов кода LDPC в единицах знаковых битов из двух битов или больше, и знаковые биты после взаимной замены становятся битами символа.

В качестве способа взаимной замены знаковых битов, для выражения символами кода LDPC, рассматриваются различные способы. Например, способ взаимной замены также определен в DVB-T.2.

В то же время, DVB-T.2 представляет стандарт цифровой широковещательной передачи, используемой исключительно для стационарных оконечных устройств, таких как телевизионный приемник, установленный в доме, и т.п., и, может не соответствовать цифровой широковещательной передаче, используемой исключительно для мобильного оконечного устройства.

Таким образом, по сравнению со стационарным оконечным устройством, в мобильном оконечном устройстве необходимо уменьшить размер схемы и уменьшить потребляемую энергию. Поэтому, при цифровой широковещательной передаче, исключительно используемой для мобильного оконечного устройства, для того, чтобы уменьшить нагрузку, необходимую для обработки такой, как декодирование кода LDPC в мобильном оконечном устройстве, величина подсчета повторений (повторений величины подсчета С декодирования) при декодировании кода LDPC или длина кода для кода LDPC могут быть ограничены в большей степени, чем в случае цифровой широковещательной передачи, используемой исключительно для стационарных оконечных устройств.

Однако необходимо поддерживать устойчивость к ошибке в определенной степени при таком ограничении.

Настоящая технология была разработана с учетом описанных выше обстоятельств и позволяет улучшить устойчивость к ошибке данных, таких как код LDPC.

Решение задач

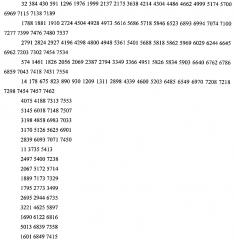

Устройство/способ обработки данных, в соответствии с первым аспектом настоящей технологии, представляет собой устройство/способ обработки данных, включающие в себя модуль/этап кодирования, который выполняет кодирование LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, на основе матрицы проверки на четность кода LDPC, и модуля/этапа взаимной замены, на котором выполняют взаимную замену знаковых битов кода LDPC на символьные биты для символа, соответствующего любой одной из 16 сигнальных точек, определенных 16QAM. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 части информационной матрицы для каждых 360 столбцов и выполнена следующим образом:

Когда знаковые биты из 8 битов, сохраненных в 8 модулях хранения, имеющих емкость хранения 16200/8 битов и считанных из соответствующих модулей хранения по одному биту, выделяют для двух последовательных символов, модуль/этап взаимной замены устанавливает (#i+1)-й бит из старших значащих битов знаковых битов из 8 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов из 8 битов двух символов в качестве бита y#i, и выполняет взаимную замену битов b0, b1, b2, b3, b4, b5, b6 и b7 на биты y0, y4, y3, y1, y2, y5, y6 и y7, соответственно.

В первом аспекте, описанном выше, кодирование LDPC, при котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, выполняют на основе матрицы проверки на четность кода LDPC, и выполняют взаимную замену знаковых битов кода LDPC с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных 16QAM. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Когда знаковые биты из 8 битов, сохраненных в 8 модулях хранения, имеющих емкость хранения 16200/8 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, (#i+1)-й бит из старших значащих битов знаковых битов из 8 битов передают в качестве бита b#i, при этом (#i+1)-й бит из старших значащих битов символьных битов среди 8 битов двух символов устанавливают в качестве бита y#i, и биты b0, b1, b2, b3, b4, b5, b6 и b7 взаимно заменяют с битами y0, y4, y3, y1, y2, y5, y6 и y7, соответственно.

Устройство/способ обработки данных, в соответствии со вторым аспектом настоящей технологии, представляют собой устройство/способ обработки данных, включающие в себя модуль/этап кодирования, который выполняет кодирование LDPC, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 7/15, на основе матрицы проверки на четность кода LDPC, и модуль/этап взаимной замены, который выполняет взаимную замену знаковых битов кода LDPC на символьные биты символа, соответствующего любой одной из 64 сигнальных точек, определенных 64QAM. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Когда знаковые биты из 12 битов, сохраненных в 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обмена устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 12 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов в качестве бита y#i, и биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11 взаимно заменяют с битами y2, y0, y8, y7, y1, y6, y4, y3, y10, y9, y5 и y11, соответственно.

Во втором аспекте, описанном выше, кодирование LDPC, при котором длина кода составляет 16200 битов и скорость кодирования равна 7/15, выполняют на основе матрицы проверки на четность кода LDPC, и выполняют взаимную замену знаковых битов кода LDPC с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных 64QAM. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, при этом область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Когда знаковые биты из 12 битов, сохраненных в 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, (#i+1)-й бит из старших значащих битов знаковых битов из 12 битов передают в качества бита b#i, при этом (#i+1)-й бит из старших значащих битов символьных битов среди 12 битов двух символов устанавливают в качестве бита y#i, и биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11 взаимно заменяют с битами y2, y0, y8, y7, y1, y6, y4, y3, y10, y9, y5 и y11, соответственно.

Устройство/способ обработки данных, в соответствии со вторым аспектом настоящей технологии, представляют собой устройство/способ обработки данных, включающие в себя модуль/этап кодирования, который выполняет кодирование LDPC, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, на основе матрицы проверки на четность кода LDPC, и модуль/этап взаимной замены, которые выполняют взаимные замены знаковых битов кода LDPC на символьные биты символа, соответствующего любой одной из 64 сигнальных точек, определенных 64QAM. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Когда знаковые биты из 12 битов, сохраненных в 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обмена устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 12 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов, в качестве бита y#i, и биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11 взаимно заменяют с битами y2, y0, y4, 1, y6, y7, y8, y5, y10, y3, y9 и y11, соответственно.

В третьем аспекте, описанном выше, кодирование LDPC, при котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, выполняют на основе матрицы проверки на четность кода LDPC, и выполняют взаимную замену знаковых битов кода LDPC с символьными битами символа, соответствующего любой одной из 64 сигнальных точек, определенных 64QAM. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом

Когда знаковые биты 12 битов, сохраненных в этих 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обмена устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 12 битов этих двух символов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов в качестве бита y#i, и заменяет биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11 с битами y2, y0, y4, y1, y6, y7, y8, y5, y10, y3, y9 и y11, соответственно.

Устройство/способ обработки данных, в соответствии с четвертым аспектом существующей технологии, представляют собой устройство/способ обработки данных, включающие в себя модуль/этап обратной взаимной замены, который выполняет взаимную замену битов символа, соответствующего любой из 16 сигнальных точек, определенных 16QAM, на знаковые биты кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, и модуль/этап декодирования, который декодирует код LDPC, после взаимной замены, выполненной модулем/этапом обратной взаимной замены, на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 8 из битов, сохраненных в 8 модулях хранения, имеющих емкость хранения 16200/8 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обратной взаимной замены устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 8 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 8 битов этих двух символов в качестве бита y#i, и выполняет взаимную замену битов y0, y4, y3, y1, y2, y5, y6 и y7 битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

В четвертом аспекте, описанном выше, символьные биты символа, соответствующего любой из 16 сигнальных точек, определенных 16QAM, чередуются со знаковыми битами кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, и код LDPC после взаимной замены декодируют на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 8 битов, сохраненных в этих 8 модулях хранения, имеющих емкость хранения 16200/8 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, (#i+1)-й бит из старших значащих битов знаковых битов 8 битов установлен в качестве бита b#i, (#i+1)-й бит из старших значащих битов символьных битов 8 битов этих двух символов установлен в качестве бита y#i, и биты y0, y4, y3, y1, y2, y5, y6 и y7 взаимно заменяют на биты b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Способ обработки данных/устройство обработки данных в соответствии с пятым аспектом настоящей технологии, представляют собой устройство/способ обработки данных, включающие в себя модуль/этап обратной взаимной замены, который выполняет взаимную замену битов символа, соответствующего любой из 64 сигнальных точек, определенных 64QAM, на знаковые биты кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 7/15, и модуль/этап декодирования, который декодирует код LDPC, после взаимной замены, выполненной модулем/этапом обратной взаимной замены, на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 12 битов, сохраненных в 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обратной взаимной замены устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 12 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов в качестве бита y#i, и выполняет взаимную замену битов y2, y0, y8, y7, y1, y6, y4, y3, y10, y9, y5 и y11 на биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11, соответственно. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

В пятом аспекте, описанном выше, символьные биты символа, соответствующего любой из 64 сигнальных точек, определенных 64QAM, чередуются со знаковыми битами кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 7/15, и код LDPC после взаимной замены декодируют на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 12 битов, сохраненных в этих 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, (#i+1)-й бит из старших значащих битов знаковых битов 12 битов установлен в качестве бита b#i, (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов установлен в качестве бита y#i, и биты y2, y0, y8, y7, y1, y6, y4, y3, y10, y9, y5 и y11 взаимно заменяют на биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11, соответственно. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Способ обработки данных/устройство обработки данных в соответствии с шестым аспектом настоящей технологии, представляют собой устройство/способ обработки данных, включающие в себя модуль/этап обратной взаимной замены, который выполняет взаимную замену символьных битов, соответствующего любой из 64 сигнальных точек, определенных 64QAM, на знаковые биты кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, и модуль/этап декодирования, который декодирует код LDPC, после взаимной замены, выполненной модулем/этапом обратной взаимной замены, на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 12 битов, сохраненных в 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, модуль/этап обратной взаимной замены устанавливает (#i+1)-й бит из старших значащих битов знаковых битов 12 битов в качестве бита b#i и (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов в качестве бита y#i, и выполняет взаимную замену битов y2, y0, y4, y1, y6, y7, y8, y5, y10, y3, y9 и y11 на биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11, соответственно. Код LDPC включает в себя информационные биты и биты четности. Матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

В шестом аспекте, описанном выше, символьные биты символа, соответствующего любой из 64 сигнальных точек, определенных 64QAM, чередуются со знаковыми битами кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования равна 8/15, и код LDPC после взаимной замены декодируют на основе матрицы проверки на четность кода LDPC. Когда знаковые биты 12 битов, сохраненных в этих 12 модулях хранения, имеющих емкость хранения 16200/12 битов и считываемых из соответствующих модулей хранения по одному биту одновременно, выделяют для двух последовательных символов, при этом (#i+1)-й бит из старших значащих битов знаковых битов 12 битов установлен в качестве бита b#i, a (#i+1)-й бит из старших значащих битов символьных битов 12 битов этих двух символов установлен в качестве бита y#i, и биты y2, y0, y4, y1, y6, y7, y8, y5, y10, y3, y9 и y11 взаимно заменяют на биты b0, b1, b2, b3, b4, b5, b6, b7, b8, b9, b10 и b11, соответственно. Код LDPC включает в себя информационные биты и биты четности, матрица проверки на четность включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности, область информационной матрицы представлена таблицей исходного значения матрицы проверки на четность, и таблица исходного значения матрицы проверки на четность представляет собой таблицу, которая представляет положения элементов 1 на участке информационной матрицы для каждых 360 столбцов, и выполнена следующим образом:

Устройство обработки данных может представлять собой независимое устройство и может представлять собой внутренний блок, состоящий из одного устройства.

Эффекты изобретения

В соответствии с настоящей технологией, может быть повышена устойчивость к ошибке.

Краткое описание чертежей

На фиг.1 показана схема, иллюстрирующая матрицу проверки на четность Н кода LDPC.

На фиг.2 показана блок-схема последовательности операций, иллюстрирующая последовательность декодирования кода LDPC.

На фиг.3 показана схема, иллюстрирующая пример матрицы проверки на четность кода LDPC.

На фиг.4 показана схема, иллюстрирующая граф Таннера матрицы проверки на четность.

На фиг.5 показана схема, иллюстрирующая переменный узел.

На фиг.6 показана схема, иллюстрирующая проверочный узел.

На фиг.7 показана схема, иллюстрирующая пример конфигурации варианта осуществления передающей системы, в которой применена настоящая технология.

На фиг.8 показана схема, иллюстрирующая пример конфигурации устройства 11 передачи данных.

На фиг.9 показана схема, иллюстрирующая пример конфигурации перемежителя 116 битов.

На фиг.10 показана схема, иллюстрирующая матрицу проверки на четность.

На фиг.11 показана схема, иллюстрирующая матрицу четности.

На фиг.12 показана схема, иллюстрирующая матрицу проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

На фиг.13 показана схема, иллюстрирующая матрицу проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

На фиг.14 показана схема, иллюстрирующая компоновку сигнальных точек 16QAM.

На фиг.15 показана схема, иллюстрирующая компоновку сигнальных точек 64QAM.

На фиг.16 показана схема, иллюстрирующая компоновку сигнальных точек 64QAM.

На фиг.17 показана схема, иллюстрирующая компоновку сигнальных точек 64QAM.

На фиг.18 показана схема, иллюстрирующая обработку демультиплексора 25.

На фиг.19 показана схема, иллюстрирующая обработку демультиплексора 25.

На фиг.20 показана схема, иллюстрирующая граф Таннера для декодирования кода LDPC.

На фиг.21 показана схема, иллюстрирующая матрицу четности HT, которая становится ступенчатой структурой, и графом Таннера, соответствующим матрице четности HT.

На фиг.22 показана схема, иллюстрирующая матрицу четности HT матрицы проверки на четность Н, соответствующей коду LDPC после перемежения четности.

На фиг.23 показана схема, иллюстрирующая матрицу преобразования проверки на четность.

На фиг.24 показана схема, иллюстрирующая обработку перемежителя 24 со скручиванием столбцов.

На фиг.25 показана схема, иллюстрирующая номер столбца запоминающего устройства 31, необходимый для перемежения со скручиванием столбцов, и адрес положения начала записи.

На фиг.26 показана схема, иллюстрирующая номер столбца запоминающего устройства 31, необходимый для перемежения со скручиванием столбцов, и адрес положения начала записи.

На фиг.27 показана блок-схема последовательности операций, иллюстрирующая обработку, выполняемую перемежителем 116 бита, и кодером 117 QAM.

На фиг.28 показана схема, иллюстрирующая модель канала передачи данных, принятая при моделировании.

На фиг.29 показана схема, иллюстрирующая соотношение частоты ошибок, полученной при моделировании, и частоты Допплера fd дрожания.

На фиг.30 показана схема, иллюстрирующая соотношение частоты ошибок, полученной при моде