Устройство обработки данных и способ обработки данных

Иллюстрации

Показать всеИзобретение относится к устройствам и способам обработки данных. Технический результат - повышение устойчивости к ошибкам данных. Для этого когда заданный код LDPC (проверки четности с низкой плотностью), имеющий длину кода 16200 битов и скорость кода равную 8/15, отображают на 256 точек сигналов, при этом (#i+1)-ый бит, отсчитанный от самого верхнего бита из 8×1 знаковых битов, a (#i+1)-ый бит, отсчитанный от самого верхнего бита из 8×1 символьных битов одного символа выражены в качестве бита b#i и бита y#i соответственно, причем демультиплексор выполнен с возможностью перестановки для назначения бита b0 в качестве бита y2, бита b1 в качестве бита y6, бита b2 в качестве бита y1, бита b3 в качестве бита y0, бита y4 в качестве бита y7, бита b5 в качестве бита y5, бита b6 в качестве бита y3 и бита b7 в качестве бита y4. Настоящая технология может применяться, например, в системах передачи, которые передают коды LDPC. 4 н.п. ф-лы, 75 ил.

Реферат

Область техники, к которой относится изобретение

Настоящая технология относится к устройствам обработки данных и способам обработки данных, и, более конкретно, к устройству обработки данных и способу обработки данных, которые позволяют улучшить, например, устойчивость к ошибкам данных.

Уровень техники

Коды LDPC (проверки четности с низкой плотностью) имеют высокие возможности по коррекции ошибок, и в настоящее время их начинают широко использовать в системах передачи данных, включающих в себя цифровую спутниковую широковещательную передачу, такую как DVB (цифровая широковещательная передача видеоданных)-S.2, которая воплощена, например в Европе (см., например, непатентный документ 1). Кроме того, рассматривается использование кодов LDPC при наземной цифровой широковещательной передаче следующего поколения.

Последние исследования показали, что коды LDPC, имеющие большую длину кода, обладают возможностями, приближающимися к пределу Шеннона, такими, как у турбокода и т.п. Кроме того, код LDPC отличается тем, что минимальное расстояние пропорционально его длине кода. Учитывая это, особенности кода LDPC имеют преимущества, состоящие в том, что вероятность ошибки блока является высокой, и мало вероятно возникают, так называемые, явления минимального уровня ошибок, которые наблюдают в характеристиках декодирования турбокодов и т.п.

Такие коды LDPC подробно описаны ниже. Коды LDPC представляют собой линейные коды, и не обязательно двоичные коды. В этом описании, однако, коды LDPC описаны, как двоичные коды.

Наиболее существенная особенность кода LDPC состоит в том, что матрица проверки четности, определяющая код LDPC, является разреженной. Здесь разреженная матрица представляет собой матрицу, которая имеет очень малое количество элементов матрицы, равных "1" (или матрицу, в которой большинство элементов равно "0").

На фиг.1 показан пример матрицы Н проверки четности кода LDPC.

В матрице Н проверки четности, показанной на фиг.1, вес каждого столбца.(вес столбца) (количество элементов равных "1") равен "3", и вес каждой строки (вес строки) равен "6".

При кодировании, когда используется код LDPC (кодирование LDPC), генерируют порождающую матрицу G, например, на основе матрицы Н проверки четности, и порождающую матрицу G умножают на двоичные информационные биты для генерирования кодового слова (кода LDPC).

В частности, устройство кодирования, которое выполняет кодирование LDPC, вначале вычисляет такую порождающую матрицу G, чтобы она удовлетворяла уравнению GHT=0, в отношении транспонированной матрицы HT матрицы Н проверки четности. Здесь, если порождающая матрица G представляет собой матрицу K×N, устройство кодирования умножает порождающую матрицу G на строку битов (вектор u) из информационных битов, состоящих из К битов, для генерирования кодового слова с (=uG), состоящего из N битов. Кодовое слово (код LDPC), генерируемое устройством кодирования, принимают на стороне приема через заданный канал.

Декодирование кода LDPC может быть выполнено путем использования алгоритма пропуска сообщений, который представляет собой алгоритм, рассматриваемый, как вероятностное декодирование Галлагера, и основано на распространении степени уверенности в, так называемом, графе Таннера, сформированном с переменными узлами (также называются узлами сообщения) и узлами проверки. Ниже переменные узлы и узлы проверки также, соответственно, называются просто узлами.

На фиг.2 показаны процедуры для декодирования кода LDPC.

Следует отметить, что реальное значение (LLR приема), представляющее логарифм отношения вероятности указывающей вероятность того, что значение i-ого знакового бита в коде LDPC (одно кодовое слово), принятом на стороне приема, равно "0", также будет называться принятым значением u0i в соответствующих случаях. Кроме того, сообщение, которое выводят от узла проверки, представлено, как uj, и сообщение, которое выводят от переменного узла, представлено, как vi.

Вначале, при декодировании кода LDPC, как показано на фиг.2, код LDPC принимают на этапе S11. Сообщение (сообщение узла проверки) uj инициируют, делая равным "0", и переменную k, которая представляет собой целое число, как периодически повторяющийся счетчик обработки, инициируют, сбрасывая в "0". Операция затем переходит на этап S12. На этапе S12, на основе принятого значения u0i, полученного в результате приема кода LDPC, выполняют вычисление, показанное в уравнении (1) (вычисление переменного узла), для определения сообщения (сообщение переменного узла) vi. Кроме того, на основе сообщения vi, выполняют вычисление (вычисление узла проверки), показанное в уравнении (2), для определения сообщения uj.

[Математическая формула 1]

[Математическая Формула 2]

В уравнении (1) и в уравнении (2), dv и dc представляют параметры, которые могут быть произвольно выбраны и представляют количество элементов, равных "1", в вертикальном направлении (в столбце) и в горизонтальном направлении (строке) в матрице Н проверки четности, соответственно. В случае кода (3, 6), например, dv равен 3, и dc равен 6.

При вычислении переменного узла, показанного в уравнении (1), и при вычислении узла проверки, показанного в уравнении (2), сообщения, которые вводят от ребер (линии, каждая из которых соединяет переменный узел и проверочный узел), которые готовы для вывода сообщений, не подвергают вычислениям. Поэтому, диапазон вычислений составляет от 1 до dv-1 или от 1 до dc-1. На практике, вычисление проверочного узла, показанное в уравнении (2), выполняют путем подготовки заранее таблицы функции R (v1, v2) показанной в уравнении (3), определенной одним выходом для двух входных данных v1 и v2, и постоянно (рекурсивно) используя таблицу, как показано в уравнении (4).

[Математическая формула 3]

[Математическая формула 4]

Кроме того, на этапе S12, выполняют последовательное приращение переменной к только на "1", и операция затем переходит на этап S13. На этапе S13 выполняют проверку для определения, превышает ли переменная k заданное число С повторений декодирования. Если определяют, что переменная k не больше, чем С на этапе S13, операция возвращается на этап S12, и повторяют те же процедуры, как описаны выше.

Если определяют, что переменная k больше, чем С на этапе S13, операция переходит на этап S14, и вычисление, показанное в уравнении (5), выполняют для определения сообщения vi, в качестве результата декодирования, который должен быть выведен в конечном итоге. Сообщение vi затем выводят, и операция декодирования кода LDPC подходит к концу.

[Математическая формула 5]

Здесь вычисление, показанное в уравнении (5), выполняют, используя сообщения uj от всех ребер, соединенных с переменными узлами, в отличие от вычисления переменного узла, показанного в уравнении (1).

На фиг.3 показан пример матрицы Н проверки четности кода LDPC (3, 6) (скорость кода 1/2, длина кода 12).

В матрице Н проверки четности, показанной на фиг.3, вес столбца равен 3, и вес строки равен 6, как и в случае, представленном на фиг.1.

На фиг.4 показан граф Таннера матрицы Н проверки четности, показанной на фиг.3.

На фиг.4 каждый "+" представляет проверочный узел, и каждый "=" представляет переменный узел. Проверочные узлы и переменные узлы соответствуют строкам и столбцам, соответственно, матрицы Н проверки четности. Соединительные линии между проверочными узлами и переменными узлами представляют собой ребра, и они эквивалентны элементам "1" матрицы проверки четности.

В частности, когда элемент в j-ой строке и i-ом столбце в матрице проверки четности равен 1, переменный узел (представленный знаком "-"), то есть, i-ый сверху, и проверочный узел (представленный "+"), то есть, j-ый сверху, соединены ребром на фиг.4. Ребро указывает, что знаковый бит, соответствующий переменному узлу, имеет ограничение, соответствующее проверочному узлу.

В соответствии с алгоритмом "сумма-произведение", который представляет собой способ декодирования кодов LDPC, вычисление переменного узла и вычисление проверочного узла выполняют многократно.

На фиг.5 показано вычисление переменного узла, который выполняют в переменном узле.

В переменном узле сообщение vi, соответствующее ребру, которое должно быть вычислено, может быть определено путем вычисления переменного узла, показанного в уравнении (1), используя сообщения u1 и u2 из остальных ребер, соединенных с переменным узлом, и принятое значение u0i. Сообщение, соответствующее любому из других ребер, может быть определено так же, как и представлено выше.

На фиг.6 показано вычисление проверочного узла, выполняемого в проверочном узле.

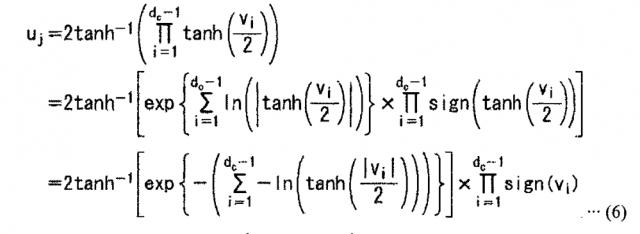

Вычисление проверочного узла, показанное в уравнении (2), также может быть выражено уравнением (6), используя взаимозависимость, выраженную уравнением a×b={ln(|a|)+ln(|b|)}×знак (а)×знак (b). Здесь, знак (x) равен 1, когда х≥0, и равен -1, когда х<0.

[Математическая формула 6]

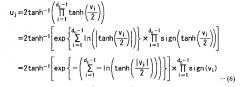

Когда х≥0, уравнение, φ-1(х)=2tanh-1(е-x), удовлетворяется, где функция φ(х) определена, как φ(х)=ln(tanh(х/2)). В соответствии с этим, уравнение (6) может быть преобразовано в уравнение (7).

[Математическая формула 7]

В проверочном узле вычисление проверочного узла, показанного в уравнении (2), выполняют в соответствии с уравнением (7).

В частности, в проверочном узле, сообщение uj, соответствующее ребру, которое должно быть вычислено, может быть определено путем вычисления проверочного узла, показанного в уравнении (7), используя сообщения v1, v2, v3, v4 и v5 от других ребер, соединенных с проверочным узлом, как показано на фиг.6. Сообщение, соответствующее любому из других ребер, может быть определено так же, как описано выше.

Следует отметить, что функция φ(х) в уравнении (7) может быть выражена уравнением φ(х)=ln((ex+1)/(ех-1)), и φ(х)=φ-1(х) удовлетворяется, когда х>0. Когда функцию φ(х) и φ-1(х) воплощают в аппаратных средствах, можно использовать LUT (справочные таблицы), но обе таблицы представляют собой идентичные LUT.

Список литературы

Непатентный документ

НЕПАТЕНТНЫЙ ДОКУМЕНТ 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Задачи, решаемые изобретением

Коды LDPC используются в DVB-S.2, которые представляют собой стандарты для цифровой спутниковой широковещательной передачи, и в DVB-T.2, которые представляют собой стандарты для цифровой наземной широковещательной передачи. Коды LDPC также планируются использовать в DVB-C.2, которые представляют собой стандарты для следующего поколения цифровой широковещательной передачи CATV (кабельного телевидения).

При цифровой широковещательной передаче, в соответствии со стандартами DVB, такими как DVB-S.2, код LDPC преобразуют (символизируют) в символы ортогональной модуляции (цифровая модуляция), такой как QPSK (квадратурная манипуляция со сдвигом фазы) и передают символы, отображенные на точки сигнала.

При выражении символами кода LDPC знаковые биты кода LDPC переставляют по два или больше знаковых бита одновременно, и переставленные знаковые биты используются в качестве символьных битов.

Существуют различные виды способов, предполагаемых, в качестве способов перестановки знаковых битов, для выражения кодов LDPC в виде символов, и некоторые из них, например, установлены в DVB-T.2.

В то же время, DVB-T.2 представляют собой стандарты для цифровой широковещательной передачи, предназначенной для фиксированных оконечных устройств, таких как телевизионные приемники, установленные в домах, и могут быть не пригодны для цифровой широковещательной передачи, предназначенной для портативных оконечных устройств.

В частности, портативные оконечные устройства должны иметь меньшие размеры схемы, чем стационарные оконечные устройства, и должны быть разработаны для потребления меньшей энергии. Поэтому, для уменьшения нагрузки, требуемой при выполнении операций, таких как декодирование кодов LDPC в каждом портативном оконечном устройстве при цифровой широковещательной передаче для портативных оконечных устройств, количество повторений при декодировании (количество С повторений при декодировании) каждого кода LDPC, длина кода каждого кода LDPC и т.п. могут быть ограничены меньшими значениями, чем в случае цифровой широковещательной передачи для стационарных оконечных устройств.

При таких ограничениях, все еще требуется поддерживать определенный уровень устойчивости к ошибкам.

Настоящая технология была разработана с учетом таких обстоятельств, и предназначена для обеспечения для данных, таких как коды LDPC, более высокой устойчивости к ошибкам.

Решение задач

Устройство/способ обработки данных, в соответствии с первым аспектом настоящей технологии, включает в себя: модуль/этап кодирования для кодирования LDPC для генерирования кода LDPC, имеющего длину кода 16200 битов, и скорость кода 8/15, на основе матрицы проверки четности для кодов LDPC; и модуль/этап перестановки для смены мест знаковых битов кода LDPC, кодированного в модуле/на этапе кодирования с символьными битами для символа, соответствующего одной из 256 точек сигнала, определенных по 256QAM. Код LDPC, кодированный в модуле/на этапе кодирования, включает в себя информационные биты и биты проверки четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок матрицы проверки четности, соответствующий битам проверки четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

В модуле/на этапе перестановки заменяют бит b0 битом y2, бит b1 битом y6, бит b2 битом y1, бит b3 битом y0, бит b4 битом y7, бит b5 битом y5, бит b6 битом y3 и бит b7 битом y4, где восьми знаковым битам, которые содержатся в восьми модулях хранения, каждый из которых имеет емкость 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому назначают один символ, при этом (#i+1)-ый бит, считая от самого верхнего бита из восьми знаковых битов, выражается, как бит b#i, и (#i+1)-ый бит, содержащийся в самом верхнем бите из восьми символьных битов одного символа, выражен как бит y#i.

В описанном выше первом аспекте кодирование LDPC для генерирования кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15, выполняют на основе матрицы проверки четности для кодов LDPC, и знаковые биты кода LDPC заменяют символьными битами символа, соответствующего одной из 256 точек сигнала, определенных 256QAM. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" информационного участка матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

В случае, когда восемь знаковых битов, которые сохранены в восьми модулях хранения, каждый из которых имеет емкость хранения 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому назначают один символ, (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми знаковых битов, выражается в качестве бита b#i, и (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми символьных битов для одного символа, выражается в качестве бита y#i, причем бит b0 заменяют битом y2, бит b1 заменяют битом y6, бит b2 заменяют битом y1, бит b3 заменяют битом y0, бит b4 заменяют битом y7, бит b5 заменяют битом y5, бит b6 заменяют битом y3 и бит b7 заменяют битом y4.

Устройство/способ обработки данных, в соответствии со вторым аспектом настоящей технологии, включает в себя: модуль/этап обратной перестановки для замены символьных битов символа, соответствующего одной из 256 точек сигнала, определенных 256QAM, знаковыми битами кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15; и модуль/этап декодирования для декодирования кода LDPC на основе матрицы проверки четности для кодов LDPC после перестановки кода LDPC модулем/этапом обратной перестановки. Модуль/этап обратной перестановки заменяет бит y2 битом b0, бит y6 битом b1, бит y1 битом b2, бит y0 битом b3, бит y7 битом b4, бит y5 битом b5, бит y3 битом b6 и бит y4 битом b7, где восемь знаковых битов содержатся в восьми модулях хранения, каждый из которых имеет емкость хранения 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому из которых назначен один символ, (#i+1)-ый бит, отсчитанный от самого верхнего бита из восьми знаковых битов, выражен в качестве бита b#i, и (#i+1)-ый бит, отсчитанный от верхнего бита из восьми символьных битов одного символа, выражен в качестве бита y#i. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы через интервалы 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

В описанном выше втором аспекте символьные биты символа, соответствующего одной из 256 точек сигнала, определенных 256QAM, заменяют знаковыми битами кода LDPC, имеющего длину кода 16200 битов и скорость кода 8/15, и переставленный код LDPC декодируют на основе матрицы проверки четности для кодов LDPC. Модуль/этап обратной перестановки заменяет бит y2 битом b0, бит y6 битом b1, бит y1 битом b2, бит y0 битом b3, бит y7 битом b4, бит y5 битом b5, бит y3 битом b6 и бит y4 битом b7, где восемь знаковых битов содержатся в восьми модулях хранения, каждый из которых имеет емкость 16200/8 битов, и которые считывают из соответствующих модулей хранения по одному биту, каждому из которых назначен один символ, (#i+1)-й бит, отсчитанный от верхнего бита из этих восьми знаковых битов, выражен в качестве бита b#i, и (#i+1)th бит, отсчитанный от верхнего бита из восьми символьных битов одного символа, выражен в качестве бита y#i. Код LDPC включает в себя информационные биты и биты четности, и матрица проверки четности включает в себя информационный участок матрицы, соответствующий информационным битам, и участок четности матрицы, соответствующий битам четности. Информационный участок матрицы представлен таблицей исходного значения матрицы проверки, и таблица исходного значения матрицы проверки представляет собой таблицу, которая представляет положения элементов "1" участка информационной матрицы с промежутками в 360 столбцов, и содержит

32 384 430 591 1976 1296 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1461 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464

Устройство обработки данных может представлять собой независимое устройство, или может представлять собой внутренний блок в отдельном устройстве.

Эффекты изобретения

В соответствии с настоящей технологией, может быть повышена устойчивость к ошибкам.

Краткое описание чертежей

На фиг.1 показана схема для пояснения матрицы Н проверки четности кода LDPC.

На фиг.2 блок-схема последовательности операций для пояснения процедуры декодирования кода LDPC.

На фиг.3 показана схема, представляющая пример матрицы проверки четности кода LDPC.

На фиг.4 показана схема, представляющая граф Таннера матрицы проверки четности.

На фиг.5 показана схема, представляющая переменный узел.

На фиг.6 показана схема, представляющая проверочный узел.

На фиг.7 показана схема, представляющая пример структуры варианта осуществления системы передачи, к которой применена настоящая технология.

На фиг.8 показана блок-схема, представляющая пример структуры устройства 11 передачи.

На фиг.9 показана блок-схема, представляющая пример структуры перемежителя 116 битов.

На фиг.10 показана схема, представляющая матрицу проверки четности.

На фиг.11 показана схема, представляющая матрицу четности.

На фиг.12 показана схема для пояснения матрицы проверки четности кода LDPC, определенного в стандартах DVB-S.2.

На фиг.13 показана схема для пояснения матрицы проверки четности кода LDPC, определенного в стандартах DVB-S.2.

На фиг.14 показана схема, представляющая компоновку точки сигнала 16QAM.

На фиг.15 показана схема, представляющая компоновку точки сигнала 64QAM.

На фиг.16 показана схема, представляющая компоновку точки сигнала 64QAM.

На фиг.17 показана схема, представляющая компоновку точки сигнала 64QAM.

На фиг.18 показана схема для пояснения операции демультиплексора 25.

На фиг.19 показана схема для пояснения операции демультиплексора 25.

На фиг.20 показана схема, представляющая граф Таннера для декодировании кода LDPC.

На фиг.21 показана схема, представляющая матрицу HT четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT четности.

На фиг.22 показана схема, представляющая матрицу HT четности матрицы Н проверки четности, соответствующую коду LDPC, подвергнутому перемежению четности.

На фиг.23 показана схема, представляющая преобразованную матрицу проверки четности.

На фиг.24 показана схема для пояснения операция перемежителя 24 со скручиванием столбцов.

На фиг.25 показана схема, представляющая заданное количество столбцов для перемежения со скручиванием столбцов в запоминающем устройстве 31, и адреса положений начала записи.

На фиг.26 показана схема, представляющая требуемое количество столбцов для перемежения со скручиванием столбцов в запоминающем устройстве 31, и адреса положений начала записи.

На фиг.27 показана блок-схема последовательности операций для пояснения операций, которые будут выполнены в перемежителе 116 битов и кодере 117 QAM.

На фиг.28 показана схема, представляющая модель канала, используемого при моделировании.

На фиг.29 показана схема, представляющая взаимосвязь между частотами ошибки, полученными при моделировании, и частотой Допплера дрожания.

На фиг.30 показана схема, представляющая взаимосвязь между скоростями ошибки, полученными при моделировании, и частотой fa Допплера дрожания.

На фиг.31 показана блок-схема, представляющая пример структуры кодера 115 LDPC.

На фиг.32 показана блок-схема последовательности операций для пояснения операции кодера для кодера 115.

На фиг.33 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/4 и длины кода 16200.

На фиг.34 показана схема, представляющая способ определения матрицы Н проверки четности из таблицы исходного значения матрицы проверки.

На фиг.35 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/5 и длины кода 16200.

На фиг.36 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 4/15 и длины кода 16200.

На фиг.37 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 1/3 и длины кода 16200.

На фиг.38 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 2/5 и длины кода 16200.

На фиг.39 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 4/9 и длины кода 16200.

На фиг.40 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 7/15 и длины кода 16200.

На фиг.41 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 8/15 и длины кода 16200.

На фиг.42 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 3/5 и длины кода 16200.

На фиг.43 показана схема, представляющая пример таблицы исходного значения матрицы проверки для кодовой скорости 2/3 и длины кода 16200.

На фиг.44 показана схема, представляющая пример графа Таннера совокупности в порядке последовательности, в которой вес столбца равен 3, и вес строки равен 6.

На фиг.45 показана схема, представляющая пример графа Таннера совокупности многореберного типа.

На фиг.46 показана схема, представляющая минимальные длины цикла и пороговые значения рабочей характеристики матриц проверки четности кодов LDPC, имеющих длину кода 16200.

На фиг.47 показана схема для пояснения матрицы проверки четности кода LDPC, имеющего длину кода 16200.

На фиг.48 показана схема для пояснения матрицы проверки четности кода LDPC, имеющего длину кода 16200.

На фиг.49 показана схема, представляющая результаты моделирования, выполненного для измерения BER кодов LDPC, имеющих длину кода 16200.

На фиг.50 показана схема для пояснения операции перестановки в соответствии с существующими способами.

На фиг.51 показана схема для пояснения операции перестановки в соответствии с существующими способами.

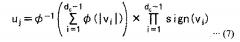

На фиг.52 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15 модулирован 256QAM, и кратное число b равно 1.

На фиг.53 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15 модулирован 256QAM, и кратное число b равно 1.

На фиг.54 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 4/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.55 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.56 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.57 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 7/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.58 показана схема, представляющая группы знаковых битов и группы символьных битов в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 2560AM, и кратное число b равно 1.

На фиг.59 показана схема, представляющая правило назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.60 показана схема, представляющая перестановку знакового бита в соответствии с правилом назначения в случаях, когда код LDPC, имеющий длину кода 16200 и скорость кода 8/15, модулирован 256QAM, и кратное число b равно 1.

На фиг.61 показана блок-схема, представляющая пример структуры устройства приема 12.

На фиг.62 показана блок-схема, представляющая пример структуры обратного перемежителя 165 битов.

На фиг.63 показана блок-схема последовательности операций для пояснения операций, выполняемых декодером QAM 164, обратным перемежителем 165 битов и декодером 166 LDPC.

На фиг.64 показана схема, представляющая пример матрицы проверки четности кода LDPC.

На фиг.65 показана схема, представляющая матрицу (преобразованную матрицу проверки четности), полученную путем выполнения замены строки и замены столбца в матрице проверки четности.

На фиг.66 показана схема, представляющая преобразованную матрицу проверки четности, разделенную на модули 5×5.

На фиг.67 показана блок-схема, представляющая пример структуры устройства декодирования, которое совместно выполняет Р вычислений узла.

На фиг.68 показана блок-схема, представляющая пример структуры декодера 166 LDPC.

На фиг.69 показана схема для пояснения операции мультиплексора 54 обратного перемежителя 165 бита.

На фиг.70 показана схема для пояснения операции обратного перемежителя 55 со скручиванием столбцов.

На фиг.71 показана блок-схема, представляющая другую примерную структуру обратного перемежителя 165 битов.

На фиг.72 показана блок-схема, представляющая первую примерную структуру системы приема, в которой может быть применено устройство 12 приема.

На фиг.73 показана блок-схема, представляющая вторую примерную структуру системы приема, в которой может быть применено устройство 12 приема.

На фиг.74 показана блок-схема, представляющая третью примерную структуру системы приема, в которой может быть применено устройство 12 приема.

На фиг.75 показана блок-схема, представляющая пример структуры варианта осуществления компьютера, в котором применена настоящая технология.

Подробное описание изобретения

Пример структуры системы передачи, в которой применяется настоящая технология

На фиг.7 показан пример структуры варианта осуществления системы передачи, в которой применяется настоящая технология ("система" означает логическую сборку устройств, и устройства, которые представляют данную структуру, не обязательно размещены в одном том же корпусе).

На фиг.7 показана система передачи, которая включает в себя устройство 11 передачи и устройство 12 приема.

Устройство 11 передачи выполняет передачу (широковещательную) (доставку) шоу, предназначенных для стационарных оконечных устройств и портативных оконечных устройств. В частности, устройство 11 передачи кодирует целевые данные передачи, такие, как данные изображения и аудиоданные, как шоу, предназначенные для стационарных оконечных устройств и портативных оконечных устройств, в коды LDPC, и передает эти коды LDPC через канал 13, например, по наземным волнам.

Устройство 12 приема представляет собой, например, портативное оконечное устройство. Устройство 12 приема принимает коды LDPC, переданные от устройства 11 передачи через канал 13, и декодирует коды LDPC в целевые данные перед выводом целевых данных.

Здесь коды LDPC, используемые в системе передачи, показанной на фиг.7, известны своей чрезвычайно высокой производительностью в каналах AWGN (аддитивный белый Гауссов шум).

Однако пакетные ошибки и удаления могут возникать в канале 13 наземных волн и т.п. Например, в системе OFDM (мультиплексирование с ортогональным разделением частоты) возникают моменты времени, когда мощность определенного символа становится равной нулю (удаление), в соответствии с задержкой эхо-сигнала (по-другому пути, чем основной путь) в среде с многолучевым распространением радиоволн, в которой D/U (отношение желательного/нежелательного) составляет 0 дБ (мощность нежелательного или эхо сигнала равна мощности желательного или сигнала в основном канале передачи).

Кроме того, когда D/U составляет 0 дБ, в случае дрожания сигнала (канал, в котором задержка равна нулю, и который имеет эхо-сигнал на Допплеровской частоте, добавленной к сигналу), мощность всех символов OFDM в определенные моменты времени может становиться равной нулю (удаление) из-за Допплеровской частоты.

Кроме того, на стороне устройства 12 приема, в некоторых случаях, пакетные ошибки возникают, из-за условий на линии от модуля приема (не показан), такого как антенна, которая принимает сигналы от устройства 11 передачи, до устройства 12 приема, и нестабильности источника питания устройства 12 приема.

При декодировании кода LDPC, с другой стороны, в строке матрицы Н проверки четности или в переменном узле, соответствующем знаковому биту кода LDPC, вычисление переменного узла, показанного в уравнении (1), включающее в себя добавление (принятого значения u0i для) знакового бита кода LDPC, выполняют, как уже описано со ссылкой на фиг.5. Поэтому, если возникает ошибка в знаковом бите, используемом при вычислении переменного узла, ухудшается точность получаемого в результате сообщения.

При декодировании кода LDPC вычисление проверочного узла, показанного в уравнении (7), выполняют в проверочном узле, используя сообщения, определенные в переменных узлах, подключенных к проверочному узлу. Поэтому, если количество проверочных узлов, которое приводит к появлению одновременных ошибок (включая в себя стирания) в подключенных переменных узлах (или в знаковых битах кодов LDPC, соответствующих переменным узлам), становится большим, характеристики декодирования ухудшаются.

Таким образом, когда одновременно возникает удаление в двух или больше переменных узлах, подключенных к проверочному узлу, проверочный узел возвращает во все переменные узлы сообщение, указывающее, что вероятность того, что значения равны "0", и вероятность того, значения равны "1", равны друг другу. В этом случае, проверочный узел, который возвращает сообщение, указывающее равные вероятности, не способствует одной из операции декодирования (один набор вычислений переменного узла и вычислений проверочного узла). В результате, количество повторений операции декодирования должно быть увеличено, и характеристики декодирования ухудшаются. Кроме того, увеличивается потребление энергии устройством 12 приема, которое декодирует коды LDPC.

С учетом этого, система передачи данных, показанная на фиг.7, улучшает устойчивость к пакетным ошибкам и удалениям при поддержании высоких рабочих характеристик в каналах AWGN.

Пример структуры устройства 11 передачи

На фиг.8 показана блок-схема, представляющая пример структуры устройства 11 передачи, показанного на фиг.7.

В устройстве 11 передачи один или более входных потоков, как целевые данные, подают на модуль 111 адаптации режима/мультиплексора.

Модуль 111 адаптации режима/мультиплексора выполняет выбор режима и мультиплексирует один или более входных потоков, подаваемых на него. Полученные в результате данные подают на заполнитель 112.

Заполнитель 112 выполняет необходимое заполнение нулями (