Быстродействующий операционный усилитель на основе "перегнутого" каскода

Иллюстрации

Показать всеИзобретение относится к области радиоэлектроники в качестве быстродействующего устройства усиления сигналов. Технический результат заключается в обеспечении более высоких уровней выходного тока «перегнутого каскода», это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса. Усилитель содержит входные полевые транзисторы, токостабилизирующий двухполюсник, выходной транзистор, которые подключены к входному полевому транзистору, причем первый выходной транзистор через токостабилизирующий двухполюсник связан со второй шиной источника питания, второй выходной транзистор соединен с первым входным полевым транзистором и через третий токостабилизирующий двухполюсник связан со второй шиной источника питания, цепь динамической нагрузки, согласованную с первой шиной источника питания. В схему введены дополнительные полевые транзисторы, дополнительные биполярные транзисторы. 4 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве быстродействующего устройства усиления сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе архитектуры «перегнутого каскода» [1-14]. Их основные достоинства - расширенный частотный диапазон, а также эффективное использование напряжения питания.

Для работы в условиях космического пространства, в экспериментальной физике необходимы радиационно-стойкие ОУ с малым напряжением смещения нуля (Uсм) и повышенным быстродействием. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [15], обеспечивающего формирование p-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [15].

Как показано в работах авторов [16-18], быстродействие классических операционных усилителей с однополюсной частотной коррекцией определяется диапазоном активной работы входного каскада (напряжением ограничения Uгр). Для увеличения максимальной скорости выходного напряжения ОУ с классической архитектурой (ϑвых), как правило, предусматриваются специальные цепи нелинейной коррекции, обеспечивающей в режиме динамической перегрузки входного каскада ОУ большие уровни выходных токов. Это способствует более быстрому перезаряду корректирующей емкости ОУ [16-18]. Однако для ОУ на основе «перегнутых каскодов» такие цепи не разработаны. Данная задача решается в предлагаемом ниже схемотехническом решении.

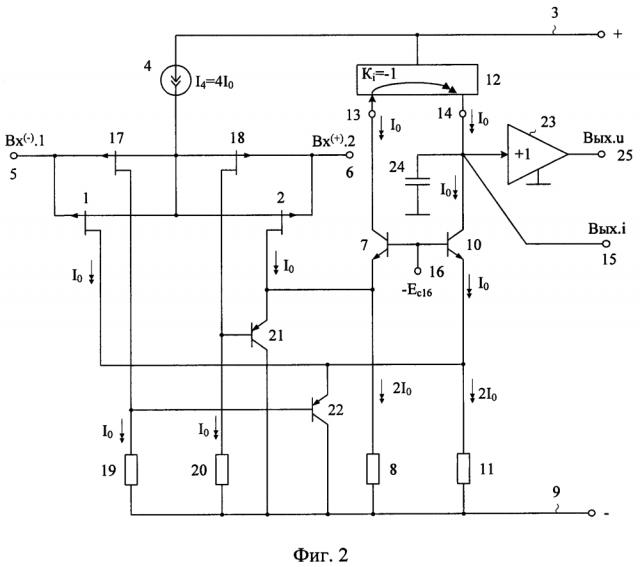

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 7.215.200, fig. 6. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых подключены к первой 3 шине источника питания через первый 4 токостабилизирующий двухполюсник, первый 5 вход устройства, связанный с затвором первого 1 входного полевого транзистора, второй 6 вход устройства, связанный с затвором второго 2 входного полевого транзистора, первый 7 выходной транзистор, эмиттер которого подключен к стоку второго 2 входного полевого транзистора и через второй 8 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, второй 10 выходной транзистор, эмиттер которого соединен со стоком первого 1 входного полевого транзистора и через третий 11 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, цепь динамической нагрузки 12, согласованную с первой 3 шиной источника питания, вход которой 13 соединен с коллектором первого 7 выходного транзистора, а выход 14 связан с выходом устройства 15 и коллектором второго 10 выходного транзистора, причем базы первого 7 и второго 10 выходных транзисторов соединены с источником напряжения смещения 16.

Существенный недостаток известного ОУ состоит в том, что его максимальный выходной ток в режиме динамической перегрузки входного каскада жестко связан со статическим током первого 7 и второго 10 выходных транзисторов. Это не позволяет осуществить быстрый перезаряд корректирующего конденсатора на выходе ОУ, что ограничивает его максимальную скорость нарастания выходного напряжения [16-18].

Основная задача предлагаемого изобретения состоит в обеспечении более высоких (чем статическое значение) уровней выходного тока «перегнутого каскода», что характерно для каскадов класса АВ. В конечном итоге это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса [16-18].

Поставленная задача достигается тем, что в операционном усилителе, фиг. 1, содержащем первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых подключены к первой 3 шине источника питания через первый 4 токостабилизирующий двухполюсник, первый 5 вход устройства, связанный с затвором первого 1 входного полевого транзистора, второй 6 вход устройства, связанный с затвором второго 2 входного полевого транзистора, первый 7 выходной транзистор, эмиттер которого подключен к стоку второго 2 входного полевого транзистора и через второй 8 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, второй 10 выходной транзистор, эмиттер которого соединен со стоком первого 1 входного полевого транзистора и через третий 11 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, цепь динамической нагрузки 12, согласованную с первой 3 шиной источника питания, вход которой 13 соединен с коллектором первого 7 выходного транзистора, а выход 14 связан с выходом устройства 15 и коллектором второго 10 выходного транзистора, причем базы первого 7 и второго 10 выходных транзисторов соединены с источником напряжения смещения 16, предусмотрены новые элементы и связи - в схему введены первый 17 и второй 18 дополнительные полевые транзисторы, истоки которых подключены к истокам первого 1 и второго 2 входных полевых транзисторов, затвор первого 17 дополнительного полевого транзистора соединен с первым 5 входом устройства, а затвор второго 18 дополнительного полевого транзистора соединен со вторым 6 входом устройства, сток первого 17 дополнительного полевого транзистора связан со второй 9 шиной источника питания через первый 19 дополнительный резистор, сток второго 18 дополнительного полевого транзистора связан со второй 9 шиной источника питания через второй 20 дополнительный резистор, эмиттер первого 7 выходного транзистора связан с эмиттером первого 21 дополнительного биполярного транзистора, база которого соединена со стоком второго 18 дополнительного полевого транзистора, а коллектор соединен со второй 9 шиной источника питания, эмиттер второго 10 выходного транзистора связан с эмиттером второго 22 дополнительного биполярного транзистора, база которого соединена со стоком первого 17 дополнительного полевого транзистора, а коллектор соединен со второй 9 шиной источника питания.

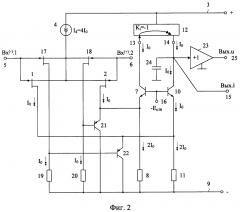

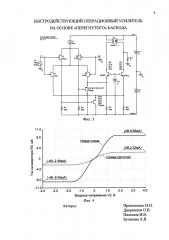

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

На фиг. 3 приведена схема заявляемого устройства в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

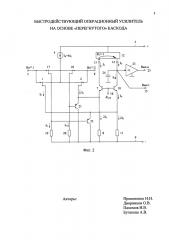

На фиг. 4 показана зависимость выходного тока «перегнутого» каскода от входного напряжения ОУ. Данный график показывает, что при выбранных параметрах элементов предлагаемая схема в режиме динамической перегрузки входного каскада обеспечивает почти в 4 раза больший выходной ток, что повышает быстродействие ОУ в типовых схемах его включения [16-18].

Быстродействующий операционный усилитель на основе «перегнутого» каскода, фиг. 2, содержит первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых подключены к первой 3 шине источника питания через первый 4 токостабилизирующий двухполюсник, первый 5 вход устройства, связанный с затвором первого 1 входного полевого транзистора, второй 6 вход устройства, связанный с затвором второго 2 входного полевого транзистора, первый 7 выходной транзистор, эмиттер которого подключен к стоку второго 2 входного полевого транзистора и через второй 8 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, второй 10 выходной транзистор, эмиттер которого соединен со стоком первого 1 входного полевого транзистора и через третий 11 токостабилизирующий двухполюсник связан со второй 9 шиной источника питания, цепь динамической нагрузки 12, согласованную с первой 3 шиной источника питания, вход которой 13 соединен с коллектором первого 7 выходного транзистора, а выход 14 связан с выходом устройства 15 и коллектором второго 10 выходного транзистора, причем базы первого 7 и второго 10 выходных транзисторов соединены с источником напряжения смещения 16. В схему введены первый 17 и второй 18 дополнительные полевые транзисторы, истоки которых подключены к истокам первого 1 и второго 2 входных полевых транзисторов, затвор первого 17 дополнительного полевого транзистора соединен с первым 5 входом устройства, а затвор второго 18 дополнительного полевого транзистора соединен со вторым 6 входом устройства, сток первого 17 дополнительного полевого транзистора связан со второй 9 шиной источника питания через первый 19 дополнительный резистор, сток второго 18 дополнительного полевого транзистора связан со второй 9 шиной источника питания через второй 20 дополнительный резистор, эмиттер первого 7 выходного транзистора связан с эмиттером первого 21 дополнительного биполярного транзистора, база которого соединена со стоком второго 18 дополнительного полевого транзистора, а коллектор соединен со второй 9 шиной источника питания, эмиттер второго 10 выходного транзистора связан с эмиттером второго 22 дополнительного биполярного транзистора, база которого соединена со стоком первого 17 дополнительного полевого транзистора, а коллектор соединен со второй 9 шиной источника питания.

В схеме фиг. 2 токовый выход 15 устройства связан со входом буферного усилителя 23 и корректирующим конденсатором 24. В этом случае потенциальный выход ОУ 25 может иметь малое выходное сопротивление.

Рассмотрим работу ОУ фиг. 2.

Статический режим транзисторов схемы фиг. 2 устанавливается первым 4 токостабилизирующим двухполюсником. При этом за счет выбора сопротивлений первого 19 и второго 20 дополнительных резисторов первый 21 и второй 22 дополнительные биполярные транзисторы закрыты (или работают в микрорежиме) и не влияют на работу схемы на малом сигнале.

При увеличении входного напряжения до уровня 0,5-1 В ток стока одного из дополнительных полевых транзисторов 17, 18 возрастает, а другого - уменьшается. В результате напряжение на базе первого 21 (или второго 22) дополнительного биполярного транзистора становится более близким к напряжению второй 9 шины источника питания. Это приводит к увеличению тока эмиттера первого 21 (или второго 22) дополнительного биполярного транзистора и, как следствие, создает дополнительное приращение тока на выходе 15. Как следствие, выходной ток низкоомной нагрузки R5 (фиг. 3) значительно превышает статические токи выходных транзисторов схемы фиг. 4. Это ускоряет процесс перезаряда корректирующего конденсатора 24 при импульсных входных сигналах ОУ, например в неинвертирующем включении.

Таким образом, выходной «перегнутый каскод» в предлагаемом ОУ работает в режиме класса АВ, что повышает быстродействие ОУ [16-18].

Заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню выходного тока в режиме динамической перегрузки входного каскада и, как следствие, максимальной скорости нарастания выходного напряжения замкнутого ОУ [16-18].

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.422.600, фиг. 2.

2. Патент США №4.406.990, фиг. 4.

3. Патент США №5.952.882.

4. Патент США №4.723.111.

5. Патент США №4.293.824.

6. Патент США №5.323.121.

7. Патент США №5.420.540, fig. 1.

8. Патент RU №2.354.041 C1.

9. Патентная заявка США №2003/0201828, fig. 1, fig. 2.

10. Патент США №6.825.721, fig. 1, fig. 2.

11. Патент США №6.542.030, fig. 1.

12. Патент US 6.456.162, fig. 2.

13. Патент US 6.501.333.

14. Патент US 6.717.466.

15. Элементная база радиационно-стойких информационно-измерительных систем: Монография. / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

16. Операционные усилители с непосредственной связью каскадов: Монография. / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

17. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: Монография. / Н.Н. Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. - 222 с.

18. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: Монография. / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

Быстродействующий операционный усилитель на основе «перегнутого» каскода, содержащий первый (1) и второй (2) входные полевые транзисторы, объединенные истоки которых подключены к первой (3) шине источника питания через первый (4) токостабилизирующий двухполюсник, первый (5) вход устройства, связанный с затвором первого (1) входного полевого транзистора, второй (6) вход устройства, связанный с затвором второго (2) входного полевого транзистора, первый (7) выходной транзистор, эмиттер которого подключен к стоку второго (2) входного полевого транзистора и через второй (8) токостабилизирующий двухполюсник связан со второй (9) шиной источника питания, второй (10) выходной транзистор, эмиттер которого соединен со стоком первого (1) входного полевого транзистора и через третий (11) токостабилизирующий двухполюсник связан со второй (9) шиной источника питания, цепь динамической нагрузки (12), согласованную с первой (3) шиной источника питания, вход которой (13) соединен с коллектором первого (7) выходного транзистора, а выход (14) связан с выходом устройства (15) и коллектором второго (10) выходного транзистора, причем базы первого (7) и второго (10) выходных транзисторов соединены с источником напряжения смещения (16), отличающийся тем, что в схему введены первый (17) и второй (18) дополнительные полевые транзисторы, истоки которых подключены к истокам первого (1) и второго (2) входных полевых транзисторов, затвор первого (17) дополнительного полевого транзистора соединен с первым (5) входом устройства, а затвор второго (18) дополнительного полевого транзистора соединен со вторым (6) входом устройства, сток первого (17) дополнительного полевого транзистора связан со второй (9) шиной источника питания через первый (19) дополнительный резистор, сток второго (18) дополнительного полевого транзистора связан со второй (9) шиной источника питания через второй (20) дополнительный резистор, эмиттер первого (7) выходного транзистора связан с эмиттером первого (21) дополнительного биполярного транзистора, база которого соединена со стоком второго (18) дополнительного полевого транзистора, а коллектор соединен со второй (9) шиной источника питания, эмиттер второго (10) выходного транзистора связан с эмиттером второго (22) дополнительного биполярного транзистора, база которого соединена со стоком первого (17) дополнительного полевого транзистора, а коллектор соединен со второй (9) шиной источника питания.