Способ и устройство для усовершенствованных технологий пропуска блокировки

Иллюстрации

Показать всеИзобретение относится к устройству и способу повышения эффективности при параллельном выполнении программных транзакций при исполнении спекулятивных критических секций в рамках архитектуры транзакционной памяти. Технический результат заключается в обеспечении параллельного выполнения программных транзакций и одной или нескольких аппаратных транзакций и достигается за счет установления блокировок в начале выполнения критической секции и контроля того, что блокировка установлена при завершении критической секции. Выполняют спекулятивную критическую секцию до завершения независимо от того, удерживается ли блокировка другой транзакцией в начале или во время выполнения спекулятивной критической секции. Как только выполнение спекулятивного критической секции завершено, определяют, что блокировка захвачена. Если блокировка не захвачена, то выполняют завершение спекулятивной критической секции. Если блокировка захвачена, то выполняют прерывание спекулятивной критической секции. 3 н. и 18 з.п. ф-лы, 16 ил.

Реферат

Область техники, к которой относится изобретение

Описанные в данном документе варианты осуществления относятся в основном к усовершенствованным технологиям пропуска блокировок.

Уровень техники

Традиционно, синхронизация между потоками, обращающихся к общей памяти, была реализована с помощью блокировок для защиты совместно используемых данных от параллельного доступа. Тем не менее, блокировки часто сериализируют доступ к совместно используемым данным, которые не всегда могут быть необходимы во время выполнения, но часто сомнительны, или иногда невозможно определить, когда код записан. Например, блокировка может защитить доступ ко всей хеш-таблице, но потоки могут получить доступ к определенным сегментам в хэш-таблице во время выполнения. Таким образом, в данном случае, блокировка излишне ограничивает параллелизм, что потенциально может привести к снижению производительности программы. Более эффективное использование параллельных ресурсов позволяет всем потокам, обращающихся к определенным данным, работать параллельно. Таким образом, для повышения производительности программы может использоваться блокировка с высокой степенью детализации, но часто программист при разработке и проверке сталкивается с трудностями.

Была предложена транзакционная память в качестве альтернативного решения, что позволяет потокам гипотетически входить и выходить из критических секций, называемые "транзакциями", параллельно. Если возникает конфликт во время выполнения, то потоки останавливают или отменяют транзакции и выполняют их снова для разрешения конфликта. Хотя многие эксперты считают, что единственным правильным решением является использование программной транзакционной памяти (STM), где транзакции реализованы полностью на программном обеспечении для синхронизации общей памяти в многопоточных программах, однако это влечет за собой рост накладных расходов при использовании в качестве общего решения.

Кроме того, транзакционная память требует от программиста переписать приложение с помощью анататоров транзакций для обозначения начала и окончания транзакций и, в некоторых случаях, также доступа к общей памяти. Эти усилия не могут быть значительными при разработке нового программного обеспечения, но для унаследованных приложений с потенциально тысячами строк кода (или более), это может быть существенным.

Пропуск спекулятивных блокировок (SLE) предоставляет способ выполнения критических секций параллельно в качестве спекулятивных транзакций для кода, который был записан для использования блокировок. Программист должен добавлять префикс установки блокировки и снятия блокировки с конкретными префиксами для указания начала и окончания критической секции. Если транзакция прерывается, оборудование не выполняет операцию и возвращает в начало критической секции, устанавливает блокировку и обработка продолжается в не спекулятивном режиме. К сожалению, данный вариант реализации ограничивает выполнение только одной не спекулятивной критической секции одновременно: только поток, который захватил блокировку, может выполняться не спекулятивно. Кроме того, чтобы обеспечить корректность, никакая другая спекулятивная критическая секция не может выполняться параллельно с не спекулятивной секцией.

Краткое описание чертежей

Настоящее изобретение иллюстрируется в качестве примера и не ограничивается описанием на прилагаемых чертежах, на которых одинаковые ссылочные позиции обозначают одинаковые элементы и на которых:

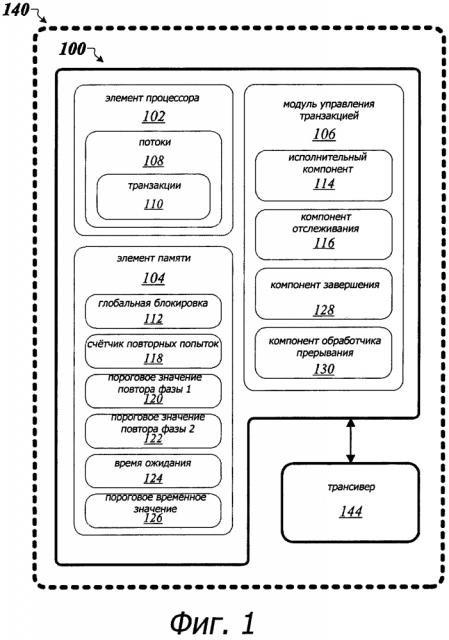

фиг. 1 иллюстрирует один вариант осуществления устройства и один вариант осуществления первой системы;

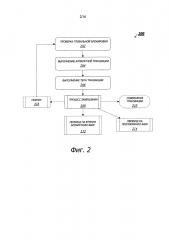

фиг. 2 иллюстрирует один вариант осуществления первого логического потока;

фиг. 3 иллюстрирует один вариант осуществления второго логического потока;

фиг. 4 иллюстрирует один вариант осуществления третьего логического потока;

фиг. 5 иллюстрирует один вариант осуществления четвертого логического потока;

фиг. 6 иллюстрирует один вариант осуществления пятого логического потока;

фиг. 7 иллюстрирует один вариант осуществления носителя информации;

фиг. 8 иллюстрирует один вариант осуществления второй системы;

фиг. 9 иллюстрирует один вариант осуществления третьей системы;

фиг. 10 иллюстрирует один вариант осуществления устройства;

фиг. 11А иллюстрирует примерный псевдокод, иллюстрирующий работу одного варианта осуществления настоящего изобретения;

фиг. 11В иллюстрирует способ в соответствии с одним вариантом осуществления настоящего изобретения;

фиг. 12А-В иллюстрируют выполнение не спекулятивных критических секций и спекулятивных критических секций в разных вариантах осуществления;

фиг. 13А-В иллюстрируют временные характеристики не спекулятивных критических секций и спекулятивных критических секций в разных вариантах осуществления.

Подробное описание вариантов осуществления

Варианты осуществления изобретения, описанные ниже, включают в себя усовершенствование предшествующих схем SLE, позволяя спекулятивным критическим секциям работать параллельно, по меньшей мере, с одной не спекулятивной критической секцией, сохраняя при этом корректность.

Согласно парадигме транзакционной памяти в среде параллельного программирования, транзакции обрабатываются с помощью подхода выполнено - не выполнено, в котором транзакции спекулятивно выполняется без изменения контента областей общей памяти до тех пор, пока те транзакции впоследствии выполняются. Таким образом, операции выполняются атомарно так, что они появляются в остальной части системы и происходят мгновенно, во время, когда они выполнены. Эти свойства позволяют обеспечить реализацию последовательности и изоляцию по отношению к операциям, которые осуществляются параллельно.

Использование программной транзакционной памяти является традиционным подходом реализации парадигмы транзакционной памяти и может включать в себя использование библиотеки времени выполнения и/или языка программирования семантики транзакционной памяти. Способы использования программной транзакционной памяти могут вызывать возникновение значительных накладных расходов, тем не менее. Аппаратная транзакционная память является другим традиционным подходом в реализации парадигмы транзакционной памяти и может включать в себя использование процессоров, кэш, протоколов шины и/или другие элементы, поддерживающие транзакции. Способы аппаратной транзакционной памяти, как правило, обеспечивают более быстрое выполнение транзакций с менее высокими ассоциированными накладными расходами, но обычно существует ограничение по размеру. Кроме того, обычные способы аппаратной транзакционной памяти обычно используют принцип выбора наилучшего возможного в соответствии с которым, не может произойти продвижение вперед. Конкретная транзакция в системе аппаратной транзакционной памяти может сколь угодно долго повторять цикл обнаружения той же ошибки, прерывание, сбоя при завершении и повторного выполнения, в связи с отсутствием механизма, для того, чтобы транзакция обрабатывалась по-разному так, чтобы цикл прерывался.

Может применяться подход гибридной транзакционной памяти в целях реализации более быстрого выполнения транзакций и снижения накладных расходов, ассоциированных с аппаратной транзакционной памятью, и в тоже время, обеспечивая прогресс при обработке транзакций. В соответствии с подходом использования гибридной транзакционной памяти, каждая транзакция первоначально обрабатывается в аппаратных средствах и впоследствии обрабатывается в программном обеспечении, если продвижение вперед не может быть достигнуто в аппаратных средствах. Одним из недостатков некоторых обычных подходов использования гибридной транзакционной памяти может быть то, что они не позволяют осуществить параллельное выполнение программных и аппаратных транзакций. В других обычных подходах использования гибридной транзакционной памяти параллельное выполнение программных и аппаратных транзакций может быть возможно, но может потребовать использования конкретного оборудования, которое поддерживает экранирующие действия и/или может потребоваться поддержка компилятора для аннотаций исходного кода транзакций. Для устранения данных недостатков, различные варианты осуществления описывают системы гибридной транзакционной памяти, в которых используется глобальная блокировка для параллельного выполнения программной транзакции и одной или более аппаратных транзакций. Некоторые варианты осуществления могут обеспечить параллельное выполнение программной транзакции и одной или более аппаратных транзакций, не требуя использования, в частности, аппаратных средств, без экранирующего действия и/или без необходимости поддержки компилятором.

Различные варианты осуществления изобретения могут быть, в основном, направлены на использование улучшенных способов управления транзакционной памятью. В одном варианте осуществления, например, устройство может содержать элемент процессора, компонент выполнения для выполнения элементом процессора параллельного выполнения программной транзакции и аппаратной транзакции в соответствии с процессом транзакционной памяти, компонент отслеживая для активации элементом процессора глобальной блокировки, указывая на выполнение программной транзакции, и компонент завершения для исполнения элементом процессора процесса завершения программной транзакции и деактивации глобальной блокировки при завершении программной транзакции, компонент завершения прерывает аппаратную транзакцию, когда глобальная блокировка активна при завершении аппаратной транзакции. Другие варианты осуществления могут быть описаны и заявлены.

Различные варианты осуществления могут включать в себя один или несколько элементов. Элемент может содержать любую упорядоченную структуру, выполненную с возможностью выполнять определенные операции. Каждый элемент может быть реализован в виде аппаратных средств, программных средств или любой их комбинации, как требуется для заданного набора конструктивных параметров или характеристик. Хотя вариант осуществления может быть описан с помощью ограниченного числа элементов в определенной топологии в качестве примера, вариант осуществления может включать в себя больше или меньше элементов в альтернативных топологиях, как требуется для данной реализации. Стоит отметить, что любая ссылка на "один вариант осуществления" или на "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанные в связи с вариантом воплощения, включены в состав, по меньшей мере, одного варианта осуществления. Употребление фраз "в одном варианте осуществления", "в некоторых вариантах осуществления" и "в различных вариантах осуществления" в различных местах в описании не обязательно относятся к тому же самому варианту осуществления изобретения.

Фиг. 1 показывает блок-схема устройства 100. Как показано на фиг. 1, устройство 100 содержит множество элементов, такие как элемент 102 процессора, элемент 104 памяти и модуль 106 управления транзакцией. Варианты осуществления, однако, не ограничиваются типом, количеством или расположением элементов, показанных на этом чертеже.

В различных вариантах осуществления устройство 100 может включать в себя элемент 102 процессора. Элемент 102 процессора может быть реализован с использованием любого устройства процессора или логического устройства, способного реализовать параллелизм. В некоторых вариантах осуществления, например, элемент 102 процессора может содержать многоядерный процессор. В другом примерном варианте осуществления, элемент 102 процессора может содержать несколько процессоров, предназначенные для выполнения задач параллельно. Варианты осуществления не ограничивается этими примерами.

В различных вариантах осуществления устройство 100 может содержать или иметь возможность коммуникативно взаимодействовать с элементом 104 памяти. Элемент 104 памяти может быть реализован с помощью любых машиночитаемых носителей, способных хранить данные, как энергозависимую, так и энергонезависимую память. В некоторых вариантах осуществления, элемент 104 памяти может содержать кэш для элемента 102 процессора. В различных вариантах осуществления, элемент 104 памяти может дополнительно или альтернативно содержать другие типы носителей данных, такие как постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), динамическую RAM (DRAM), DRAM с удвоенной скоростью передачи данных (DDRAM), синхронное DRAM (SDRAM), статическое RAM (SRAM), программируемое ROM (PROM), стираемую программируемую ROM (EPROM), электрически стираемую программируемую ROM (EEPROM), флэш-памяти, запоминающее устройство на полимере, такое как память на ферроэлектрическом полимере, запоминающее устройство на элементах Овшинского, память на фазовых переходах или память на сегнетоэлектриках, память со структурой металл-нитрид кремния-оксид (SONOS), магнитные или оптические карты или любой другой тип носителя, пригодный для хранения информация. Стоит отметить, что некоторая часть или весь элемент 104 памяти может быть включен в ту же интегральную схему в качестве элемента 102 процессора, или альтернативно, некоторая часть или весь элемент 104 памяти может быть расположен на интегральной схеме или на другом носителе, например, жесткий диск, который является внешним по отношению к интегральной схеме элемента 102 процессора. Хотя элемент 104 памяти установлен в устройстве 100, как показано на фиг. 1, элемент 104 памяти может быть внешним по отношению к устройству 100 в некоторых вариантах осуществления. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, устройство 100 может включать в себя модуль 106 управления транзакциями. Модуль 106 управления транзакциями может содержать схему, логический блок и/или команды, при помощи которых осуществляется управление функционированием устройства 100 в соответствии с парадигмой транзакционной памяти. В различных вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью вызывать выполнение обоих транзакций, как аппаратных, так и программных транзакций в устройстве 100. Аппаратные транзакции могут содержать транзакции, выполняемые непосредственно логическим устройством в элементе 102 процессора. Программные транзакции могут содержать транзакции, выполняемые опосредовано посредством логического программирования, осуществляемого на элементе 102 процессора. Стоит отметить, что в соответствии с парадигмой транзакционной памяти, потоки могут спекулятивно выполнять транзакции без изменения контента в ячейках общей памяти до тех пор, пока транзакции будут выполнены последовательно. Если определяется конфликт или потенциальный конфликт после выполнения транзакции, то выполнение транзакции может быть прервано, вместо того, чтобы разрешить завершения процесса. Таким образом, транзакции могут быть прерваны после того, как они выполнены. Кроме того, любая конкретная транзакция может быть повторно выполнена один или несколько раз в случае, если она не была завершена после первоначального исполнения. Таким образом, при некоторых обстоятельствах, конкретная транзакция может многократно выполняется и прерывается прежде чем, в конечном счете, будет получено разрешение на ее совершение. Варианты осуществления не ограничены в этом контексте.

Фиг. 1 также иллюстрирует блок-схему системы 140. Система 140 может содержать любые из вышеупомянутых элементов устройства 100. Система 140 может дополнительно включать в себя трансивер 144. Трансивер 144 может включать в себя одну или несколько радиостанций, способных передавать и принимать сигналы с помощью различных подходящих способов беспроводной связи. Такие способы могут включать установление связи посредством одной или более беспроводных сетей. Примерные беспроводные сети включают в себя (но не ограничиваются) беспроводные локальные сети (WLANs), беспроводные персональные сети (WPANs), беспроводные городские сети (WMANs), сотовые сети и спутниковые сети. При осуществлении коммуникации посредством таких сетей, трансивер 144 может работать в соответствии с одним или более соответствующим стандартам любой версии. Варианты осуществления не ограничены в этом контексте.

Обычно, устройство 100 и/или система 140 может быть выполнена с возможностью осуществлять транзакции в соответствии с алгоритмом транзакционной памяти. Более конкретно, устройство 100 и/или система 140 может быть выполнена с возможностью выполнять алгоритм гибридной транзакционной памяти, в соответствии с которым транзакции могут быть выполнены как аппаратные, так и программные. В некоторых вариантах осуществления, в соответствии с алгоритмом гибридной транзакционной памятью, любая конкретная транзакция может быть первой, выполненной аппаратной, и затем может быть выполнена программная, если попытки совершить с помощью аппаратной были неудачны. В различных вариантах осуществления, алгоритм гибридной транзакционной памяти может обеспечить реализацию быстрого выполнения транзакции и тем самым снизить накладные расходы, связанные с аппаратной транзакционной памятью, обеспечивая дальнейшую обработку транзакций с помощью программной транзакционной памяти в качестве отката.

В различных вариантах осуществления, алгоритм гибридной транзакционной памяти может обеспечить параллельное выполнение программной транзакции и одной или более аппаратных транзакций без конструктивных ограничений, присущих обычным системам гибридной транзакционной памяти. Например, в отличие от некоторых обычных систем гибридной транзакционной памяти, которые требуют использования определенного оборудования, которое поддерживает экранирующее действие, различные варианты осуществления могут не требовать использования конкретного аппаратного оборудования и могут не требовать поддержки экранирующего действия. В качестве другого примера, в отличие от некоторых обычных систем гибридной транзакционной памяти, которые требуют поддержки уровня компилятора для аннотаций исходного кода уровня транзакций, различные варианты осуществления могут обеспечить параллельное выполнение программной транзакции и одной или несколько аппаратных транзакций, не требуя поддержки уровня компилятора. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, элемент 102 процессора может обрабатывать один или несколько потоков 108. Каждый поток 108 может соответствовать приложению или программе, работающие на элементе 102 процессора, и любое конкретное приложение или программа могут иметь более, чем один ассоциированный поток 108. Приложение или программа может использовать конкретный поток 108 для запроса на выполнение одной или нескольких транзакций ПО. Транзакция ПО может содержать вычисления и другие задачи, которые будут выполняться элементом 102 процессора. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления, когда поток 108 запрашивает выполнение транзакции ПО, модуль 106 управления транзакцией может быть выполнен с возможностью управлять транзакцией ПО в соответствии с алгоритмом гибридной транзакционной памяти. В некоторых вариантах осуществления алгоритм гибридной транзакционной памяти может содержать несколько фаз выполнения, в течение которых могут быть сделаны попытки выполнить и завершить транзакцию ПО. В различных вариантах осуществления алгоритм гибридной транзакционной памяти может содержать первую аппаратный фазу, вторую аппаратную фазу и программную фазу. В некоторых вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью использовать вторую аппаратную фазу для транзакции ПО только после того, как первая аппаратная фаза была не выполнена, и может быть выполнен с возможностью использовать программную фазу для транзакции ПО только после невыполнения второй аппаратной фазы. В различных вариантах осуществления первая аппаратная фаза может содержать более агрессивную аппаратную фазу, вторая аппаратная фаза может содержать более консервативную аппаратную фазу и программная фаза может содержать откатную фазу, в течение которой транзакции ПО назначен наивысший приоритет, чтобы убедиться, что она будет завершена, и что дальнейший процесс обработки будет обеспечен. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может использовать глобальную блокировку 112 для обеспечения параллельного выполнения программной транзакции и одной или более аппаратных транзакций. В различных вариантах осуществления, модуль 106 управления транзакциями может быть выполнен с возможностью вызывать установку или активацию глобальной блокировки 112 при выполнении программной транзакции, и вызвать команду на освобождение или на перевод в состояние неактивности глобальной блокировки 112 при невыполнении программной транзакции. В некоторых вариантах осуществления, глобальная блокировка 112 может содержать спин-блокировку. В других вариантах осуществления может быть использована Mellor-Crummey-Scott (MCS) блокировка для глобальной блокировки 112, чтобы снизить конфликт блокировки на кэш-строке. В различных вариантах осуществления изобретения способы "MCS захват" и "MCS освобождение" могут быть использованы для использования преимуществ аппаратных транзакций, чтобы ускорить выполнение инструкций сравнение с обменом (CAS). Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью обеспечивать выполнение некоторых аппаратных транзакций, но не допускать завершения аппаратных транзакций, когда глобальная блокировка 112 установлена или активна. В различных вариантах осуществления, модуль 106 управления транзакциями может быть выполнен с возможностью разрешать выполнение аппаратных транзакций на первой аппаратной фазе, когда глобальная блокировка 112 установлена, но может не разрешать выполнение аппаратной транзакции на второй аппаратной фазе, когда глобальная блокировка установлена. Таким образом, первая аппаратная фаза может содержать более агрессивную фазу выполнения, в то время, как вторая аппаратная фаза может содержать более консервативную фазу выполнения, во время которой, система ожидает неактивной глобальной блокировки 112 до выполнения транзакции 110. В некоторых вариантах осуществления программная фаза может содержать откатную фазу выполнения, в течение которой транзакции 110 присваивается высший приоритет для обеспечения того, что она будет завершена, и что прогресс обработки будет завершен. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления модуль 106 управления транзакцией может содержать исполнительный компонент 114. В некоторых вариантах осуществления, исполнительный компонент 114 может содержать логическую схему, схему и/или инструкции, выполненный с возможностью выполнять транзакцию 110. В различных вариантах осуществления, когда каждый раз поток 108 запрашивает выполнение новой транзакции 110, исполнительный компонент 114 может быть выполнен с возможностью выполнять одну или несколько транзакций 110. В некоторых вариантах осуществления, исполнительный компонент 114 может быть выполнен с возможностью сначала выполнять транзакцию 110 один или несколько раз как аппаратную транзакцию и затем впоследствии выполнить транзакцию 110 как программную транзакцию, если транзакция не завершена при выполнении аппаратно. В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью выполнять транзакцию 110 один или несколько раз в первой аппаратной фазе, выполнять транзакцию 110 один или несколько раз на второй аппаратной фазе, если она не завершена во время первой аппаратной фазы, и выполнить транзакцию 110 в программной фазе, если она не завершена в ходе второй аппаратной фазы. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед каждым выполнением транзакции 110 во время первой аппаратной фазы и/или второй аппаратной фазы. В различных вариантах осуществления, в ходе первой аппаратной фазы исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110, но с возможностью продолжить выполнение транзакции 110 независимо от состояния глобальной блокировки 112. В некоторых вариантах осуществления, путем проверки глобальной блокировки 112 перед выполнением транзакции 110, исполнительный компонент 114 может быть выполнен с возможностью увеличивать вероятность того, что величина глобальной блокировки будет присутствовать в кэш-строке ядра процессора, выполняющего транзакцию 110, что может привести к временному локальному выигрышу в производительности, если и когда транзакция завершается на первой аппаратной фазе. В различных вариантах осуществления на второй аппаратной фазе исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110, и если глобальная блокировка 112 установлена, то исполнительный компонент 114 может быть выполнен с возможностью ожидать освобождения глобальной блокировки 112 перед выполнением транзакции 110. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110 на программной фазе. В некоторых вариантах осуществления, если глобальная блокировка 112 активна, то исполнительный компонент 114 может быть выполнен с возможностью ожидать выполнения ряда «пустых операций» (NOPs) и затем, возможно, перепроверить глобальную блокировку 112. В различных вариантах осуществления, каждый последующий раз, когда исполнительный компонент 114 находит глобальную блокировку 112 для активации, исполнительный компонент 114 может ожидать более длительный период времени, прежде чем перепроверить глобальную блокировку 112. В некоторых вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью ожидать в течение периода времени, заданного временем 124 ожидания, и может быть выполнен с возможностью экспоненциально увеличить время 124 ожидания каждый раз, как было установлено, что глобальная блокировка 112 по-прежнему активна. В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью постоянно увеличивать время 124 ожидания, пока величина не достигает пороговой величины 126 ожидания. В некоторых вариантах осуществления, когда время 124 ожидания достигает пороговой величины 126 ожидания, исполнительный компонент не может дополнительно увеличить время 124 ожидания. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может содержать компонент 116 отслеживания. В различных вариантах осуществления компонент 116 отслеживания может содержать логические схемы, схемы и/или инструкции, выполненный с возможностью управлять глобальной блокировкой 112, счетчик 118 повторных попыток, пороговое значение 120 повтора фазы 1 и пороговое значение 122 повтора фазы 2. В некоторых вариантах осуществления компонент 116 отслеживания может быть выполнен с возможностью устанавливать глобальную блокировку 112 на основе инструкции от исполнительного компонента 114. Например, исполнительный компонент 114 может быть выполнен с возможностью инструктировать компонент 116 отслеживания на установку глобальной блокировки 112, когда исполнительный компонент 114 начинается выполнение транзакции 110 в программной фазе. В различных вариантах осуществления, счетчик 118 повторных попыток может содержать общее число попыток, которые были сделаны для выполнения транзакции 110. В некоторых вариантах осуществления пороговое значение 120 повтора фазы 1 может содержать количество попыток, после которых исполнительный компонент 114 переводит из аппаратной фазы 1 в аппаратную фазу 2, и пороговое значение 122 фазы 2 может содержать количество попыток, после которых исполнительный компонент 114 переводит из аппаратной фазы 2 в программную фазу. В различных вариантах осуществления, когда принята новая транзакция ПО, компонент 116 отслеживания может быть выполнен с возможностью обнулить показания счетчика 118 повторных попыток. В некоторых вариантах осуществления, после каждого выполнения транзакции 110, компонент 116 отслеживания может быть выполнен с возможностью увеличить количество попыток в счетчике 118 повторных попыток. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления модуль 106 управления транзакцией может содержать компонент 128 завершения. В некоторых вариантах осуществления компонент 128 завершения может содержать логическую схему, схему и/или инструкции, выполненный с возможностью определять, следует ли завершить или прервать процесс выполнения транзакции 110 после того, как они выполняются исполнительным компонентом 114. В различных вариантах осуществления компонент 128 завершения может быть выполнен с возможностью определять, что любая конкретная транзакция 110 должна быть прервана, когда транзакция 110 конфликтует или потенциально конфликтует с другой транзакцией. В некоторых вариантах осуществления компонент 128 завершения может быть выполнен с возможностью определять, может ли транзакция 110 потенциально конфликтовать с конкурентной программной транзакцией посредством проверки глобальной блокировки 112. В различных вариантах осуществления, если глобальная блокировка 112 установлена и транзакция 110 является аппаратной транзакцией, то компонент 128 завершения может быть выполнен с возможностью определять, что транзакция 110 должна быть прервана. В некоторых вариантах осуществления, если глобальная блокировка 112 установлена и транзакция является программной транзакцией, то компонент 128 завершения может быть выполнен с возможностью завершать транзакцию 110 и инструктировать компонент 116 отслеживания освободить глобальную блокировку 112 и обнулить счетчик 118 повторных попыток. В различных вариантах осуществления, если глобальная блокировка 112 не установлена, то компонент 128 завершения может быть выполнен с возможностью завершать транзакцию 110 и инструктировать компонент 116 отслеживания обнулить счетчик 118 повторных попыток. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может содержать компонент 130 обработчика прерывания. В различных вариантах осуществления компонент 130 обработчика прерывания может содержать логические схемы, схемы и/или инструкции, выполненный с возможностью обрабатывать прерывание транзакций 110, в соответствии с указаниями компонента 128 завершения. В некоторых вариантах осуществления компонент 130 обработчика прерывания может быть выполнен с возможностью определять, является ли последующая операция попыткой прерывания транзакции 110, которая должна происходить в первой аппаратной фазе, на второй аппаратной фазе или в программной фазе. В различных вариантах осуществления компонент 130 обработчика прерывания может быть выполнен с возможностью определять, должна ли транзакция 110 быть прервана в результате конфликта или возможного конфликта с другой транзакции или по другой причине. Если транзакция 110 была прервана по другой причине, например, из-за недопустимой инструкции, переполнения емкости или переполнения ассоциативности кэш в связи со случайным характером доступа к памяти, компонент 130 обработчика прерывания может быть выполнен с возможностью определять, что исполнительный компонент 114 должен приступить непосредственно к программной фазе. Если транзакция 110 была прервана в связи с конфликтом или потенциальным конфликтом с другой транзакцией, то компонент 130 обработчика прерывания может быть выполнен с возможностью определять, следует ли повторить транзакцию 110 на данной фазе или на следующей фазе.

В различных вариантах осуществления, для определения фазы для следующей попытки выполнения прерывания транзакции 110, компонент 130 обработчика прерывания может быть выполнен с возможностью сравнивать показания счетчика 118 повторных попыток на фазе 1 с пороговым значением 120 повтора фазы 1 и/или пороговым значением 122 фазы 2. В некоторых вариантах осуществления, если показания счетчика 118 повторных попыток меньше, чем пороговое значение 120 фазы 1, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на первой аппаратной фазе. В различных вариантах осуществления, если показания счетчика 118 повторных попыток меньше порогового значения 122 фазы 2, но не менее порогового значения 120 фазы 1, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на второй аппаратной фазе. В некоторых вариантах осуществления, если показания счетчика 118 повторных попыток составляет не менее порогового значения 122 фазы 2, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на программной фазе. В различных вариантах осуществления компонент 116 отслеживания может быть выполнен с возможностью адаптивно определять значения пороговой величины 120 фазы 1 и/или пороговой величины 122 фазы 2 на основе количества успешных и/или неудачных завершений попыток совершения транзакций. Варианты осуществления не ограничены в этом контексте.

Операции для вышеописанных вариантов осуществления могут быть подробно описаны со ссылкой на следующие чертежи и соответствующих примерах. Некоторые из чертежей могут включать в себя логическую схему. Хотя такие чертежи, представленные здесь, могут включать в себя конкретную логическую схему, но следует понимать, что логическая блок-схема алгоритма является лишь только примером реализации общей функциональности, как описано здесь. Кроме того, данная логическая блок-схема алгоритма не обязательно должна быть выполнена в указанном порядке, если не указано иное. Кроме того, данный логический поток операций может быть реализован с помощью аппаратного элемента, программного элемента, выполняемого процессором, или любой их комбинации. Варианты осуществления не ограничены в этом контексте.

Фиг. 2 иллюстрирует один вариант осуществления логического алгоритма 200, который может быть примером операций, выполняемых одним или несколькими вариантами осуществления, описанными в данном документе. Более конкретно, логический алгоритм 200 может содержать пример операций, выполняемых в устройстве 100 и/или системе 140, показанной на фиг. 1, во время обработки любой конкретной транзакции на первой аппаратной фазе. Как показано на схеме логического алгоритма 200, глобальная блокировка может быть проверена на этапе 202. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью проверять глобальную блокировку 112. На этапе 204 может начаться аппаратная транзакция. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью начать обработку транзакции 110 в первой аппаратной фазе. На этапе 206 тело транзакции может быть выполнено. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью выполнять транзакцию 110 на аппаратном уровне.

На этапе 208 может быть применен алгоритм завершения обработки, как будет описано более подробно со ссылкой на фиг. 5 ниже. Одним из возможных результатов алгоритма завершения обработки может быть то, что транзакция может быть завершена на этапе 210. Например, компонент 128 завершения, показанный на фиг. 1, может быть выполнен с возможностью заверша