Биполярно-полевой операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиоэлектроники, а именно к прецизионным устройствам усиления сигналов. Технический результат - повышение коэффициента усиления дифференциального сигнала в разомкнутом состоянии ОУ до уровня 90÷100 дБ. Биполярно-полевой операционный усилитель содержит первый (1) и второй (2) входные полевые транзисторы, объединенные истоки которых связаны с первой (3) шиной источника питания через первый (4) токостабилизирующий двухполюсник, а затворы соединены с соответствующими входами (5) и (6) устройства, первый (7) и второй (8) выходные транзисторы, базы которых объединены и подключены к цепи смещения потенциалов (9), эмиттер первого (7) выходного транзистора соединен со второй (10) шиной источника питания через первый (11) токостабилизирующий резистор, эмиттер второго (8) выходного транзистора соединен со второй (10) шиной источника питания через второй (12) токостабилизирующий резистор, токовое зеркало (13), согласованное с первой (3) шиной источника питания, выход которого соединен с токовым выходом устройства (14) и коллектором второго (8) выходного транзистора, а вход токового зеркала (13) соединен с коллектором первого (7) выходного транзистора. В схему введены первый (15), второй (16), третий (17) и четвертый (18) дополнительные транзисторы, а также первый (19) и второй (20) дополнительные резисторы, объединенные коллекторы первого (15) и второго (16) дополнительных транзисторов соединены с истоками первого (1) и второго (2) входных полевых транзисторов, базы третьего (17) и четвертого (18) дополнительных транзисторов связаны с базами первого (7) и второго (8) выходных транзисторов, база первого (15) дополнительного транзистора соединена с коллектором третьего (17) дополнительного транзистора, эмиттер первого (15) дополнительного транзистора подключен к эмиттеру первого (7) выходного транзистора, эмиттер третьего (17) дополнительного транзистора связан со второй (10) шиной источника питания через первый (19) дополнительный резистор, база второго (16) дополнительного транзистора соединена с коллектором четвертого (18) дополнительного транзистора, эмиттер второго (16) дополнительного транзистора подключен к эмиттеру второго (8) выходного транзистора, эмиттер четвертого (18) дополнительного транзистора связан со второй (10) шиной источника питания через второй (20) дополнительный резистор. 10 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе архитектуры «перегнутого каскода» [1-14]. Их основные достоинства - расширенный частотный диапазон, а также эффективное использование напряжения питания.

Для работы в условиях космического пространства в экспериментальной физике необходимы радиационно-стойкие ОУ с малым напряжением смещения нуля (Uсм) и повышенным коэффициентом усиления по напряжению (80-100 дБ). Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [15], обеспечивающего формирование p-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако, для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [15-18].

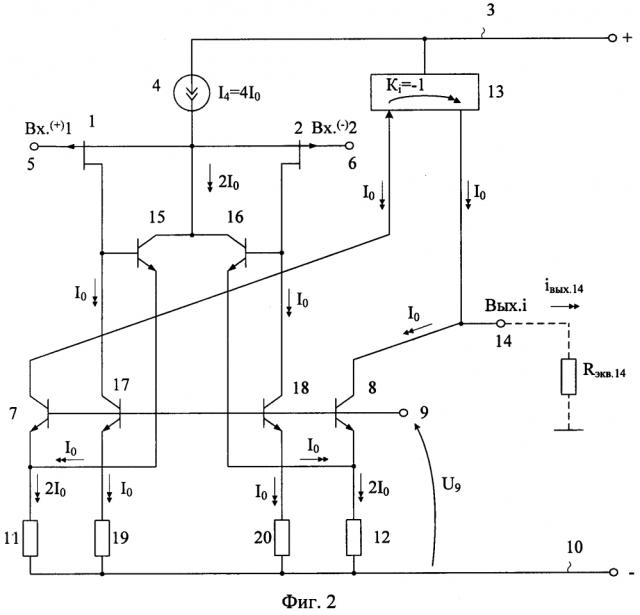

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту US 7215200, fig. 6. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, а затворы соединены с соответствующими входами 5 и 6 устройства, первый 7 и второй 8 выходные транзисторы, базы которых объединены и подключены к цепи смещения потенциалов 9, эмиттер первого 7 выходного транзистора соединен со второй 10 шиной источника питания через первый 11 токостабилизирующий резистор, эмиттер второго 8 выходного транзистора соединен со второй 10 шиной источника питания через второй 12 токостабилизирующий резистор, токовое зеркало 13, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 14 и коллектором второго 8 выходного транзистора, а вход токового зеркала 13 соединен с коллектором первого 7 выходного транзистора.

Существенный недостаток известного ОУ состоит в том, что его коэффициент усиления по напряжению (Kу) получается небольшим. Это связано с тем, что в известной схеме усиление по напряжению обеспечивается только каскадом на выходных транзисторах 7 и 8. Кроме этого, в диапазоне рабочих, прежде всего низких температур, а также при воздействии потока нейтронов он имеет повышенные значения напряжения смещения нуля (Uсм) (единицы-десятки милливольт). В конечном итоге это снижает прецизионность известного ОУ.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления дифференциального сигнала в разомкнутом состоянии ОУ до уровня 90÷100 дБ.

Дополнительная задача - уменьшение напряжения смещения нуля.

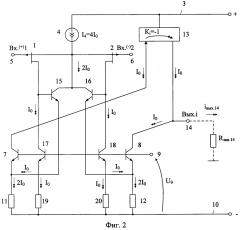

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, а затворы соединены с соответствующими входами 5 и 6 устройства, первый 7 и второй 8 выходные транзисторы, базы которых объединены и подключены к цепи смещения потенциалов 9, эмиттер первого 7 выходного транзистора соединен со второй 10 шиной источника питания через первый 11 токостабилизирующий резистор, эмиттер второго 8 выходного транзистора соединен со второй 10 шиной источника питания через второй 12 токостабилизирующий резистор, токовое зеркало 13, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 14 и коллектором второго 8 выходного транзистора, а вход токового зеркала 13 соединен с коллектором первого 7 выходного транзистора, предусмотрены новые элементы и связи - в схему введены первый 15, второй 16, третий 17 и четвертый 18 дополнительные транзисторы, а также первый 19 и второй 20 дополнительные резисторы, объединенные коллекторы первого 15 и второго 16 дополнительных транзисторов соединены с истоками первого 1 и второго 2 входных полевых транзисторов, базы третьего 17 и четвертого 18 дополнительных транзисторов связаны с базами первого 7 и второго 8 выходных транзисторов, база первого 15 дополнительного транзистора соединена с коллектором третьего 17 дополнительного транзистора, эмиттер первого 15 дополнительного транзистора подключен к эмиттеру первого 7 выходного транзистора, эмиттер третьего 17 дополнительного транзистора связан со второй 10 шиной источника питания через первый 19 дополнительный резистор, база второго 16 дополнительного транзистора соединена с коллектором четвертого 18 дополнительного транзистора, эмиттер второго 16 дополнительного транзистора подключен к эмиттеру второго 8 выходного транзистора, эмиттер четвертого 18 дополнительного транзистора связан со второй 10 шиной источника питания через второй 20 дополнительный резистор.

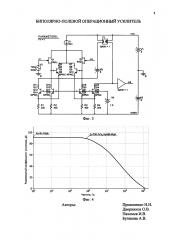

На фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

На фиг. 3 приведена схема ОУ фиг. 2 в среде компьютерного моделирования PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На фиг. 4 показана частотная зависимость коэффициента усиления по напряжению разомкнутого ОУ фиг. 3.

На фиг. 5 приведена зависимость напряжения смещения нуля (Uсм) схемы фиг. 3 от температуры в диапазоне минус 60÷+80°C (а) и потока нейтронов (б) для случая, когда транзисторы схемы не имеют разброса параметров, а токовое зеркало 13 идеально. Это позволяет оценить предельные возможности структуры заявляемого ОУ по величине Uсм.

На фиг. 6 показана схема заявляемого ОУ фиг. 2 в среде PSpice при выполнении токового зеркала 13 на p-n-p транзисторах АБМК 1_3, которые не имеют высокой радиационной стойкости.

На фиг. 7 представлены амплитудно-частотные характеристики схемы фиг. 6 и схемы ОУ-прототипа фиг. 9 при выполнении токового зеркала 13 на p-n-p транзисторах АБМК 1_3. Из данных графиков следует, что заявляемый ОУ (в сравнении с прототипом) имеет более высокий (на 33,4 дБ) коэффициент усиления по напряжению в разомкнутом состоянии.

На фиг. 8 приведена зависимость напряжения смещения нуля ОУ фиг. 6 при выполнении токового зеркала 13 на p-n-p транзисторах АБМК 1_3 от температуры в диапазоне минус 60-80°C (а), потока нейтронов (б).

На фиг. 9 показана схема ОУ-прототипа фиг. 1 в среде PSpice при выполнении токового зеркала 13 на p-n-p транзисторах АБМК 1_3, параметры которых деградируют в большей степени, чем транзисторов n-p-n.

На фиг. 10 приведена зависимость напряжения смещения нуля ОУ-прототипа фиг. 9 при выполнении токового зеркала 13 на р-п-р транзисторах АБМК 1_3 от температуры в диапазоне минус 60 - 80°С (а), потока нейтронов (б).

Сравнение фиг. 10 и фиг. 8 показывает, что предлагаемый ОУ имеет на порядок меньшее значение напряжения смещения нуля как в рабочем диапазоне температур, так и в диапазоне радиационных воздействий.

Биполярно-полевой операционный усилитель фиг. 2 содержит первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, а затворы соединены с соответствующими входами 5 и 6 устройства, первый 7 и второй 8 выходные транзисторы, базы которых объединены и подключены к цепи смещения потенциалов 9, эмиттер первого 7 выходного транзистора соединен со второй 10 шиной источника питания через первый 11 токостабилизирующий резистор, эмиттер второго 8 выходного транзистора соединен со второй 10 шиной источника питания через второй 12 токостабилизирующий резистор, токовое зеркало 13, согласованное с первой 3 шиной источника питания, выход которого соединен с токовым выходом устройства 14 и коллектором второго 8 выходного транзистора, а вход токового зеркала 13 соединен с коллектором первого 7 выходного транзистора. В схему введены первый 15, второй 16, третий 17 и четвертый 18 дополнительные транзисторы, а также первый 19 и второй 20 дополнительные резисторы, объединенные коллекторы первого 15 и второго 16 дополнительных транзисторов соединены с истоками первого 1 и второго 2 входных полевых транзисторов, базы третьего 17 и четвертого 18 дополнительных транзисторов связаны с базами первого 7 и второго 8 выходных транзисторов, база первого 15 дополнительного транзистора соединена с коллектором третьего 17 дополнительного транзистора, эмиттер первого 15 дополнительного транзистора подключен к эмиттеру первого 7 выходного транзистора, эмиттер третьего 17 дополнительного транзистора связан со второй 10 шиной источника питания через первый 19 дополнительный резистор, база второго 16 дополнительного транзистора соединена с коллектором четвертого 18 дополнительного транзистора, эмиттер второго 16 дополнительного транзистора подключен к эмиттеру второго 8 выходного транзистора, эмиттер четвертого 18 дополнительного транзистора связан со второй 10 шиной источника питания через второй 20 дополнительный резистор.

Сопротивление Rэкв.14 моделирует нагрузку в выходной цепи 14 заявляемого (фиг. 2) и известного (фиг. 1) устройств.

Для уменьшения выходного сопротивления устройства к выходу 14 может подключаться буферный усилитель с низким выходным сопротивлением (фиг. 3, Gain=1). Симметрирование статического режима первого 7 и второго 8 выходных транзисторов может осуществляться вспомогательным источником V5 (фиг. 3, фиг. 6).

Рассмотрим работу ОУ фиг. 2.

Статический режим транзисторов схемы фиг. 2 по току устанавливается источником опорного тока 4. При этом токи стоков (Ici) и токи коллекторов (Iкi) транзисторов схемы при 100% отрицательной обратной связи в ОУ определяются уравнениями Кирхгофа:

где U9 - напряжение цепи смещения потенциалов 9 относительно второй 10 шины источника питания;

Uэб≈0,7 В - напряжение эмиттер-база биполярных транзисторов схемы (7, 8, 17, 18) в активном режиме при токах эмиттера Iэi=I0;

R11, R12 - сопротивления первого 11 и второго 12 токостабилизирующих резисторов;

R19, R20 - сопротивления первого 19 и второго 20 дополнительных резисторов;

I11, I12 - токи первого 11 и второго 12 токостабилизирующих резисторов;

I4=4I0 - ток источника опорного тока 4;

I0 - некоторый заданный квант тока, например, I0=2 мА, выбираемый при проектировании ОУ.

Коэффициент усиления по напряжению разомкнутой схемы ОУ фиг. 2 определяется произведением:

где uвых.14 - приращение напряжения на выходе ОУ 14, вызванное изменением напряжения (uвх.5-6) между входами ОУ 5, 6;

- коэффициент преобразования входного напряжения ОУ (uвх.5-6) в напряжение между базами транзисторов 15-16 (u15-16);

- коэффициент передачи дифференциального напряжения между базами транзисторов 15 и 16 на выход усилителя 14.

Причем

где Rэкв.15-16 - эквивалентное дифференциальное сопротивление между базами транзисторов 15 и 16;

Rэкв.14 - эквивалентное сопротивление в цепи нагрузки ОУ (выходного узла 14);

- эквивалентная крутизна входного дифференциального каскада на основе входных полевых транзисторов 1 и 2;

S1, S2 - крутизны стокозатворной характеристики соответствующих входных полевых транзисторов 1 и 2;

;

rэij - сопротивление эмиттерного перехода ij-го транзистора (rэij=φт/Iэij);

φт=25 мВ - температурный потенциал;

Ki≈1 - модуль коэффициента усиления по току токового зеркала 13.

Численное значение эквивалентного сопротивления R3KB.i5-i6 определяется формулой

где β15-16=β15=β16 - коэффициент усиления по току базы транзисторов 15 и 16;

.

Как следствие, за счет создания в схеме фиг. 2 двух высокоимпедансных узлов коэффициент усиления по напряжению разомкнутого ОУ фиг. 2 получается достаточно большим (≈80÷100 дБ):

В ОУ-прототипе этот параметр в β15-16-раз меньше:

В заявляемой схеме ОУ (в сравнении с прототипом) повышается также коэффициент ослабления входных синфазных сигналов (Kос.сф). Данный эффект объясняется введением (за счет новых элементов) отрицательной обратной связи по синфазному сигналу (транзисторы 15 и 16) в истоковую цепь транзисторов 1 и 2, которая улучшает Kос.сф [19].

За счет высокой симметрии схемы ОУ напряжение смещения нуля заявляемого ОУ, в отличие от ОУ-прототипа (фиг. 9), достаточно мало (фиг. 8). Это связано с уменьшением в K1-раз (11) влияния на Uсм погрешностей токового зеркала 13, которое имеет высокую нестабильность статического режима при внешних воздействиях из-за применения p-n-p транзисторов АБМК_1_3 [15-18].

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5422600, фиг. 2.

2. Патент США №4406990, фиг. 4.

3. Патент США №5952882.

4. Патент США №4723111.

5. Патент США №4293824.

6. Патент США №5323121.

7. Патент США №5420540 fig. 1.

8. Патент RU №2354041 C1.

9. Патентная заявка США №2003/0201828 fig 1, fig 2.

10. Патент США №6825721 fig. 1, fig 2.

11. Патент США №6542030 fig. 1.

12. Патент US 6456162, fig. 2.

13. Патент US 6501333.

14. Патент US 6717466.

15. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

16. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 1 / О. Дворников // Компоненты и технологии, №6, 2005, http://kit-e.ru/articles/device/2005_6_218.php.

17. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 2 / О. Дворников // Компоненты и технологии, №7, 2005, http://kit-e.ru/articles/device/2005_7_216.php.

18. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 3 / О. Дворников // Компоненты и технологии, №8, 2005, http://kit-e.ru/articles/device/2005_8_184.php.

19. Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов: монография / Н.Н. Прокопенко, С.В. Крюков. - Шахты: ГОУ ВПО «ЮРГУЭС», 2008. - 329 с.

Биполярно-полевой операционный усилитель, содержащий первый (1) и второй (2) входные полевые транзисторы, объединенные истоки которых связаны с первой (3) шиной источника питания через первый (4) токостабилизирующий двухполюсник, а затворы соединены с соответствующими входами (5) и (6) устройства, первый (7) и второй (8) выходные транзисторы, базы которых объединены и подключены к цепи смещения потенциалов (9), эмиттер первого (7) выходного транзистора соединен со второй (10) шиной источника питания через первый (11) токостабилизирующий резистор, эмиттер второго (8) выходного транзистора соединен со второй (10) шиной источника питания через второй (12) токостабилизирующий резистор, токовое зеркало (13), согласованное с первой (3) шиной источника питания, выход которого соединен с токовым выходом устройства (14) и коллектором второго (8) выходного транзистора, а вход токового зеркала (13) соединен с коллектором первого (7) выходного транзистора, отличающийся тем, что в схему введены первый (15), второй (16), третий (17) и четвертый (18) дополнительные транзисторы, а также первый (19) и второй (20) дополнительные резисторы, объединенные коллекторы первого (15) и второго (16) дополнительных транзисторов соединены с истоками первого (1) и второго (2) входных полевых транзисторов, базы третьего (17) и четвертого (18) дополнительных транзисторов связаны с базами первого (7) и второго (8) выходных транзисторов, база первого (15) дополнительного транзистора соединена с коллектором третьего (17) дополнительного транзистора, эмиттер первого (15) дополнительного транзистора подключен к эмиттеру первого (7) выходного транзистора, эмиттер третьего (17) дополнительного транзистора связан со второй (10) шиной источника питания через первый (19) дополнительный резистор, база второго (16) дополнительного транзистора соединена с коллектором четвертого (18) дополнительного транзистора,эмиттер второго (16) дополнительного транзистора подключен к эмиттеру второго (8) выходного транзистора, эмиттер четвертого (18) дополнительного транзистора связан со второй (10) шиной источника питания через второй (20) дополнительный резистор.