Неограниченная транзакционная память с гарантиями продвижения при пересылке, используя аппаратную глобальную блокировку

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в гарантировании выполнения транзакции, используя аппаратную глобальную блокировку. Устройство обработки потоков содержит аппаратный менеджер разногласий аппаратной транзакционной памяти (НТМ), который обеспечивает перевод транзакции с упреждающим исполнением из множества транзакций с упреждающим исполнением в транзакцию без упреждающего исполнения, при этом транзакция без упреждающего исполнения предназначена для получения глобальной аппаратной блокировки для транзакции без упреждающего исполнения, а глобальная аппаратная блокировка считывается оставшимися транзакциями с упреждающим исполнением, которые отменяют, если глобальная аппаратная блокировка получена; и исполнительный модуль для исполнения инструкций транзакции без упреждающего исполнения без упреждения, в то время как глобальная аппаратная блокировка получена для транзакции без упреждающего исполнения, при этом транзакция без упреждающего исполнения предназначена для освобождения глобальной аппаратной блокировки после завершения исполнения инструкций транзакции без упреждающего исполнения. 3 н. и 22 з.п. ф-лы, 19 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления изобретения, в общем, относятся к устройствам обработки и, более конкретно, относятся к неограниченной транзакционной памяти с гарантиями продвижения при пересылке, используя аппаратную глобальную блокировку.

Уровень техники

Для улучшения рабочих характеристик, некоторые компьютерные системы могут выполнять множество потоков обработки одновременно. В общем, перед тем, как поток получит доступ к совместно используемому ресурсу, он может получить блокировку совместно используемого ресурса. В ситуациях, когда совместно используемый ресурс представляет собой структуру данных, сохраненную в памяти, все потоки, которые пытаются получить доступ к одному и тому же ресурсу, могут установить последовательность исполнения своих операций с учетом взаимной исключительности, предоставляемой механизмом блокировки. Это может отрицательно сказываться на рабочих характеристиках системы и может привести к отказам программы, например, из-за ошибок, ограниченных с зависанием блокировки.

Для уменьшения потерь производительности, возникающих в результате использования механизмов блокировки, в некоторых компьютерных системах может использоваться транзакционная память. Транзакционная память, в общем, относится к модели синхронизации, которая позволяет множеству потоков одновременно получать доступ к совместно используемому ресурсу, без использования механизма блокировки. Однако исполнение транзакционной памяти в процессорах может повысить сложность конструкции, например, из-за ошибок прогнозирования, возникающих в результате упреждающего исполнения.

Краткое описание чертежей. Изобретение будет более полно понято из подробного описания изобретения, представленного ниже, и из приложенных чертежей различных вариантов осуществления раскрытия. Чертежи, однако, не следует рассматривать как ограничение для раскрытия конкретных вариантов осуществления, поскольку они предназначены только для пояснения и понимания.

На фиг. 1 иллюстрируется блок-схема вычислительной системы, в соответствии с вариантом осуществления раскрытия.

На фиг. 2 показана блок-схема потока, иллюстрирующая блок-схему ядра процессора, в соответствии с вариантом осуществления раскрытия.

На фиг. 3А показан пример листинга псевдокода, иллюстрирующий синтаксис транзакции, в соответствии с вариантом осуществления раскрытия.

На фиг. 3В показан пример листинга псевдокода аппаратных инструкций, ассоциированных со ограниченной транзакцией, в соответствии с вариантом осуществления раскрытия.

На фиг. 3С показан пример листинга псевдокода аппаратных инструкций, ассоциированных с неограниченной транзакцией, в соответствии с вариантом осуществления раскрытия.

На фиг. 4А показан пример листинга псевдокода исполнения оптимизированной ограниченной транзакции, в соответствии с вариантом осуществления раскрытия.

На фиг. 4В и 4С показаны блок-схемы, концептуально иллюстрирующие примерные сценарии глобальной аппаратной блокировки, считываемой как в неоптимизированной, так и в оптимизированной форме, в соответствии с вариантом осуществления раскрытия.

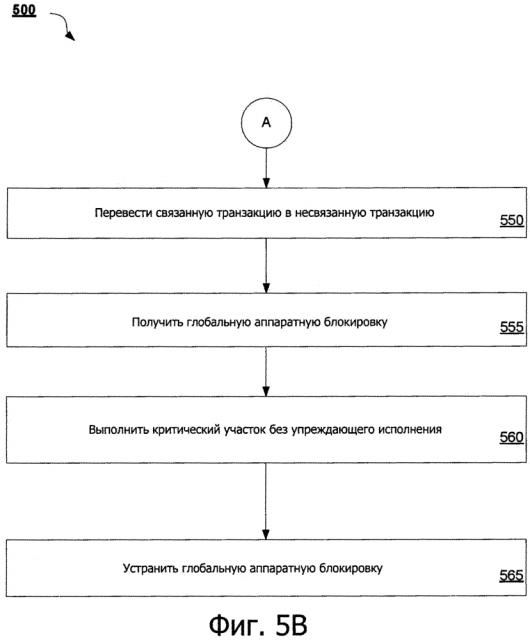

На фиг. 5А и 5В показаны блок-схемы последовательности операций, иллюстрирующие способ для воплощения неограниченной транзакционной памяти с гарантиями продвижения при пересылке, использующей аппаратную глобальную блокировку, в соответствии с воплощением раскрытия

На фиг. 6А показана блок-схема, иллюстрирующая микроархитектуру для процессора, в котором воплощена неограниченная транзакционная память с гарантиями продвижения при пересылке, с использованием аппаратной глобальной блокировки, в которой может использоваться один вариант осуществления раскрытия.

На фиг. 6В показана блок-схема, иллюстрирующая магистраль, работающую не по порядку, и каскад переименования регистра, магистраль выработки/исполнения, работающую по порядку, воплощенную в соответствии с, по меньшей мере, одним вариантом осуществления раскрытия.

На фиг. 7 иллюстрируется блок-схема микроархитектуры для процессора, который включает в себя логические схемы, для воплощения неограниченной транзакционной памяти с гарантиями продвижения при пересылке, с использованием аппаратной глобальной блокировки, в соответствии с одним вариантом осуществления раскрытия.

На фиг. 8 показана блок-схема, иллюстрирующая систему, в которой может использоваться вариант осуществления раскрытия.

На фиг. 9 показана блок-схема системы, в которой может работать вариант осуществления раскрытия.

На фиг. 10 показана блок-схема системы, в которой может работать вариант осуществления раскрытия.

На фиг. 11 показана блок-схема системы на кристалле (SoC), в соответствии с вариантом осуществления настоящего раскрытия

На фиг. 12 показана блок-схема варианта осуществления конструкции SoC, в соответствии с настоящим раскрытием.

На фиг. 13 иллюстрируется блок-схема одного варианта осуществления компьютерной системы.

Подробное описание изобретения

Варианты осуществления изобретения воплощают технологии для неограниченной транзакционной памяти с гарантиями продвижения при пересылке, в которых используется аппаратная глобальная блокировка в устройстве обработки. Традиционно, синхронизация между потоками, которые обращаются к общей памяти, была реализована с использованием блокировки для защиты совместно используемых данных от одновременного доступа. Однако блокировка может привести к ненужной последовательной обработке в системе или может быть чрезмерно сложной для программистов для правильного выполнения. Транзакционная память была предложена, как альтернативное решение для блокировки, и обеспечивает возможность параллельного упреждающего исполнения потоками критических участков, называемых транзакциями. Если возникает конфликт во время исполнения, тогда потоки останавливают или выполняют возврат своих транзакций и исполняют их снова для разрешения конфликта. Один тип ТМ представляет собой программную транзакционную память (STM), где транзакции воплощены полностью в виде программных средств для синхронизации совместно используемой памяти в многопотоковых программах. Однако STM потребовать использования большого количества служебных данных, что не позволяет использовать STM в качестве общего решения.

В последнее время поставщики аппаратных средств предоставили аппаратную транзакционную память (НТМ), работающую на принципе наилучших усилий в устройствах обработки. НТМ на принципе наилучших усилий может обеспечить лучшие характеристики, чем STM, но не выполняет гарантии продвижения при пересылке; то есть, настоящие варианты осуществления НТМ не могут гарантировать, что транзакция будет выполнена, независимо от того, какое количество раз она будет повторно исполнена. ("Наилучшие усилия" относится к концепции, когда система НТМ выполняет все от нее зависящее, но не может гарантировать, что транзакция будет выполнена). Например, транзакция Т1 может быть отклонена транзакцией Т2, которая может быть затем отменена перезапущенной транзакцией Т1, и так далее. Без гарантий продвижения при пересылке НТМ, работающая на принципе наилучших усилий, может деградировать до динамической взаимной блокировки. Кроме того, транзакции аппаратных средств, в общем, могут быть отклонены по множеству причин: истинные или ложные конфликты, переполнения, нелегальные инструкции и т.д.

В результате, современные НТМ, работающие по принципу наилучших усилий, обычно обеспечивают программный путь отхода для решения проблемы отсутствия гарантий продвижения при пересылке и обеспечивают то, что аппаратные транзакции, которые не могут быть выполнены в аппаратных средствах, в конечном итоге, будут выполнены, используя программное обеспечение. Такие системы называются гибридными ТМ (НуТМ), в которых используются, как аппаратные, так и программные транзакции. Было предложено множество алгоритмов НуТМ, но они проявляют тенденцию иметь недостаток существенного усложнения пространства ТМ и введения служебных издержек из-за необходимости использования синхронизирующих аппаратных и программных транзакций.

Предыдущие предложения неограниченных (то есть, без ограничений по размеру транзакции) НТМ, которые не основаны на опции программного отхода, воплощают изменения в протокол когерентности кэш и/или сложных метаданных, таким образом, что они не являются практическими решениями. В отличие от этого, варианты осуществления раскрытия обеспечивают неограниченную НТМ с гарантиями продвижения при пересылке, используя аппаратную глобальную блокировку в устройстве обработки. В частности, варианты осуществления раскрытия исполняют одну неограниченную транзакцию в аппаратных средствах, без маркировки битов транзакции в кэш, параллельно с множеством неограниченных транзакций (которые выполняют с упреждающим исполнением). Одна глобальная аппаратная блокировка достигается неограниченной транзакцией и должна быть считана ограниченными транзакциями перед тем, как они будут считаны ограниченными транзакциями, прежде чем они детектируют потенциальные конфликты между неограниченной транзакцией и ограниченными транзакциями. Неограниченная НТМ, в соответствии с вариантами осуществления раскрытия может быть воплощена в существующих системах НТМ с минимальными изменениями и без изменений протокола когерентности кэш этих систем (которые используются для детектирования конфликтов и обеспечивают когерентность памяти).

Хотя следующие варианты осуществления могут быть описаны со ссылкой на конкретные интегральные схемы, такие как вычислительные платформы или микропроцессоры, другие варианты осуществления применимы для других типов интегральных схем и логических устройств. Аналогичные технологии и описания представленных здесь вариантов осуществления, могут применяться для других типов схем или полупроводниковых устройств. Например, раскрытые варианты осуществления не ограничены настольными компьютерными системами или Ultrabooks™ и также могут использоваться в других устройствах, таких как портативные устройства, планшеты, другие тонкие ноутбуки, устройства типа системы на кристалле (SOC) и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства, работающие с протоколом Интернет, цифровые камеры, карманные персональные компьютеры (PDA) и переносные ПК. Встроенные приложения обычно включают в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на кристалле, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любую другую систему, которая может выполнять функции и операции, описанные ниже.

Хотя следующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы для других типов интегральных схем и логических устройств. Аналогичные технологии и описания вариантов осуществления раскрытия могут применяться для других типов схем или полупроводниковых устройств, которые могут получить пользу, благодаря более высокой пропускной способности магистрали и улучшенным рабочим характеристикам. Описания вариантов осуществления раскрытия применимы к любому процессору или устройству, в котором выполняются манипуляции с данными. Однако настоящее раскрытие не ограничено процессорами или устройствами, которые выполняют операции с данными размером 512 битов, 256 битов, 128 битов, 64 бита, 32 бита или 16 битов, и может применяться к любому процессору и устройству, в котором выполняются манипуляции для управления данными. Кроме того, в следующем описании представлены примеры, и на приложенных чертежах показаны различные примеры с целью иллюстрации. Однако эти примеры не следует рассматривать в ограничительном смысле, поскольку они предназначены просто для использования в качестве примеров вариантов осуществления настоящего раскрытия, а не для предоставления исчерпывающего списка всех возможных вариантов осуществления настоящего раскрытия.

Поскольку все больше компьютерных систем используют в приложениях для Интернет, редактирования текста и в мультимедийных приложениях, дополнительная поддержка процессора была введена с течением времени. В одном варианте осуществления набор инструкций может быть ассоциирован с одной или больше компьютерными архитектурами, включающими в себя типы данных, инструкции, архитектуру регистра, режимы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод и вывод (I/O).

В одном варианте осуществления архитектура набора инструкций (ISA) может быть воплощена с помощью одной или больше микроархитектур, которые включают в себя логические и электрические схемы процессора, используемые для воплощения одного или больше наборов инструкций. В соответствии с этим, процессоры с разными микроархитектурами могут совместно использовать, по меньшей мере, часть общего набора инструкций. Например, процессор Intel® Pentium 4, процессоры Intel® Core™ и процессоры компании Advanced Micro Devices, Inc. of Sunnyvale CA воплощают практически идентичные версии набора инструкций х86 (с некоторыми расширениями, которые были добавлены в более новых версиях), но имеют разные внутренние конструкции. Аналогично, процессоры, разработанные другими компаниями разработчиками процессоров, такие как ARM Holdings, Ltd., MIPS, или их лицензеобладатели или последователи, могут совместно использовать, по меньшей мере, часть общего набора инструкций, но могут включать в себя различные конструкции процессора. Например, одна и та же архитектура регистра в ISA может быть воплощена по-разному в разных микроархитектурах, используя новые или хорошо известные технологии, включающие в себя специализированные физические регистры, один или больше динамически выделенных физических регистров, использующих механизм переименования регистра (например, использование таблицы псевдонима регистров (RAT), буфер изменения порядка (ROB) и файл изъятия регистров. В одном варианте осуществления регистры могут включать в себя один или больше регистров, архитектуру регистров, файлы регистров или другие наборы регистров, которые могут быть адресуемыми или могут не быть адресуемыми программистом, работающим с программными средствами.

В одном варианте осуществления инструкция может включать в себя один или больше форматов инструкции. В одном варианте осуществления формат инструкции может обозначать различные поля (количество битов, места расположения битов и т.д.), для установления, помимо прочего, операции, которая должна быть выполнена, и операнда (операндов), для которого должна быть выполнена эта операция. Некоторые форматы инструкции могут быть дополнительно разделены в соответствии с определением по шаблонам инструкций (или подформатами). Например, шаблоны инструкции заданного формата инструкции могут быть определены так, чтобы они имели разные поднаборы полей формата инструкций и/или были определены так, чтобы они имели заданное поле, интерпретируемое по-разному. В одном варианте осуществления инструкция выражена с использованием формата инструкций (и, если он определен, в заданном одном из шаблонов инструкций этого формата инструкций) и устанавливает или обозначает операцию и операнды, по которым будет работать операция.

На фиг. 1 иллюстрируется блок-схема вычислительной системы 100, в соответствии с вариантом осуществления раскрытия. Система 100 может включать в себя одно или больше вычислительных устройств 102-1 через 102-N (в общем, называемых "процессорами 102" или процессорными устройствами 102"). Процессоры 102 могут связываться через взаимное соединение или шину 104. Каждый процессор 102 может включать в себя различные компоненты, некоторые из которых для ясности описаны со ссылкой на процессор 102-1. В соответствии с этим, каждый из остальных процессоров 102-2-102-N может включать в себя некоторые или аналогичные компоненты, описанные со ссылкой на процессор 102-1.

В одном варианте осуществления процессор 102-1 может включать в себя одно или больше процессорных ядер 106-1-106-М (называются здесь "ядрами 106", или в более общем случае, "ядром 106"), кэш 108 (который может включать в себя один или больше частных или совместно используемых кэш) и/или маршрутизатор 110. Процессорные ядра 106 могут быть воплощены на одном кристалле интегральной схемы (IC). Кроме того, IC может включать в себя один или больше совместно используемых и/или частных кэш (таких как кэш 108), шин или взаимных соединений (таких как шина или взаимное соединение 112), контроллеров памяти или других компонентов.

Маршрутизатор 110 может использоваться для обмена данными между различными компонентами процессоров 102-1 и/или системой 100. Кроме того, процессоры 102-1 могут включать в себя больше чем один маршрутизатор 110. Кроме того, множество маршрутизаторов 110 могут связываться друг с другом для обеспечения передачи данных между различными компонентами внутри или за пределами процессора 102-1.

Кэш 108 может содержать данные (например, включающие в себя инструкции), которые используются одним или больше компонентами процессора 102-1, такими как ядра 106. Например, кэш 108 может локально содержать данные, сохраняемые в памяти 114 для более быстрого доступа компонентами процессора 102. Как показано на фиг. 1, память 114 может сообщаться процессорами 102 через взаимное соединение 104. В одном варианте осуществления кэш 108 может представлять собой, по меньшей мере, кэш последнего уровня (LLC). Кроме того, каждое из ядер 106 может включать в себя кэш 116 уровня 1 (L1) (в общем, называется здесь "кэш 116 L1"). Кроме того, процессор 102-1 также может включать в себя кэш среднего уровня, который совместно используется несколькими ядрами 106. Различные компоненты процессора 102-1 могут связываться с кэш 108 непосредственно, через шину (например, шину 112), и/или контроллер памяти, или концентратор.

В одном варианте осуществления, устройство 102-1 обработки воплощает неограниченную НТМ. Как описано выше, НТМ воплощена в виде аппаратных средств и обеспечивает для потов возможность параллельного упреждающего исполнения критических участков, называемых транзакциями. Если возникает конфликт во время исполнения, тогда потоки останавливают или выполняют возврат их транзакций и снова исполняют для разрешения конфликта. Неограниченная НТМ в вариантах осуществления использует традиционную, ограниченную конструкцию НТМ и затем встраивает в нее преобразованные в последовательную форму неограниченные аппаратные транзакции. Ограниченность относится к пределу (скрытому или явно выраженному), установленному в отношении размера (например, количество операций и т.д.) транзакций, исполняемых в соответствии с конструкцией НТМ. Например, из-за ограничения размера кэш, существует предел для набора записей (доступа к сохранению в памяти, выполняемому транзакцией) для транзакции, которая может отслеживаться с помощью аппаратных средств (например, кэш, таких как кэш 116 L1, в некоторых воплощениях НТМ). После достижения этого предела, транзакция должна быть отменена, поскольку аппаратные средства больше не отслеживают точно доступ к памяти транзакции, исключая, таким образом, точный возврат транзакции, если возникает конфликт. Как описано выше, предыдущие решения НТМ обеспечивают возможность работы программного обеспечения возврата в связи с этой проблемой ограниченности. Неограниченная транзакция включает в себя транзакцию, которая может исполняться без каких-либо пределов в отношении размера транзакции.

В одном варианте осуществления неограниченные НТМ, в соответствии с вариантами осуществления раскрытия используют дополнительные неограниченные компоненты 118 (UB) НТМ для выполнения одной неограниченной транзакции в аппаратных средствах без упреждающего исполнения (например, без пометки битов транзакции в кэш 116 L1), параллельно с множеством ограниченных транзакций. Компоненты 118 UB НТМ могут включать в себя счетчик и логическую схему повторной попытки для воплощения аппаратного менеджера разногласий, как описано дополнительно ниже со ссылкой на фиг. 2. Глобальная аппаратная блокировка (GHWL) 120 в памяти 114 получается в результате неограниченной транзакции, и она должна быть считана всеми ограниченными транзакциями прежде, чем они будут выполнены. Для исключения состязания между ограниченными транзакциями и неограниченной транзакцией, ограниченные транзакции при выполнении транзакций считывают GHWL 120, чтобы проверить, поддерживается ли она. Если GHWL 120 выполняется, что обозначает, что исполняется неограниченная транзакция, ограниченные транзакции должны быть отменены для исключения недетектированных конфликтов. В некоторых вариантах осуществления CPU ID 125 также ассоциирован с GHWL 120, и может использоваться для идентификации ядра 106, которое исполняет свои операции в неограниченном режиме, с целью определения, когда поток должен выпустить GHWL 120, как дополнительно описано ниже. Поскольку в неограниченной транзакции не используется упреждающее исполнение, она всегда исполняется, в результате чего, обеспечивается гарантия продвижения при пересылке. При таком подходе ограниченные аппаратные транзакции все еще выполняются параллельно, как и в оригинальных конструкциях НТМ, поэтому, параллельная обработка не теряется при исполнении только этих типов транзакций.

На фиг. 2 иллюстрируется блок-схема ядра 106 процессора, в соответствии с вариантом осуществления раскрытия. В одном варианте осуществления ядро 106 процессора является таким же, как и ядро 106 процессора, описанное со ссылкой на фиг. 1. Стрелки, показанные на фиг. 2, могут иллюстрировать поток инструкций через ядро 106. Одно или больше ядер процессора (таких как ядро 106 процессора) могут быть воплощены на одном кристалле IC (или на одной подложке), как описано со ссылкой на фиг. 1. Кроме того, кристалл может включать в себя один или больше совместно используемых и/или частных кэш (например, кэш 108 на фиг. 1), взаимных соединений (например, взаимных соединений 104 и/или 112 по фиг. 1), контроллеров памяти или других компонентов. В одном варианте осуществления ядро 106 процессора, показанное на фиг. 2, может использоваться для обеспечения неограниченной транзакционной памяти с гарантиями продвижения при пересылке, используя аппаратную глобальную блокировку.

Как показано на фиг. 2, ядро 106 процессора может включать в себя модуль 202 выборки, предназначенный для выборки инструкций для исполнения ядром 106. Инструкции могут быть выбраны из любого устройства сохранения, такого как память 114 на фиг. 1 и/или другие устройства памяти. Ядро также может включать в себя модуль 204 декодирования, предназначенный для декодирования выбранных инструкций. Например, модуль 204 декодирования может декодировать выбранную инструкцию во множество микроопераций (uops).

Кроме того, ядро 106 может включать в себя модуль 206 планирования. Модуль 206 планирования может выполнять различные операции, ассоциированные с сохранением декодированных инструкций (например, принятых из модуля 204 декодирования), до тех пор, пока инструкции не будут готовы к отправке, например, до тех пор, пока все значения источника декодированных инструкций не станут доступными. В одном варианте осуществления модуль 206 планирования может планировать и/или вырабатывать (или пересылать) декодированные инструкции в исполнительный модуль 208, для исполнения. Исполнительный модуль 208 может исполнять пересылаемые инструкции после их декодирования (например, модулем 204 декодирования) и пересылки (например, модулем 206 планирования). В варианте осуществления исполнительный модуль 208 может включать в себя больше, чем один исполнительный модуль, такой как исполнительный модуль памяти, исполнительный модуль целых чисел, исполнительный модуль для работы с плавающей точкой или другие исполнительные модули. Кроме того, исполнительный модуль 208 может исполнять инструкции не по порядку. Следовательно, ядро 106 процессора может представлять собой ядро процессора, работающие не по порядку в одном варианте осуществления.

Ядро 106 также может включать в себя модуль 210 изъятия инструкции. Модуль 210 изъятия инструкции может изымать исполненные инструкции после их выполнения. В варианте осуществления изъятие выполненных инструкций может привести к тому, что состояние процессора будет фиксировано без исполнения инструкций, физические регистры, используемые инструкциями, будут откреплены и т.д.

Как показано на фиг. 2, ядро 106 может включать в себя буфер 212 изменения порядка (ROB), предназначенный для сохранения информации об инструкциях, запущенных на исполнение (или uops) для доступа различными компонентами ядра 106. Ядро 106 может дополнительно включать в себя таблицу псевдонима регистра (RAT) 214 для поддержания отображения логических (или архитектурных) регистров (таких как регистры, идентифицированные операндами программных инструкций) для соответствующих физических регистров. В одном варианте осуществления каждый вход в RAT 214 может включать в себя идентификатор ROB, назначенный для каждого физического регистра. Кроме того, буфер порядка памяти (MOB), который может включать в себя буфер нагрузки или буфер сохранения, может сохранять находящиеся на исполнении операции в памяти, которые не были загружены или записаны обратно в память (например, память, которая является внешней для ядра 106, такая как память 114). Кроме того, ядро 106 может включать в себя модуль 220 шины, который обеспечивает возможность обмена данными между компонентами ядра 106 и другим компонентом (такими как компоненты, описанные со ссылкой на фиг. 1) через одну или больше шин (например, шины 104 и/или 112) из памяти 114, перед сохранением принятых данных в кэш 116.

Кэш 116 L1 может включать в себя одну или больше линий 224 кэш (например, линии 0-N кэш). В одном варианте осуществления каждая линия 224 кэш может включать в себя бит 226 упреждающего исполнения для каждого потока, исполняемого в ядре 106. Бит 226 упреждающего исполнения может быть установлен или сброшен для обозначения доступа (загрузки и/или исполнения) в соответствующей линии кэш по запросу на доступ к транзакционной памяти. Даже при том, что линии 224 кэш показаны, как имеющие соответствующий бит 226 упреждающего исполнения, также возможны другие конфигурации. Например, линия 224 кэш может иметь бит считывания транзакции и бит записи транзакции. В качестве другого примера, бит 226 упреждающего исполнения может соответствовать выбранному участку кэш 116, такому как блок данных кэш, или другому участку кэш 116. Кроме того, бит 226 упреждающего исполнения может быть сохранен в других местах, кроме кэш 116, таких как, например, кэш 108 на фиг. 1, память 114 или кэш "жертвенных" данных.

Ядро 106 также может воплощать НТМ на основе кэш для вариантов осуществления ограниченных транзакций. Транзакционные операции помечены путем установки транзакционных битов, таких как бит 226 упреждающего исполнения, ассоциированный с линиями 224 кэш. В некоторых вариантах осуществления конфликты могут быть детектированы при гранулярности линии кэш, используя протокол когерентности кэш. Если линия 224 кэш, доступ к которой осуществляется через транзакции, становится опустошенной, транзакция затем отменяется. Вместо использования возврата программными средствами при отмене транзакции в вариантах осуществления раскрытия, вводится компонент 230 аппаратного менеджера исполнения НТМ, и счетчик 235 повторной попытки НТМ для воплощения неограниченной транзакционной памяти с гарантиями продвижения при пересылке, используя аппаратную глобальную блокировку (GHWL), такую как GHWL 120 на фиг. 1. Компонент 230 аппаратного менеджера исполнения НТМ рассматривают причину отмены, в некоторых случаях, и принимает решение, следует ли использовать политику повторной попытки, отслеживаемой счетчиком 235 повторной попытки НТМ (например, в случае конфликта) или начать неограниченную транзакцию. GHWL 120 также должен быть считан при выполнении транзакции всеми ограниченными транзакциями, для правильной синхронизации с неограниченными транзакциями.

На фиг. 3А показан пример листинга псевдокода, иллюстрирующего синтаксис транзакции. Как показано, в листинге 300 кода представлен пример программного кода, который исполняет транзакцию, и листинг 310 кода обеспечивает соответствующую аппаратную транзакцию листинга 300 программных средств с помощью устройства обработки, такого как ядро 106. Варианты осуществления раскрытия не ограничены конкретными формулировками инструкций и/или терминологией, представленной в листингах 300, 310, и могут воплощать другие вариации этих инструкций. Как представлено в программном листинге 300, критический участок инициируется TX_BEGIN для обозначения начала транзакции, и заканчивается TX_END, для обозначения конца транзакции.

Аппаратный листинг 310 показывает, что после первого исполнения, эти инструкции (например, TX_BEGIN) инициируют ограниченную аппаратную транзакцию. На фиг. 3В показан пример листинга псевдокода аппаратных инструкций, ассоциированных со ограниченной транзакцией. Поток, исполняющий ограниченную аппаратную транзакцию может начать упреждающее исполнение, когда GHWL 120 является свободным. В одном варианте осуществления, в качестве части критического участка упреждающего исполнения, исполняется инструкция, обеспечивающая упреждающее исполнение (например, такая как "enable_spec_writes") ядром 116, что приводит к отслеживанию транзакционных операций, путем установки транзакционных битов, таких как бит 226 упреждающего исполнения, ассоциированный с линиями 224 кэш для кэш 116 L1 (или любого другого кэш и/или памяти, используемой для воплощения НТМ), доступ к которой осуществляется соответствующими транзакционными операциями.

Если транзакция не исполняется, и ее отменяют из-за конфликта (как обозначено аппаратным статусом отмены, который может быть сохранен в специализированном регистре 240 ядра 106), тогда счетчик 235 повторной попытки НТМ может быть последовательно увеличен. Счетчик 235 повторной попытки НТМ может представлять собой накопитель, который отслеживает отмены для каждой транзакции. Политика повторной попытки, которая может быть воплощена аппаратным компонентом 230 управления разногласиями НТМ, определяет, следует ли выполнить повторную попытку транзакции, как ограниченной аппаратной транзакции или следует ли ее повторно назначать, как неограниченную аппаратную транзакцию. В некоторых вариантах осуществления к считчику 235 повторной попытки НТМ можно обращаться для определения, было ли достигнуто пороговое число повторных попыток транзакции. Если это так, тогда ограниченная транзакция может быть преобразована в неограниченную транзакцию с гарантией продвижения при пересылке и со сбросом счетчика 235 повторной попытки НТМ.

В других вариантах осуществления, если причина отмены представляет собой неподдерживаемую инструкцию или переполнение, транзакцию повторно запускают непосредственно, как неограниченную аппаратную транзакцию, и выполняют сброс счетчика 235 повторных попыток НТМ. Такие преобразования ограниченных и неограниченных транзакций являются прозрачными для программиста, и ими могут управлять аппаратные средства НТМ ядра 106, такие как аппаратный компонент 230 менеджера содержания НТМ.

Варианты осуществления раскрытия поддерживают одновременное исполнение одной неограниченной транзакции с любым количеством ограниченных транзакций. Процесс, который исполняет неограниченную транзакцию, должен получать GHWL 120 для обеспечения того, что больше нет других неограниченных транзакций, работающих одновременно, как показано в примерном листинге 330 псевдокода аппаратных инструкций, ассоциированных с неограниченной транзакцией на фиг. 3С. Неограниченная транзакция выполняет все записи на месте (то есть, без упреждающего исполнения), делая их видимыми для параллельных считывателей (например, других потоков). По этой причине неограниченные транзакции не могут быть отменены в вариантах осуществления раскрытия.

Кроме того, неограниченные транзакции не помечают биты транзакции, такие как биты 226 упреждающего исполнения, в линиях 224 кэш, к которым они обращаются. В одном варианте осуществления это ограничено с тем, что НТМ не исполняет инструкцию для обеспечения записей упреждающего исполнения (например, "enable_spec_writes"), при начале неограниченной транзакции. Поэтому, линии 224 кэш, доступ к которым выполняют неограниченные транзакции, могут быть удалены из кэш 116 без последствий.

В некоторых вариантах осуществления, когда транзакция заканчивается (например, как часть процедуры TX_END, предоставляемой аппаратными средствами ядра 106), транзакция может проверять, была ли выполнена GHWL 120, и также может сравнивать CPU ID ядра 106 с CPU ID 125, сохраненным с GHWL 120. Если присутствует соответствие, тогда поток мог быть знать, что он является неограниченным и мог бы очистить CPU ID 125 и снять GHWL 120. Если соответствие отсутствует или если CPU ID весь занят нулями, тогда поток мог быть знать, что он находится в ограниченном режиме и может выполнять изменения в кэш 116, которые помечены, как предназначенные для упреждающего исполнения в памяти, среди других задач, выполняемых, как часть окончания транзакции.

В результате описанных выше вариантов осуществления, неограниченные транзакции не отменяют в кэш и при ассоциативных переполнениях. Поскольку неограниченные транзакции не могут быть отменены, они также поддерживают инструкции, которые являются нелегальными в ограниченных транзакциях, такие как системные вызовы и I/O. В конечном итоге, ограниченная транзакция, которая постоянно отменяется из-за конфликтов, может быть повторно запущена, как неограниченная транзакция (например, используя политику повторной попытки и счетчик повторной попытки, описанный выше), что гарантирует, что она будет успешной; и это свойство обеспечивает продвижение при пересылке.

При наивном подходе, используя такую конструкцию, состязания должны быть исключены между неограниченной транзакцией и ограниченными транзакциями. Это может быть обработано, благодаря чтению GHWL 120 неограниченными транзакциями (при выполнении транзакции), как описано выше, предотвращая, таким образом, исполнение ограниченных транзакций параллельно с неограниченной транзакцией. Когда ограниченная транзакция считывает GHWL 120 в начале исполнения, GHWL 120 добавляют в считанный набор транзакций. Если ограниченная транзакция начинает исполнение, в то время как GHWL 120 не поддерживается, и впоследствии ее получают (то есть, начинается неограниченная транзакция), ограниченная транзакция, вследствие этого, отменяется из-за конфликта транзакций, идентифицированного в НТМ, в результате конфликта по адресу GHWL 120 в считанном наборе ограниченных транзакций. Этот конфликт автоматически определяется по протоколу когерентности, используемому ядром 106 и воплощением НТМ.

В некоторых вариантах осуществления считывание GHWL 120 может быть оптимизировано, для поддержки параллельного исполнения ограниченных транзакций вместе с одиночной неограниченной транзакцией. Вместо регулярной отмены таких транзакций, в результате требования считывания ограниченными транзакциями GHWL 120 в момент начала транзакции, варианты осуществления раскрытия следят за тем, чтобы правильность была обеспечена, если GHWL 120 считывают во время исполнения ограниченной транзакции. В результате, НТМ может запускать любое количество ограниченных транзакций одновременно с одной неограниченной транзакцией.

В частности, как показано в листинге 400 псевдокода на фиг. 4А, если ограниченные транзакции считывают GHWL 120 во время исполнения транзакции, после исполнения критического участка, а не перед этим, возможна определенная конкуренция между разными типами транзакций. При таких установках неограниченная транзакция должна сделать свои изменения видимыми для ограниченной транзакции, для поддержания возможности последовательного представления; и, поэтому, упреждающее исполнение неограниченной транзакции становится невозможным. На фиг. 4В и 4С показаны блок-схемы, концептуально иллюстрирующие примерные сценарии, в которых такая оптимизация со считыванием GHWL обеспечива