Нечувствительный к задержке буфер транзакции для связи с квитированием

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в уменьшении зависимости глубины буфера транзакций от латентности связи с квитированием. Устройство для обработки транзакций содержит блок хранения данных транзакций для хранения данных транзакций, подлежащих передаче по межкомпонентному соединению; буфер транзакций для буферизации части данных транзакций и логический блок транзакций для передачи сигнала с запросом (REQ) арбитру в ответ на первые данные транзакций, которые становятся доступными в блоке хранения данных транзакций, извлечения в ответ на сигнал разрешения (GNT), принимаемый от арбитра, вторых данных транзакций из буфера транзакций и передачи вторых данных транзакций на межкомпонентное соединение и пополнения буфера транзакций третьими данными транзакций, извлекаемыми из блока хранения данных транзакций, после передачи вторых данных транзакций на межкомпонентное соединение, при этом логический блок транзакций выполнен с возможностью увеличения значения счетчика в ответ на определение, что буфер транзакций заполнен после передачи сигнала REQ, причем значение счетчика представляет собой число сигналов REQ, на которые не поступил ответ и чьи ассоциированные данные транзакций не были буферизованы в буфере транзакций. 3 н. и 11 з.п. ф-лы, 27 ил., 1 табл.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся в основном к интерфейсам компьютерных систем. В частности, варианты осуществления изобретения относятся к нечувствительному к задержке буферу транзакций для протоколов связи с квитированием систем система-на-кристалле.

Уровень техники

Основные микросхемы процессоров, как высокопроизводительных, так и низкоэнергетических, все чаще выполняют дополнительные функции, например, графические, функции устройств отображения, функции модулей безопасности, функции PCIe ™ портов (т.е., портов в соответствии со спецификацией взаимного соединения периферийных компонентов (PCI Express ™ (PCIe ™)) базовой спецификации версии 2.0 (опубликована в 2007 г.) (далее упоминается как PCIe ™ спецификация) и других PCIe ™ на основе периферийных устройств, предоставляя при этом унаследованную поддержку устройствам, совместимых с PCI спецификацией, такой как спецификацией взаимного соединения периферийных компонентов (PCI) спецификации локальной шины, версия 3.0 (опубликована в 2002 г.) (здесь и далее, упоминается как PCI спецификация).

Такие конструкции высоко сегментированы из-за наличия различных спецификаций сервера, настольных, мобильных, встраиваемых, ультра мобильных и мобильных интернет устройств. Различные рынки стремятся использовать единую микросхему система-на-кристалле (SoC или SOC), сочетающая, по меньшей мере, некоторые из ядро процессора, контроллеров памяти, контроллеров ввода/вывода и других элементов сегмента удельного ускорения на одной микросхеме. Тем не менее, конструкции, которые аккумулируют эти признаки, не получили широкое распространение из-за трудностей интеграции различных компонентов (IP) архитектуры, охраняемые законом об авторском праве, или агентов на одном кристалле. Это особенно проявляется в том, что IP-блоки могут иметь различные спецификации и уникальную конструкцию, и могут потребовать использования множества специализированных проводов, коммуникационных протоколов и так далее, чтобы совместить их на SoC. В результате, каждая SoC или другое передовое полупроводниковое устройство, которое было разработано, имеет более сложную конструкцию и процедуру адаптации к специфическим требованиям для инкорпорирования различных IP-блоков в одном устройстве.

При использовании протокола связи с квитированием (и тому подобное) IP агент должен быть подключен к соединению (или структуре, шине) для получения права использования или прав доступа на взаимодействие, отправив сигнал с запросом (REQ) арбитру, и приняв сигнал (GNT) разрешения от арбитра, прежде чем будет осуществлена передача транзакции в соединение. Как правило, как показано на фиг. 1, устройство временного хранения информации (здесь и далее обозначается как буфер транзакций) реализуется как буфер транзакций или транзакции, относящейся к данным (извлекаемые из устройства хранения данных транзакций, например, регистры), для которых "REQ" уже был размещен на IO структуре подсистемы в качестве примера. Когда принимается "GNT", соответствующая транзакция извлекается из буфера транзакций и поставляется в IO структуры подсистемы, как показано на фиг. 1. В результате, глубина этого буфера транзакций зависит от латентности связи с квитированием для заданной полосы пропускания и устойчивости к задержке. Когда IP агент перемещается в пределах IO структуры подсистемы или меняет свои требования к латентности, то изменяется латентность связи с квитированием, что оказывает воздействие на глубину буфера транзакций.

Краткое описание чертежей

Варианты осуществления настоящего изобретения проиллюстрированы в качестве примера, и не ограничиваются описанием, приведенным на прилагаемых чертежах, на которых одинаковые ссылочные позиции указывают одинаковые элементы.

Фиг. 1 представляет собой схему, иллюстрирующую типичные транзакции узла.

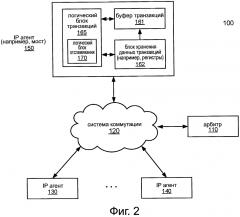

Фиг. 2 представляет собой блок-схему, иллюстрирующую базовую архитектуру межкомпонентного соединения в соответствии с вариантом осуществления.

Фиг. 3 представляет собой блок-схему алгоритма, иллюстрирующую процесс обработки протокола связи с квитированием согласно одному варианту осуществления.

Фиг. 4 представляет собой блок-схему алгоритма, иллюстрирующую механизм обработки транзакции в соответствии с другим вариантом осуществления.

Фиг. 5 представляет собой блок-схему алгоритма, иллюстрирующую способ обработки транзакции протоколов связи с квитированием согласно одному варианту осуществления.

Фиг. 6А и 6В показывают блок-схемы, иллюстрирующие систему система-на-кристалле в соответствии с одним вариантом осуществления.

Фиг. 7А иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 7В иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 7С иллюстрирует примерный формат команд расширения системы команд (AVX) в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 8А представляет собой блок-схему, иллюстрирующую общий формат векторных команд и их шаблоны команд класса А, в соответствии с вариантами осуществления изобретения.

Фиг. 8В показывает блок-схему, иллюстрирующую общий формат векторных команд и их шаблоны команд класса В, в соответствии с вариантами осуществления изобретения.

Фиг. 9А показывает блок-схему, иллюстрирующую примерный конкретный формат векторных команд, в соответствии с одним вариантом осуществления изобретения.

Фиг. 9В изображает блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 9С показывает блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 9D представляет собой блок-схему, иллюстрирующую общий формат векторных команд, в соответствии с другим вариантом осуществления изобретения.

Фиг. 10 представляет собой блок-схему архитектуры регистра в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 11а представляет собой блок-схему, иллюстрирующую пример упорядоченного конвейера и пример переименования регистра конвейером с изменением последовательности выполнения команд в соответствии с вариантами осуществления изобретения.

Фиг. 11В представляет собой блок-схему, иллюстрирующую пример варианта осуществления архитектуры ядра с логикой последовательного выполнения команд и пример переименования регистра архитектурой ядра с логикой изменения последовательности выполнения команд, включенного в состав процессора, в соответствии с вариантами осуществления изобретения.

Фиг. 12А показывает блок-схему ядра процессора в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 12В показывает блок-схему ядра процессора в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 13 представляет собой блок-схему процессора согласно вариантам осуществления настоящего изобретения.

Фиг. 14 представляет собой блок-схему системы в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 15 представляет собой блок-схему более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 16 показывает блок-схему более конкретного примера системы в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг. 17 показывает блок-схему SoC в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 18 представляет собой блок-схему, которая иллюстрирует пример контрастного использования преобразователя команд программного обеспечения для преобразования двоичных команд в наборе команд источника в двоичные команды в целевом наборе команд в соответствии с вариантами осуществления изобретения.

Описание вариантов осуществления

Различные варианты осуществления и аспекты изобретения будут описаны со ссылкой на подробное приведенное ниже описание и на прилагаемые чертежи, которые иллюстрируют различные варианты осуществления. Нижеследующее описание и чертежи иллюстрируют изобретение и не должны быть истолкованы как ограничивающие изобретение. Многочисленные конкретные подробности описаны ниже для обеспечения полного понимания различных вариантов осуществления настоящего изобретения. Тем не менее, в некоторых случаях, хорошо известные или типовые детали не описаны с целью обеспечения более краткого описания вариантов осуществления настоящего изобретения.

Ссылка в описании на "один вариант осуществления" или "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанные в связи с вариантом осуществления, могут быть включены в состав, по меньшей мере, одного из вариантов осуществления изобретения. Употребление фразы "в одном из вариантов" в различных местах описания, не обязательно все относится к одному и тому же варианту осуществления.

Варианты осуществления, описанные здесь, могут быть использованы во многих различных типах систем. В качестве примеров реализации, описанные здесь, могут быть использованы с применением полупроводниковых приборов, таких как процессоры или другие полупроводниковые устройства, которые могут быть изготовлены на одном полупроводниковом кристалле. В конкретной реализации, устройство может представлять собой систему-на-кристалле (SoC) или другой усовершенствованный процессор, который включает в себя различные однородные и/или гетерогенные агенты обработки и дополнительные компоненты, такие как сетевые компоненты, например, маршрутизаторы, контроллеры, мосты, память и так далее.

Некоторые варианты реализации могут быть использованы в полупроводниковом устройстве, которое реализовано в соответствии с заданной спецификацией, такой как спецификация структуры интегрированной системы на кристалле (IOSF), разработанной Intel® Corporation, изготовленной производителем полупроводника, чтобы обеспечить стандартизированный протокол межкомпонентного соединения на кристалле для установки компонентов архитектуры (IP), защищенных авторским правом, внутри SoC или другой микросхемы. Такие ЕР блоки могут представлять собой различные компоненты, включающие в себя универсальные процессоры с логикой последовательного выполнения команд и ядро с логикой изменения последовательности выполнения команд, блоки фиксированных функций, графические процессоры, контроллеры и многих другие. Благодаря стандартизации протокола межкомпонентного взаимодействия, инфраструктура, таким образом, реализуется для широкого использования ЕР агентов в различных типах микросхем. Соответственно, изготовитель полупроводниковых устройств может не только эффективно проектировать различные типы микросхем для различных клиентов, но может также с помощью спецификации предоставлять возможность третьим сторонам разрабатывать логические устройства, такие как IP агенты, которые будут включены в структуру таких микросхем. И, кроме того, путем предоставления нескольких вариантов различных аспектов протокола межкомпонентного соединения, повторным использованием конструкций, можно добиться наличия эффективной компоновки. Хотя варианты осуществления описаны здесь с использованием IOSF спецификации, очевидно, что объем настоящего изобретения не ограничивается в этом отношении, и варианты осуществления могут быть использованы во многих различных типах систем.

Согласно некоторым вариантам осуществления, предусматривается новый подход, который полностью устраняет зависимость буфера транзакции от латентности связи с квитированием. В этом подходе, глубина буфера транзакций зависит от латентности доступа для чтения набора регистров, из которого извлекаются транзакции. Буфер транзакций используется только для хранения фиксированного числа первоначально приостановленных транзакций (например, соответствующие запросы были отправлены, но соответствующие подтверждения не были приняты от арбитра). Когда буфер транзакций заполнен, запросы (REQ) новых транзакций отправляются независимо и ведется подсчет таких приостановленных запросов. Поскольку гарантируется, что сигнал (GNT) разрешения поступит в порядке, в котором были сделаны запросы (для данного класса потока/виртуального канала (FC/VC) канал), то будет обеспечена надлежащая сохранность только первоначальных транзакции в буфере транзакций на FC/VC канале. Каждый раз, прием GNT предохраняет буфер транзакций от переполнения, если не подтвержденный REQ был отправлен без сохранения соответствующей транзакции внутри буфера транзакций, то такие транзакции извлекаются из набора регистров для пополнения буфера транзакций.

Фиг. 2 представляет собой блок-схему, иллюстрирующую базовую архитектуру межкомпонентного соединения в соответствии с вариантом осуществления. Как показано на фиг. 2, система 100 может быть частью системы-на-кристалле или другого полупроводникового устройства, и включает в себя систему 120 коммутации, которая действует в качестве межкомпонентного соединения между различными компонентами. В примере, как показано, эти компоненты включают в себя IP агенты 130 и 140, которые могут быть независимыми IP блоками для обеспечения различных функциональных возможностей, таких как вычислительных, графических и так далее. Эти IP агенты являются, таким образом, IP блоками или логическими устройствами, имеющие интерфейс, совместимый со спецификацией IOSF, в одном варианте осуществления. Как далее видно, сеть 120 также взаимодействует с мостом 150, который также может быть IP агентом. Хотя это не показано для простоты иллюстрации в варианте на фиг. 1, мост 150 может работать в качестве интерфейса с другими компонентами системы, например, на той же микросхеме или на одной или нескольких различных микросхемах. Например, мост 150 может представлять собой любое из устройств сопряжения в системе, такое как мосты 920 и 985, показанные на фиг. 6А и 6В.

Как будет описано дополнительно ниже, каждый из элементов, показанный на фиг. 2, а именно сеть 120, IP агенты 130 и 140, мост 150 могут включать в себя один или несколько интерфейсов для осуществления обработки различных коммуникационных сигналов. Эти интерфейсы могут быть определены в соответствии со спецификацией IOSF, которая определяет коммуникационные сигналы на этих интерфейсах, протоколы, используемые для обмена информацией между агентами, арбитраж и механизмы управления потоком, используемые для инициирования и организации обмена информацией, поддержанные декодированием адреса и возможностями преобразования, обмен сообщениями при полосной или внеполосной коммуникации, управление мощностью, тестирование, проверку достоверности и отладку.

Как описано выше, когда IP агент, такой как IP агент 150, пытается отправить данные в систему 120 коммутации, IP агент 150 должен послать REQ сигнал (например, устанавливая REQ линию, ассоциированную с IP агентом) арбитру 110 и ждать GNT сигнал, принятый от арбитра 110 (который одобрен арбитром 110). После приема GNT от арбитра 110, IP агент 150 должен послать транзакцию в последующем цикле в систему 120 коммутации. После того, как IP агент 150 послал REQ арбитру 110 и ожидает GNT сигнал от арбитра 110, новые данные транзакции могут быть приняты и сохранены в блоке хранения транзакций, таком как регистры, IP агентом 150. В обычной системе IP агент 150 буферизует новые данные транзакции в буфере транзакции в ожидании GNT от арбитра, что может занять длительный период времени. В результате, буфер транзакций может потребовать большей емкости хранения для удержания всех приостановленных транзакций. Данная величина емкости хранения напрямую зависит от латентности связи с квитированием.

Согласно одному варианту осуществления, по меньшей мере, один из ЕР агентов 130, 140 и 150, в этом примере, IP агент 150 включает в себя буфер 162 транзакций фиксированного размера, который хранит только фиксированное количество данных приостановленных транзакций, в то время как остальные данные транзакций могут по-прежнему удерживаться в блоке 161 хранения данных транзакций. В одном варианте осуществления, со ссылкой на фиг. 2 и фиг. 3, в качестве примера, когда IP агент 150 принимает новые данные транзакции, которые становятся доступными в блоке 162 хранения данных транзакций, которые должны быть переданы в систему 120 коммутации, логическое устройство 165 транзакций посылает REQ в адрес арбитра 110 (через тракт 301). Логическое устройство 165 транзакций посылает новый REQ арбитру 110 независимо от того, был ли принят GNT от арбитра 110.

Кроме того, в соответствии с одним вариантом осуществления, логическое устройство 165 транзакций определяет, имеет ли буфер 161 транзакций достаточно места для буферизации новых данных о транзакции. Если буфер 161 транзакции имеет достаточно места для буферизации новых данных, то логическое устройство 165 транзакций извлекает новые данные транзакций из блока 162 хранения данных транзакций и сохраняет извлеченные данные в буфер 161 транзакций (через тракт 302В). Если буфер 161 транзакции не имеет достаточного места для буферизации новых данных, то логическое устройство 165 транзакций обновляет логическое устройство 170 отслеживания. Логическое устройство 170 отслеживания выполнено с возможностью отслеживать число не подтвержденных REQs, чьи данные не были буферизованы в буфер 161 транзакций. В частности, в соответствии с одним вариантом осуществления, логическое устройство 165 транзакций увеличивает значение счетчика 170 (через тракт 302А), оставляя новые данные транзакций в блоке 162 хранения данных транзакций. Указанное счетчиком 170 значение представляет число не подтвержденного или приостановленного REQs, чьи данные транзакций не были буферизованы в буфер 161 транзакций. То есть, значение счетчика 170 представляет собой число транзакций, которые соответствует отправленным REQs, но их ассоциированные данные транзакций не были буферизованы в буфер 161 транзакций (например, до сих пор хранятся в блоке 162 хранения данных транзакций). Следует отметить, что данные транзакции, сохраненные в буфере 161 транзакций, могут быть обновлены посредством тракта 302В или логического устройства 170 отслеживания (например, соответствующее значение счетчика увеличивается), прежде чем его REQ подается в тракт 301.

Впоследствии, когда GNT принимается от арбитра 110 (по тракту 303), который может быть асинхронным или параллельным по отношению к операциям в трактах 302А и 302В, в одном варианте осуществления, логическое устройство 165 транзакций извлекает следующие данные транзакций соответственно (если существуют) из буфера 161 транзакций и помещает извлеченные данные в систему 120 коммутации (через тракт 304). Кроме того, логическое устройство 165 транзакций определяет, имеется ли какой-либо не подтвержденный или приостановленный REQ посредством проверки значения счетчика 170. Если значение счетчика 170 больше, чем заданное пороговое значение, такое как ноль, то это означает, что существует, по меньшей мере, один неподтвержденный REQ. В такой ситуации, логическое устройство 165 транзакций извлекает следующие данные транзакции соответственно из блока 162 хранения данных транзакций и помещает их в буфер 161 транзакций (по тракту 305), и уменьшает показания счетчика 170 (по тракту 306). В результате, размер буфера 161 может поддерживаться на относительно небольшой величине, с обеспечением достаточной степени латентности доступа к блоку 162 хранения данных транзакций.

Фиг. 4 представляет собой блок-схему алгоритма, иллюстрирующую механизм обработки транзакции в соответствии с другим вариантом осуществления. Как показано на фиг. 4, в этом варианте осуществления, способы, описанные выше, могут быть применены к ситуации, в которой данные нескольких каналов/полос (например, виртуальные каналы/полосы) с множеством классов (например, классы потоков), передаются по межкомпонентному соединению или систему коммутаций. Каждый канал может дополнительно нести несколько различных классов данных. Согласно одному варианту осуществления, буфер (например, буферы 161А - 161N) поддерживается для буферизации данных каждой из комбинации канала/полосы и класса (канал /класс). Для каждого канала/класса, конкретный счетчик (например, счетчики 170) и указатель отсчета (например, указатели 404 отсчета) поддерживаются логическим устройством 403 пополнения буфера, где логическое устройство 403 пополнения буфера осуществляет извлечение соответствующих данных конкретного канала/класса из местоположения, на которое указывает соответствующий указатель отсчета, и размещает извлеченные данные в одном из буферов 161А - 161N, в соответствии с этим конкретным каналом/классом. То есть, для каждой комбинации канал/класс, существует соответствующий указатель отсчета и счетчик. Указатель отсчета указывает на место хранения блока 162 хранения транзакции, в котором в следующие имеющиеся данные соответствующего канала/класса, сохраняются, в то время как соответствующий счетчик сохраняет значение, представляющее номер неподтвержденного REQs этой конкретной комбинации канал/класс.

Когда GNT принят от арбитра 110, арбитр 402 транзакции определяет, какая из комбинаций канал/класс соответствует принятому GNT сигналу, и информирует логическое устройство 403 пополнения буфера о необходимости загрузить данные, ассоциированные с этим конкретным каналом/классом из блока 162 хранения и поместить данные в соответствующий один из буферов 161А - 161N. Арбитр 402 транзакции может поддерживать информацию, идентифицирующую неподтвержденные запросы, и информация может быть использована для ассоциирования принятых GNTs с неподтвержденными REQs. В ответ на это, логическое устройство 403 пополнения буфера проверяет значение счетчика, соответствующее принятому GNT, и извлекает следующие доступные данные транзакций из места хранения, на которое ссылается соответствующий указатель отсчета. В результате, большое количество данных конкретного канала/класса не будет блокировать данные другого канала/класса.

Фиг. 5 представляет собой блок-схему алгоритма, иллюстрирующую способ обработки транзакции протоколов связи с квитированием, согласно одному варианту осуществления. Способ 500 может быть выполнен путем обработки логическим устройством, которое может включать в себя программное обеспечение, аппаратные средства или их сочетание. Способ 500 может быть выполнен IP агентом, как описано выше. Как показано на фиг. 5, на этапе 501, в ответ на данные транзакции, которые будут передаваться посредством межкомпонентного соединения (например, система коммутации, шина), данные транзакции буферизуются в буфер транзакции, если буфер имеет достаточно места. На этапе 502, REQ представляется арбитру, который ассоциирован с межкомпонентным соединением. На этапе 503, в ответ на прием GNT от арбитра, данные транзакции затем извлекаются из буфера транзакции и передаются на межкомпонентное соединение. На этапе 504, логическое устройство обработки определяет, имеется ли какой-либо неподтвержденный REQ, например, путем проверки значения счетчика, который показывает число неподтвержденного REQ. Если это так, то на этапе 505, логическое устройство пополнения буфера осуществляет обработку данных, извлеченных из блока хранения транзакции (например, регистры) и, возможно, уменьшает показания счетчика, если это необходимо.

Фиг. 6А показывает блок-схему, иллюстрирующую систему система-на-кристалле в соответствии с одним вариантом осуществления. Как показано на фиг. 6А, SoC 900 может включать в себя различные компоненты, все из которых могут быть интегрированы на одном полупроводниковом кристалле для обеспечения различных возможностей обработки при высоких скоростях и малой мощности, занимая сравнительно небольшое пространство. SoC 900 включает в себя процессор или центральный процессор (CPU) 901, имеющий один или несколько процессорных ядер 905А и 906В. В различных вариантах осуществления, ядра 905 могут быть относительно простыми ядрами с логикой последовательного выполнения команд или более сложными ядрами с логикой выполнением команд с изменением их очередности. Или может быть использовано объединение простого и сложного ядер на одном SoC. Как видно, ядра 905 могут быть соединены с помощью когерентного межкомпонентного соединения 915, которое дополнительно подключает память 910, например, общий кэш последнего уровня (LLC). Хотя объем вариантов осуществления настоящего изобретения не ограничивается в этом отношении, в одном варианте осуществления когерентное межкомпонентное соединение 915 может быть реализовано в соответствии со спецификацией последовательной кэш-когерентной шиной типа точка-точка (QPI) ™, разработанной Intel Corporation, Santa Clara, California.

Согласно одному варианту осуществления, когерентное межкомпонентное соединение 915 может устанавливать связь через мост 920 с системой 950 коммутаций, которая может быть IOSF системой. Когерентное межкомпонентное соединение 915 дополнительно может устанавливать связь посредством интегрированного контроллера памяти с памятью вне кристалла (не показано для простоты иллюстрации варианта осуществления). Различные компоненты могут соединяться с системой 950 коммутации, которая включает в себя модуль 940 обработки контента (СРМ), который может использоваться для выполнения различных операций, таких как выполнение функций безопасности, криптографических функций и так далее. Кроме того, процессор 945 дисплея может быть частью конвейера обработки медиа информации для воспроизведения видео на ассоциированном дисплее.

Как дополнительно показано, система 950 коммутаций может дополнительно подключаться к другим IP агентам. Кроме того, для обеспечения связи с другими устройствами на кристалле, система 950 коммутации может дополнительно осуществлять связь с контроллером 960 PCIe ™ и контроллером 965 универсальной последовательной шины (USB), оба из которых могут взаимодействовать с различными устройствами в соответствии с этими протоколами. Наконец, как показано в варианте осуществления, мост 970, который может быть использован для связи с дополнительными компонентами других протоколов, такими как протокол открытого ядра (ОСР) или расширенная шинная архитектура микроконтроллеров (AMBA) ARM протокола. Хотя вариант осуществления показан с конкретными компонентами, следует понимать, что объем настоящего изобретения не ограничивается этим, и в различных вариантах осуществления могут применяться дополнительные или другие компоненты.

Более того, следует понимать, что хотя вариант реализации показан в виде одного кристалла SoC, варианты осуществления могут быть дополнительно реализованы в системе, в которой множество микросхем устанавливают связь друг с другом через иной, чем IOSF интерфейс. На фиг. 6В показана блок-схема системы в соответствии с другим вариантом осуществления настоящего изобретения. Как показано на фиг. 6В, SoC 925 включает в себя северный комплекс 902 и южный комплекс 903. Северный комплекс 902 может включать в себя множество компонентов, аналогичные тем, которые обсуждались выше, и дополнительный интерфейс вне кристалла. Соответственно, северный комплекс 902 может осуществлять связь с другой микросхемой 903, которая может включать в себя различные функциональные возможности для обеспечения связи между этими двумя микросхемами, а также с различными устройствами вне кристалла, такими как различные периферийные устройства, в соответствии с одним или более различными характеристиками. В частности, вторая микросхема 903 показана, как включающая в себя интерфейс вне кристалла, чтобы обеспечить связь с микросхемой 902 и который, в свою очередь, взаимодействует с системой 980 коммутации, которая может быть ОСР системой коммутации в соответствии с вариантом осуществления. Как видно, система 980 коммутации дополнительно может быть соединена с различными контроллерами для установления связи с устройствами вне кристалла, включающие в себя контроллер 960 PCIe ™, контроллер 965 USB и мост 985. Мост 958 может быть соединен с другой ОСР системой коммутации и т.д.

Различные IP блоки или агенты, описанные выше, представляют компоненты или функциональные блоки (то есть функциональные блоки), обычно используемые в SoC конструкциях, включающие в себя, но не ограничиваясь ядрами процессора, компонентами кэш-памяти и агентами, контроллерами памяти, I/O контроллерами и интерфейсами, периферийными устройствами и периферийными интерфейсами, видео и аудио компонентами и интерфейсами, компонентами платформы управления и т.д.

Системы межкомпонентного соединения, такие как описаны выше, поддерживают связь между IP блоками с использованием соответствующей проводки и протоколов. Обычно структура данной системы межкомпонентного соединения может содержать матричную "сетку", свободно наполненную систему коммутации, содержащую множество соединений типа точка-точка, общую шинную архитектуру или кольцевую топологию. В одном варианте осуществления, SoC архитектура обобщается таким образом, что каждая система коммутации может быть сконфигурирована в любой из этих топологий. Кроме того, конкретная структура межкомпонентного соединения и протоколы также обобщены в SoC архитектуре так, что различные системы коммутации могут использовать одни и те же или различные структуры межкомпонентного соединения и протоколы. Например, может быть желательно использовать межкомпонентное соединение, которое поддерживает протокол поддержки когерентности кэшей (например, QPI), для связи между ядрами процессора и кэш-памятью IP блоков, в то время как другие структуры и протоколы, такие как ОСР, могут быть использованы для других систем коммутации в архитектуре. Возможно, один протокол может быть использован для всей архитектуры или структуры системы коммутации могут представлять собой часть SoC.

Протокол открытого ядра определяет интерфейс точка-точка между двумя взаимодействующими объектами, такими как IP ядра и модули шинных интерфейсов (оболочки интерфейса шины), также называемые здесь как агенты. Один объект выступает как ОСР ведущий, например, и другие, как ведомые. Только ведущий может представить команды и управлять объектом. Ведомый отвечает на поступившие команды, либо принимая данные от ведущего, либо представляя данные ведущему. Для двух объектов, которые устанавливают одноранговую связь, необходимо иметь два экземпляра ОСР, соединяющий их, где первый объект является ведущим и тот, где первый объект является ведомым.

Характеристики IP ядра определяют, нуждается ли ядро в ведомом, ведущем или в обеих сторонах ОСР; модули оболочки интерфейса должны работать как дополнительная сторона ОСР для каждого подключенного объекта. Передача по этой системе происходит следующим образом. Системный инициатор (как ОСР ведущий) осуществляет передачу команды управления и, возможно, данных в адрес подключенного ведомого (модуль оболочки шинного интерфейса). Модуль интерфейса передает запрос через систему шин на кристалле. ОСР не указывает на функциональность встроенной шины. Вместо этого структура интерфейса преобразует ОСР запрос во встроенную шину обмена. Принимающий модуль оболочки шинного интерфейса (в качестве ОСР ведущего) преобразует операцию встроенной шины в нормативную ОСР команду. Целевая система (ОСР ведомого) принимает команду и осуществляет требуемое действие.

Каждый экземпляр ОСР выполнен (выбором сигналов или битовой шириной конкретного сигнала) на основе требований подключенного объекта, и не зависит от других. Например, системные инициаторы могут потребовать дополнительные адресные биты в их ОСР экземплярах для определения системных целей; дополнительные адресные биты могут быть использованы встроенной шиной для выбора целевой шины, к которой обращается системный инициатор.

ОСР является гибким. Есть несколько полезных моделей для обеспечения коммуникации IP ядер друг с другом. Некоторые используют конвейер для улучшения пропускной способности и характеристик латентности. Другие используют модели многотактового доступа, где сигналы удерживаются статически в течение нескольких тактов, чтобы упростить временной анализ и уменьшить область применения. Поддержка этого шаблона поведения может оказываться путем использования синхронных сигналов квитирования, которые позволяют как ведущему, так и ведомому осуществлять управления, когда сигналы могут быть изменены.

Согласно одному варианту осуществления устройство включает в себя блок хранения данных транзакций для хранения данных транзакций, подлежащих передаче по межкомпонентному соединению системы обработки данных; буфер транзакций, соединенный с блоком хранения данных транзакций для буферизации, по меньшей мере, части данных транзакций и логическое устройство транзакции, соединенное с блоком хранения данных транзакций и буфером транзакций для передачи сигнала с запросом (REQ) в адрес арбитра, ассоциированного с межкомпонентным соединением, в ответ на первые данные транзакции, которые становятся доступными в блоке хранения данных транзакций, в ответ на принятый сигнал разрешения (GNT) от арбитра, извлечение вторых данных транзакции из буфера транзакций и передачу вторых данных транзакции в межкомпонентное соединение и пополнение буфера транзакций с третьими данными транзакций, извлеченными из блока хранения данных транзакций, после того, как вторые данные транзакций были переданы на межкомпонентное соединение. Буфер транзакций буферизует заранее определенное фиксированное количество данных транзакций. Логическое устройство транзакций определяет факт заполнения буфера транзакции в ответ на первые данные транзакций и буферизует первые данные транзакций в буфере транзакций, если буфер транзакций не заполнен. Логическое устройство транзакций увеличивает значение счетчика в ответ на определение, что буфер транзакций заполнен, после того, как REQ был передан. Счетчик показывает количество REQs, которые приостановлены и их ассоциированные данные транзакций не были буферизованы в буфере транзакций. Третьи данные транзакции буферизуются в буфер транзакций, только если значение счетчика превышает нулевое значение. Логическое устройство транзакций уменьшает значение счетчика после того, как вторые данные транзакции была переданы на межкомпонентное соединение.

Набор команд или архитектура системы команд (ISA) является частью компьютерной архитектуры, относящейся к программированию, и может включать в себя собственные данные, команды, регистровую архитектуру, способы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод и вывод (I/O). Термин команда, как правило, относится здесь к макрокоманде - это команды, которые поставляются в процессор (или преобразователь команды, который преобразовывает (например, с помощью статического двоичного преобразования, динамического бинарного преобразования, включающее в себя динамическую компиляцию), трансформирует, эмулирует или иным образом преобразовывает команду из одной или более других команд, которые будут обрабатываться процессором) для выполнения - в отличие от микрокоманд или микроопераций (микрокоманды) - что является результатом декодирования макрокоманд декодером процессора.

ISA отличается от микроархитектуры, которая является внутренней структурой процессора, реализующей набор команд. Процессоры с различными микроархитектурами могут совместно использовать общий набор команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core ™ и процессоры Advanced Micro Devices, Inc. Sunnyvale CA реализовывают почти идентичные версии х86 набора команд (с некоторыми расширениями, которые были добавлены в более новых версиях), но имеют различные внутренние структуры. Например, та же архитектура регистра ISA может быть реализована по-разному в разных микроархитектурах с использованием хорошо известных способов, включающие в себя выделенные физические регистры, один или несколько динамически выделенных физических регистров, используя механизм переименования регистров (например, использование Таблицы псевдонимов регистров (RAT), Буфера переупорядочивания (ROB) и глобального внутрисхемного регистра процессор