Использование аутентифицированных манифестов для обеспечения внешней сертификации многопроцессорных платформ

Иллюстрации

Показать всеИзобретение относится к многопроцессорным платформам. Технический результат - защита данных. Процессорная система содержит архитектурно защищенную память и несколько процессорных устройств, осуществляющих связь с этой архитектурно защищенной памятью, причем первое процессорное устройство процессорной системы предназначено для реализации архитектурно защищенной исполнительной среды путем выполнения по меньшей мере одного из следующих действий: выполнения команд, резидентных в архитектурно защищенной памяти, или предотвращения неавторизованного доступа к архитектурно защищенной памяти; установления защищенного канала связи со вторым процессорным устройством из состава этой процессорной системы, использования этого защищенного канала связи для синхронизации идентификационного ключа платформы, представляющей процессорную систему, передачи манифеста платформы, содержащего идентификационный ключ платформы, в систему сертификации, и передачи в систему сертификации требования добавить третье процессорное устройство в процессорную систему. 3 н. и 21 з.п. ф-лы, 11 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к компьютерным системам и в частности относится к системам и способам, обеспечивающим внешнюю сертификацию многопроцессорных платформ.

Уровень техники

Важность защищенного и безопасного исполнения и целостности приложений и данных в компьютерной системе продолжает расти. Разнообразные известные способы обеспечения безопасности не способны адекватно защитить приложения и данные гибким, но надежным способом.

Краткое описание чертежей

Настоящее изобретение иллюстрируется на примерах, и, не в качестве ограничений, может быть лучше понято со ссылками на последующее подробное описание, рассматриваемое вместе с чертежами, на которых:

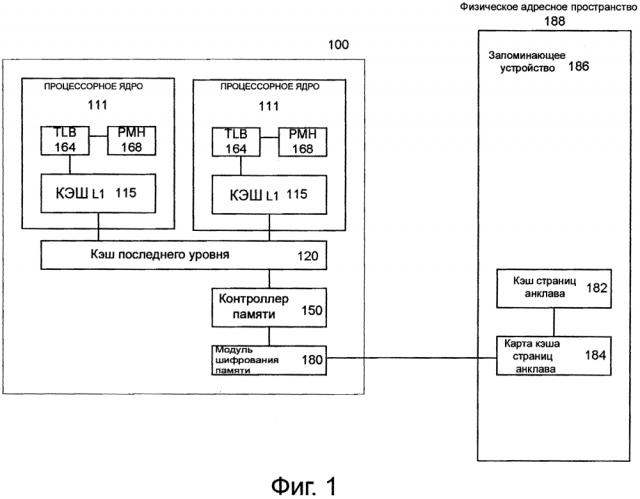

Фиг. 1 представляет компонентную схему высокого уровня для примера процессорной системы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 2 схематично иллюстрирует пример способа генерации манифеста платформы посредством многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 3 представляет логическую схему примера способа генерации манифеста платформы посредством многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 4 представляет логическую схему способа взаимной (перекрестной) аутентификации процессоров в составе многопроцессорной платформы после второй и последующих загрузок платформы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 5 представляет компонентную схему высокого уровня для примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 6 представляет блок-схему процессора согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 7а-7b схематично иллюстрируют элементы микроархитектуры процессора согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 8 представляет блок-схему примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 9 представляет блок-схему примера системы на кристалле (SoC) согласно одному или нескольким аспектам настоящего изобретения;

Фиг. 10 представляет блок-схему примера компьютерной системы согласно одному или нескольким аспектам настоящего изобретения; и

Фиг. 11 представляет блок-схему примера системы на кристалле (SoC) согласно одному или нескольким аспектам настоящего изобретения.

Подробное описание

Здесь описаны процессорные системы и соответствующие способы, обеспечивающие внешнюю сертификацию многопроцессорных платформ. Приложения, выполняемые процессорной системой, и данные, к которым обращаются и получают доступ эти приложения, могут быть защищены на микроархитектурном уровне, например, путем реализации защищенных анклавов, как это более подробно рассмотрено ниже.

Согласно одному или нескольким аспектам настоящего изобретения процессорная система может содержать процессорное ядро, связанное с архитектурно защищенной памятью. Это процессорное ядро может содержать управляющую логику, конфигурированную для предотвращения неавторизованного доступа к архитектурно защищенной памяти. Процессорное ядро может также содержать исполнительную логику, конфигурированную для реализации защищенного анклава путем выполнения команд для обращения и доступа к данным, находящимся в микроархитектурно защищенной памяти, как это будет более подробно описано ниже.

Каждый процессор в ходе его изготовления может быть оснащен идентификационным ключом. Идентификационный ключ процессора может храниться в энергонезависимом постоянном запоминающем устройстве в составе процессора, таком как группа программируемых перемычек. В случае однопроцессорной платформы идентификационный ключ процессора может быть использован в качестве идентификационного ключа платформы для передачи сервису сертификации и может быть также использован в качестве «ключевого» материала для генерации одного или нескольких шифровальных ключей для применения при создании защищенного анклава.

Следовательно, в случае многопроцессорных платформ анклав будет принимать различные ключи в зависимости от того, какой процессор работает с этим анклавом, что может привести к неисправимой ошибке, если активный анклав будет мигрировать от одного процессора к другому. Кроме того, для многопроцессорной платформы потребуется идентификатор платформы для представления сервису сертификации.

Один или несколько аспектов настоящего изобретения направлены на устранение перечисленных выше и других недостатков путем создания многопроцессорной платформы и способа генерации манифеста платформы, содержащего идентификационные ключи процессоров, входящих в состав платформы, и идентификационный ключ платформы, генерируемый и синхронизируемый этими процессорами, как будет более подробно рассмотрено ниже. Разнообразные аспекты упомянутых выше способов и систем будут более подробно рассмотрены ниже на примерах, а не посредством ограничений.

В последующем описании приведены многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные структуры аппаратуры, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы команд, конкретные компоненты систем, конкретные размеры/высоты, конкретные ступени процессорных конвейеров и операций с целью предоставления полного понимания настоящего изобретения. Специалисты в рассматриваемой области должны, однако, понимать, что не обязательно использовать все эти конкретные подробности для практической реализации рассматриваемых здесь способов. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные архитектуры процессоров, конкретные логические схемы/программные коды для рассматриваемых алгоритмов, конкретные встроенные программные коды, конкретные логические конфигурации, конкретные производственные технологии и материалы, конкретные реализации компиляторов, конкретные выражения алгоритмов в виде программных кодов, конкретные способы/логические схемы снижения питания и стробирования, и другие конкретные подробности работы компьютерных систем, здесь не были рассмотрены подробно, чтобы избежать ненужного загромождения и затемнения настоящего описания.

Хотя последующие примеры описаны со ссылками на процессор, другие варианты реализации применимы к другим типам интегральных схем и логических устройств. Аналогично, технологии и рекомендации, рассмотренные здесь, могут быть применены к другим типам схем или полупроводниковых приборов, которые могут выиграть от более высокой производительности и пропускной способности конвейерных систем и улучшения характеристик. Рекомендации и особенности примеров, рассмотренных здесь, применимы к любому процессору или машине, осуществляющей манипуляции с данными. Однако настоящее изобретение не ограничивается процессорами или машинами, выполняющими операции с данными размером 512 бит, 256 бит, 128 бит, 64 бит, 32 бит или 16 бит, а может быть применено к процессору или машине, манипулирующей данными или управляющей ими.

Примеры, иллюстрирующие настоящее изобретение, и прилагаемые чертежи не следует толковать в ограничительном смысле, поскольку они предназначены быть только примерами вариантов, рассмотренных здесь, а не для создания исчерпывающего списка всех возможных реализаций описываемых здесь вариантов. Хотя приведенные ниже примеры описывают манипуляции с командами и распределение таких команд в контексте функциональных исполнительных модулей и логических схем, другие варианты реализации систем и способов, представленных здесь, могут быть созданы с использованием записанных на машиночитаемом материальном носителе данных или команд, при выполнении которых машиной эта машина осуществляет функции, согласованные по меньшей мере с одним из описанных здесь вариантов. В некоторых вариантах реализации функции, ассоциированные с вариантами реализации, рассматриваемыми здесь, воплощены в исполняемых машиной командах. Эти команды могут быть использованы для того, что процессор общего назначения или специализированный процессор, запрограммированный этими командами, осуществлял описываемые здесь способы. Рассматриваемые здесь варианты реализации могут содержать машиночитаемый или компьютерный носитель записи с сохраненными на нем командами, который может быть использован для программирования компьютера (или другого электронного устройства) с целью выполнения одной или нескольких операций согласно рассматриваемым здесь вариантам. В качестве альтернативы, операции системы и способы, рассматриваемые здесь, могут быть выполнены специализированными аппаратными компонентами, содержащими логические схемы с фиксированными функциями для выполнения таких операций, или посредством сочетания программируемых компьютерных компонентов и аппаратных компонентов с фиксированными функциями.

Команды, используемые для программирования логических устройств с целью осуществления рассматриваемых здесь способов, могут быть записаны в запоминающем устройстве системы, таком как динамическое запоминающее устройство с произвольной выборкой (DRAM), кэш-память, флэш-память или другое запоминающее устройство. Более того, команды могут быть переданы через сеть связи или посредством другого компьютерного носителя записи. Таким образом, машиночитаемый носитель записи может содержать любой механизм для хранения или передачи информации в форме, читаемой машиной (например, компьютером), но не ограничиваясь этим, - дискеты, оптические диски, компакт-диски, постоянные запоминающие устройства (CD-ROM) и магнитооптические диски, постоянные запоминающие устройства (ПЗУ (ROM)), запоминающие устройства с произвольной выборкой (ЗУПВ (RAM)), стираемые программируемые постоянные запоминающие устройства (СППЗУ (EPROM)), электрически стираемые программируемые постоянные запоминающие устройства (ЭСППЗУ (EEPROM)), магнитные или оптические карточки, флэш-память или материальные машиночитаемые носители, используемые при передаче информации через Интернет посредством электрических, оптических, акустических или распространяющихся сигналов другого вида (например, волн несущих, инфракрасных сигналов, цифровых сигналов и т.п.). Соответственно, компьютерный носитель записи содержит материальный машиночитаемый носитель любого типа, подходящий для хранения или передачи команд или информации в электронном виде, в форме, читаемой машиной (например, компьютером).

Термин «процессор» здесь будет обозначать устройство, способное выполнять команды, кодирующие арифметические операции, логические операции или операции ввода/вывода. В одном иллюстративном примере процессор может соответствовать модели фон-Неймана и может содержать арифметическо-логическое устройство (ALU), модуль управления и несколько регистров. В следующем аспекте процессор может содержать одно или несколько процессорных ядер и, соответственно, может быть одноядерным процессором, который обычно способен выполнять команды одного конвейерного потока, или многоядерным процессором, который может одновременно обрабатывать команды нескольких конвейерных потоков. В другом аспекте процессор может быть реализован в виде одной интегральной схемы, двух или более интегральных схем или может быть компонентом многокристального модуля (например, где кристаллы индивидуальных микропроцессоров смонтированы в одном общем корпусе интегральной схемы и вследствие этого используют одно гнездо (сокет)).

На Фиг. 1 представлена блок-схема примера процессорной системы согласно одному или нескольким аспектам настоящего изобретения. Как показано на Фиг. 1, процессорная система 100 может содержать одно или несколько процессорных ядер 111, с каждым процессорным ядром 111 ассоциирован локальный кэш 115 первого уровня (L1). Кэш L1 115 может быть связан с совместно используемым кэшем 120 последнего уровня (LLC). В иллюстративном примере иерархия кэшей, содержащая кэш L1 115 и кэш LLC 120 может быть конфигурирована в виде инклюзивной иерархии кэшей, так что по меньшей мере часть информации, хранящейся в кэше L1 115, может быть также сохранена в кэше LLC 120.

Процессорные ядра 111 в разнообразных реализациях могут представлять Собой ядра, выполняющие команды по порядку, или ядра, выполняющие команды не по порядку (с внеочередным выполнением команд). В иллюстративном примере процессорное ядро 111 может иметь микроархитектуру, содержащую процессорные логические схемы и схемы, используемые для реализации архитектуры набора команд (instruction set architecture (ISA)). Процессоры с различными микроархитектурами могут использовать по меньшей мере часть общего набора команд. Например, одна и также архитектура регистров для ISA может быть реализована различными способами в разных микроархитектурах с использованием различных технологий и в том числе - выделенных физических регистров, одного или нескольких динамически выделяемых регистров с применением механизма переименования регистров (например, с использованием таблицы псевдонимов регистров (register alias table (RAT)), буфера переупорядочения (reorder buffer (ROB)) и регистрового файла завершения (retirement register file)), как показано на Фиг. 6-7. В некоторых вариантах реализации процессорная система 100 может также содержать разнообразные другие компоненты, не показанные на Фиг. 1.

Согласно одному или нескольким аспектам настоящего изобретения процессорная система 100 может содержать архитектурно защищенную память. Процессорное ядро 111 может содержать процессорную логику, конфигурированную для реализации защищенного анклава путем выполнения команд, находящихся в защищенной памяти, и доступа к данным, находящимся в защищенной памяти, предотвращая при этом неавторизованный доступ к защищенной памяти даже для привилегированных приложений, как будет более подробно описано ниже.

Термин «защищенный (или безопасный) анклав» здесь будет обозначать защищенную область в пределах адресного пространства приложения. Доступ к анклаву памяти от приложений, не являющихся резидентными в этом анклаве, предотвращен, даже если попытку такого доступа предпринимает привилегированное приложение, такое как BIOS, операционная система или монитор виртуальной машины.

Активный защищенный анклав может быть разбит на зашифрованную часть и незашифрованную часть. Зашифрованная часть анклава может находиться в незащищенной памяти (такой как главное запоминающее устройство или диск). Незашифрованная часть находится в кэше страниц анклава (enclave page cache (ЕРС)) 182. Кэш ЕРС представляет собой защищенную память, используемую процессорной системой для временного хранения страниц анклава, когда они не являются защищенными криптографически. Кэш ЕРС может быть разбит на страницы заданного размера, которые могут именоваться страницами ЕРС. Кэш ЕРС защищен от любого доступа посредством программного обеспечения, резидентного за пределами анклава. Более того, неавторизованные стороны не смогут прочитать или как-то модифицировать принадлежащие анклавам данные открытого текста, загруженные в кэш ЕРС, посредством прямолинейных аппаратных атак. Кэш ЕРС расположен в физическом адресном пространстве процессорной системы, но доступен он может быть только с использованием привилегированных или непривилегированных команд анклава, служащих для построения и активизации анклава, входа/выхода из анклава, управления кэшем ЕРС и выполнения разнообразных других операций.

Есть несколько механизмов реализации кэша ЕРС. Кэш ЕРС может быть реализован в виде выполненного на кристалле статического ЗУПВ (SRAM) или динамического ЗУПВ (DRAM). В качестве альтернативы кэш ЕРС может быть построен путем секвестирования кэша последнего уровня в составе центрального процессора CPU. Другим механизмом реализации кэша ЕРС является модуль шифрования памяти (Memory Encryption Engine (МЕЕ)). Термин «модуль МЕЕ» здесь будет обозначать реализованную аппаратно процессорную логическую схему, шифрующую трафик между корпусом процессора и динамическим ЗУПВ (DRAM) платформы, создавая, таким образом, механизм образования криптографически защищенной энергозависимой памяти с использованием динамического ЗУПВ DRAM платформы. Модуль МЕЕ может перехватывать попытки доступа к памяти и направлять их криптографическому контроллеру, который может генерировать один или несколько случаев обращения к динамическому ЗУПВ DRAM платформы с целью выборки зашифрованного текста, обрабатывать этот зашифрованный текст для генерации открытого текста и удовлетворять исходный запрос доступа к памяти.

Как показано на Фиг. 1, кэш L1 115 может передавать данные в кэш LLC 120 и из него. С кэшем 120 последнего уровня и модулем МЕЕ 180 может быть соединен контроллер 150 памяти. Этот контроллер 150 памяти может обращаться и получать доступ к кэшу ЕРС 182, резидентному в запоминающем устройстве 186 для резервного копирования в физическом адресном пространстве 188.

Карта кэша страниц анклава (Enclave Page Cache Map (EPCM)) представляет собой защищенную структуру, используемую процессорной системой для отслеживания контента кэша ЕРС. Карта ЕРСМ может содержать несколько входных позиций, каждая из которых соответствует своей странице кэша ЕРС. Каждая входная позиция карты ЕРСМ может содержать, в зависящем от конкретной реализации формате, следующую информацию: действительна ли соответствующая страница кэша ЕРС или нет; идентификатор события анклава, которому принадлежит эта страница, тип страницы (REG, TCS, VA, SECS); виртуальный адрес, по которому анклаву разрешено обращаться к этой странице; разрешения для чтения/записи/исполнения применительно к этой странице; доступна ли эта страница или нет («Заблокирована» (BLOCKED) или «Не заблокирована) UNBLOCKED).

Карта ЕРСМ может быть использована процессорной системой в процессе трансляции адресов, чтобы усилить управление доступом к страницам анклава, загруженным в кэш ЕРС. Логически это создает дополнительный уровень защиты при управлении доступом в качестве дополнения к «старым» известным механизмам сегментации, таблиц страниц и расширенных таблиц страниц.

Кэш ЕРС, карта ЕРСМ и разнообразные другие специфичные для конкретной реализации структуры данных могут быть отображены в позиции внутри архитектурно защищенной памяти. Когда происходит генерация запроса на доступ в кэш ЕРС, процессорная система 100 может переотобразить этот запрос в позицию в запоминающем устройстве для резервного копирования, содержащую зашифрованные данные кэша ЕРС, и извлечь эти данные.

Разнообразные функции, относящиеся к анклаву, могут быть реализованы в микрокоде (микропрограммном коде), поддерживаемом аппаратными реализациями модуля МЕЕ и процессорной логикой, осуществляющей функциональные характеристики анклава. В некоторых вариантах процессорная логика может управлять доступом в кэш ЕРС 182 через буфер 164 динамической трансляции (translation lookaside buffer (TLB)) и модуль 168 обработки промахов страниц (page miss handler (РМН)).

В иллюстративном примере буфер TLB может быть реализован в виде таблицы, отображающей виртуальные адреса на физические адреса. Термин «попадание в буфер TLB» ("TLB hit") обозначает ситуацию, когда запрошенный виртуальный адрес присутствует в буфере TLB. Термин «промах буфера TLB» ("TLB miss") обозначает противоположную ситуацию: когда запрошенный виртуальный адрес отсутствует в буфере TLB, преобразование (трансляция) адресов может происходить путем просмотра таблицы страниц. После определения физического адреса преобразование виртуального адреса в физический адрес может быть введено в буфер TLB.

Каждая входная позиция буфера TLB может содержать один или несколько битов, идентифицирующих анклав, владеющий позицией в памяти, на которую «ссылается» эта входная позиция буфера TLB. В качестве альтернативы, если этих битов нет, может потребоваться сброс буфера TLB при выходе из защищенного анклава, чтобы предотвратить неавторизованный доступ к кэшу ЕРС. В иллюстративном примере, если произошел промах буфера TLB, дополнительный просмотр сможет выбрать из карты ЕРС данные относительно нескольких ссылок в память. Модуль РМН может осуществлять просмотр карты ЕРС.

Процессорная система 100 может реализовать механизм, именуемый «аттестация» ("attestation"), посредством которого эта процессорная система может продемонстрировать внешнему объекту (например, удаленной компьютерной системе), что некий модуль программного обеспечения был правильно инсталлирован и запущен в процессорной системе. В некоторых вариантах реализации процессорная система 100 может генерировать идентификационный ключ, обеспечивающий идентификацию аппаратной платформы. В иллюстративном примере приложение, исполняемое в анклаве, может направлять этот идентификационный ключ сервису сертификации. После проверки действительности идентификационного ключа сервис сертификации может выдать аттестационный ключ и может далее передать этот аттестационный ключ обеспечивающему сервису. Приложение защищенного анклава, исполняемой процессорной системой, может затем передать свой идентификационный ключ этому обеспечивающему сервису для извлечения данных, чувствительных с точки зрения безопасности.

Каждый процессор может быть оснащен идентификационным ключом во время изготовления этого процессора. Идентификационный ключ процессора может храниться в энергонезависимом постоянном запоминающем устройстве в составе процессора, таком как группа программируемых перемычек. В случае однопроцессорной платформы идентификационный ключ процессора может быть использован в качестве идентификационного ключа платформы для передачи сервису сертификации и может быть также использован в качестве «ключевого» материала для генерации одного или нескольких шифровальных ключей для применения при создании защищенного анклава. В некоторых вариантах каждый защищенный анклав может затребовать один или несколько ключей с использованием команды EGETKEY.

Следовательно, в случае многопроцессорных платформ анклав будет принимать различные ключи в зависимости от того, какой процессор работает с этим анклавом, что может привести к неисправимой ошибке, если активный анклав будет мигрировать от одного процессора к другому. Кроме того, для многопроцессорной платформы потребуется идентификатор платформы для представления сервису сертификации.

Согласно одному или нескольким аспектам настоящего изобретения многопроцессорная платформа может генерировать манифест платформы, содержащий идентификационные ключи процессоров, входящих в состав платформы, и идентификационный ключ платформы, сформированный и синхронизированный процессорами, как это будет более подробно описано ниже.

Пример способа генерации манифеста платформы рассмотрен со ссылками на Фиг. 2. Логическая схема этого примера способа представлена на Фиг. 3. Как схематично показано на Фиг. 2, платформа 200 может содержать несколько процессорных корпусов 210. Тогда как приведенное ниже описание рассматривает случай двух процессорных корпусов, предлагаемые здесь способы в равной степени применимы к процессорным платформам, содержащим произвольное число процессоров.

После первой загрузки или сброса платформы каждый из процессоров 210А-210В может удостовериться, записан ли манифест платформы в заданной позиции энергонезависимой памяти, доступной соответствующему процессору. Если манифест платформы потерян или недействителен, процессоры 210 могут согласовать долговременные ключи 220 для межпроцессорной (IPC) связи с целью защиты последующей межпроцессорной связи для генерации манифеста 230 платформы. В иллюстративном примере процессоры 210 могут выполнять протокол согласования неаутентифицированного ключа (например, протокол обмена ключами Диффи-Хелмана (Diffie-Hellman)).

После этого процессоры могут установить защищенный канал связи с применением согласованного ключа 220 межпроцессорной связи и использовать этот канал связи для обмена своими идентификационными ключами и синхронизации набора функций безопасности. К последним могут относиться идентификационный ключ 225 платформы и идентификатор сертификационного сервиса, которым должна пользоваться эта платформа. В иллюстративном примере идентификатор сертификационного сервиса может представлять собой открытый ключ этого сертификационного сервиса.

В некоторых вариантах реализации идентификационный ключ 225 платформы может генерировать ведущий процессор этой платформы. Последний может быть выбран на основании того, что каждый процессор считывает заранее заданные настройки BIOS. Ведущий процессор может генерировать идентификационный ключ платформы (например, с использованием генератора случайных чисел). В одном иллюстративном примере идентификационный ключ платформы может быть представлен 128-битовым числом. В другом иллюстративном примере идентификационный ключ платформы может содержать один или несколько симметричных и/или асимметричных ключей. Ведущий процессор может дополнительно принимать идентификатор и открытый ключ сертификационного сервиса 240, например, посредством считывания заранее заданных настроек BIOS. Ведущий процессор может сообщить идентификационный ключ платформы и идентификатор сертификационного сервиса другим процессорам своей платформы с использованием безопасного канала связи, защищенного долговременными ключами связи, согласованными процессорами платформы, как это было описано выше.

После синхронизации функций безопасности с другими процессорами платформы каждый процессор может зашифровать с применением своего идентификационного ключа, ключевой двоичный объект (blob) 250, содержащий идентификационный ключ платформы и долговременные ключи для межпроцессорной связи. В некоторых вариантах реализации ключевой двоичный объект может дополнительно содержать идентификатор сертификационного сервиса. Процессор может сохранять такой ключевой двоичный объект в заданной позиции энергонезависимой памяти 255 (например, во флэш-памяти или на жестком диске), и может вызывать этот ключевой двоичный объект при последующих загрузках платформы.

После синхронизации функций безопасности с другими процессорами платформы каждый процессор этой платформы может дополнительно создать манифест 230 платформы, содержащий идентификационный ключ платформы и идентификационные ключи процессоров этой платформы. Каждый процессор может затем зашифровать манифест с применением открытого ключа сертификационного сервиса и передать зашифрованный манифест этому сертификационному сервису 240.

Сертификационный сервис 240 может проверить действительность платформы путем расшифровки и аутентификации принятых манифестов платформы и проверить действительность идентификационного ключа каждого процессора путем сравнения с авторитетным источником данных, где хранятся все действительные идентификационные ключи процессоров (например, у изготовителя или дистрибьютора процессоров). Сертификационный сервис может дополнительно убедиться, что манифесты были приняты от всех процессоров, входящих в состав рассматриваемой платформы, предотвращая тем самым попытки процессоров скрыть свое присутствие в составе платформы.

В ответ на успешную проверку действительности всех процессоров в составе платформы сертификационный сервис может записать идентификационный ключ платформы 225 в базе 260 данных для обеспечения ключей и выдать аттестационный ключ 270. Сертификационный сервис может дополнительно передать аттестационный ключ платформы обеспечивающему сервису 280. Приложение 290 защищенного анклава, исполняемое процессорной системой 200, может затем передать идентификационный ключ 225 своей платформы 225 обеспечивающему сервису, чтобы вызвать данные, чувствительные с точки зрения безопасности.

В некоторых вариантах реализации доступность канала связи для внешнего сертификационного сервиса может потребоваться только при первой загрузке платформы. При последующих загрузках каждый процессор может вызывать ключевой двоичный объект (blob), хранящийся в заданной позиции энергонезависимой памяти и расшифровывать идентификационный ключ платформы и долговременные ключи для межпроцессорной связи. После этого каждый процессор может установить защищенные каналы связи с другими процессорами своей платформы с использованием этих долговременных ключей для межпроцессорной связи с целью повторной аутентификации других процессоров платформы. После того, как каждый процессор платформы удостоверится, что все процессоры, присутствовавшие на платформе прежде последней загрузки, по-прежнему присутствуют на платформе и что на эту платформу не были добавлены новые процессоры, платформа может декларировать, что она соответствует конфигурации, которая ранее была сертифицирована посредством сертификационного сервиса.

Новый процессор может быть добавлен к ранее сертифицированной платформе путем передачи сертификационному сервису, который ранее сертифицировал эту платформу, запроса, содержащего идентификационный ключ вновь добавляемого процессора. В ответ на подтверждение действительности идентификационного ключа вновь добавляемого процессора сертификационный сервис может передать утверждающее сообщение. Вновь добавленный процессор может сохранить это утверждающее сообщение в заданной позиции энергонезависимой памяти. При новой загрузке платформы вновь добавленный процессор может вызвать это утверждающее сообщение из указанной позиции энергонезависимой памяти и представить вызванное утверждающее сообщение другим процессорам своей платформы, чтобы обменяться долговременными ключами для межпроцессорной связи, как более подробно описано выше. Этот вновь добавленный процессор может затем принять идентификационный ключ платформы от уже присутствующих процессоров по каналу связи, защищенному посредством долговременного ключа для межпроцессорной связи.

В некоторых вариантах реализации разрешение процессорам быть добавленными на платформу или удаленными с нее может создать ситуацию, когда два процессора, ранее входившие в состав одной и той же общей платформы, разделились с образованием своих собственных платформ, причем на обе новые платформы были добавлены вторые процессоры. Поскольку первые процессоры обладают ключевыми двоичными объектами (blob), содержащими идентификационный ключ их первоначальной платформы, последний может оказаться совместно используемым указанными двумя новыми платформами. Этот процесс может быть повторен, что потенциально ведет к произвольному числу платформ, совместно использующих один и тот же идентификационный ключ платформы.

Для предотвращения возможного возникновения описанного выше сценария в рамки платформы может быть введен чипсет. Этот чипсет может устанавливать уникальный идентификатор платформы. Каждый процессор может сохранить идентификатор платформы в своем ключевом двоичном объекте (blob). При повторной загрузке процессор может запросить идентификатор платформы из чипсета и сравнить полученную величину с идентификатором платформы, вызванным из ключевого двоичного объекта (blob). Если эти два идентификатора совпадут, значит, ключевой двоичный объект (blob) принадлежит текущей платформе. В противном случае процессор может инициировать процесс сертификации платформы, как это было описано выше.

На Фиг. 3 показана логическая схема примера способа генерации манифеста многопроцессорной платформы согласно одному или нескольким аспектам настоящего изобретения. Способ 300 может быть осуществлен компьютерной системой, которая может содержать аппаратную часть (например, разного рода схемы, специализированные логические устройства и/или программируемые логические устройства), программное обеспечение (например, команды, выполняемые компьютерной системой для моделирования функций аппаратуры) или сочетания аппаратуры и программного обеспечения. Способ 300 и/или каждая из его функций, процедур или операций может быть осуществлен одним или несколькими физическими процессорами из состава компьютерной системы, реализующей этот способ. Две или более функции, процедуры или операции способа могут быть выполнены параллельно или в порядке, отличном от описанного выше порядка. В некоторых вариантах реализации способ 300 может быть осуществлен посредством одного процессорного потока. В качестве альтернативы способ 300 может быть реализован посредством двух или более процессорных потоков, так что каждый поток выполняет одну или несколько индивидуальных функций, процедур или операций, составляющих способ. В иллюстративном примере процессорные потоки, реализующие способ 300 могут быть синхронизированы (например, с использованием семафоров, критических сечений и/или других механизмов синхронизации потоков). В качестве альтернативы, процессорные потоки, реализующие способ 300, могут работать асинхронно один относительно другого. В одном из примеров, показанном на Фиг. 3, способ 300 может быть осуществлен компьютерными системами, описываемыми ниже и иллюстрируемыми посредством чертежей Фиг. 5-11.

Как показано на Фиг. 3, в блоке 310 два или более процессоров могут согласовать ключи для межпроцессорной связи с целью установления защищенного канала связи. В иллюстративном примере процессоры могут выполнять протокол согласования анонимного (неаутентифицированного) ключа (например, протокол обмена ключами Диффи-Хелмана (Diffie-Hellman)), более подробно описанный выше.

В блоке 320 процессоры в составе платформы могут использовать защищенный канал связи для обмена своими идентификационными ключами и синхронизации группы функций безопасности. Последние могут содержать идентификационный ключ платформы и идентификатор сертификационного сервиса, который должна использовать эта платформа.

В блоке 330 платформа может назначить ведущий процессор. В иллюстративном примере этот ведущий процессор может быть идентифицирован настройками BIOS.

В блоке 340 ведущий процессор может генерировать идентификационный ключ платформы (например, с использованием генератора случайных чисел). В иллюстративном примере идентификационный ключ платформы может представлять собой 128-битовое число.

В блоке 350 ведущий процессор может принять идентификатор и открытый ключ внешнего сертификационного сервиса, например, посредством считывания заданных настроек BIOS.

В блоке 360 процессоры из состава платформы могут синхронизировать функции безопасности платформы, содержащие идентификационный ключ платформы и идентификатор сертификационного органа. Ведущий процессор может сообщить идентификационный ключ платформы и идентификатор сертификационного сервиса другим процессорам своей платформы с использованием безопасных каналов связи, защищенных посредством долговременных ключей для связи, согласованных, как описано выше со ссылками на блок 310.

В блоке 370 каждый процессор платформы может зашифровать, с использованием идентификационного ключа, ключевой двоичный объект (blob), содержащий идентификационный ключ платформы и долговременный ключ для межпроцессорной связи. Процессор может сохранить этот ключевой двоичный объект в заданной позиции в энергонезависимой памяти, как это было более подробно описано выше.

В блоке 380 каждый процессор из состава платформы может создать манифест платформы, содержащий идентификационный ключ платформы и идентификационные ключи процессоров из состава платформы.

В блоке 380 каждый процессор в составе платформы может «подписать» манифест платформы и зашифровать его открытым ключом сертификационного сервиса, после чего передать зашифрованный манифест сертификационному сервису для проверки действительности, как это более подробно описано выше.

На Фиг. 4 показана логическая схема примера способа перекрестной (взаимной) аутентификации процессоров в составе многопроцессорной платформы при второй и последующих загрузках платформы согласно одно