Логический преобразователь

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является уменьшение аппаратурных затрат и повышение быстродействия при сохранении функциональных возможностей прототипа - реализации симметричных булевых функций пяти переменных при соответствующих настройках. Устройство содержит пять информационных входов, три настроечных входа, выход, мажоритарный элемент, элемент ИЛИ, три элемента И. 1 ил., 1 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен логический преобразователь (патент РФ 2440601, кл. G06F 7/57, 2011 г.), который содержит 17 мажоритарных элементов, пять информационных входов, три настроечных входа, выход и реализует любую из пяти простых симметричных булевых функций при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся большие аппаратурные затраты и низкое быстродействие.

Известен логический преобразователь (патент РФ 2549158, кл. G06F 7/57, H03K 19/23, 2015 г.), который содержит 11 мажоритарных элементов, пять информационных входов, три настроечных входа, выход и реализует любую из пяти простых симметричных булевых функций при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся большие аппаратурные затраты и низкое быстродействие.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический преобразователь (патент РФ 2559708, МПК G06F 7/57, H03K 19/23, 2015 г.), предназначенный для реализации простых симметричных булевых функций, зависящих от пяти аргументов, содержащий пять информационных входов логического преобразователя, три настроечных входа логического преобразователя, выход логического преобразователя, одиннадцать мажоритарных элементов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического преобразователя, относятся большие аппаратурные затраты и низкое быстродействие.

Техническим результатом изобретения является уменьшение аппаратурных затрат и повышение быстродействия при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом преобразователе, содержащем пять информационных входов логического преобразователя, три настроечных входа логического преобразователя, выход логического преобразователя, мажоритарный элемент, причем выход мажоритарного элемента соединен с выходом логического преобразователя, особенность заключается в том, что он содержит три элемента И, элемент ИЛИ, мажоритарный элемент имеет девять входов, причем первый информационный вход логического преобразователя соединен с первым входом мажоритарного элемента, второй информационный вход логического преобразователя соединен со вторым входом мажоритарного элемента, третий информационный вход логического преобразователя соединен с третьим входом мажоритарного элемента, четвертый информационный вход логического преобразователя соединен с четвертым входом мажоритарного элемента, пятый информационный вход логического преобразователя соединен с пятым входом мажоритарного элемента, первый настроечный вход логического преобразователя соединен с шестым входом мажоритарного элемента, первым входом первого элемента И и с первым входом второго элемента И, второй настроечный вход логического преобразователя соединен со вторым входом первого элемента И, третий настроечный вход логического преобразователя соединен с вторым входом второго элемента И, выход первого элемента И соединен с седьмым входом мажоритарного элемента, с первым входом третьего элемента И и с первым входом элемента ИЛИ, выход второго элемента И соединен со вторым входом третьего элемента И и со вторым входом элемента ИЛИ, выход третьего элемента И соединен с восьмым входом мажоритарного элемента, выход элемента ИЛИ соединен с девятым входом мажоритарного элемента.

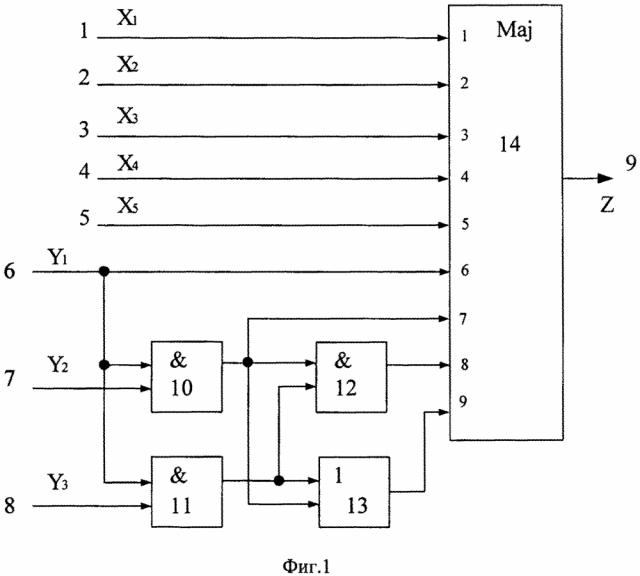

На чертеже представлена схема предлагаемого логического преобразователя.

Логический преобразователь содержит пять информационных входов логического преобразователя 1, 2, 3, 4, 5, три настроечных входа логического преобразователя 6, 7, 8, выход логического преобразователя 9, элементы И 10, 11, 12, элемент ИЛИ 13, мажоритарный элемент 14, причем первый информационный вход логического преобразователя 1 соединен с первым входом мажоритарного элемента 14, второй информационный вход логического преобразователя 2 соединен со вторым входом мажоритарного элемента 14, третий информационный вход логического преобразователя 3 соединен с третьим входом мажоритарного элемента 14, четвертый информационный вход логического преобразователя 4 соединен с четвертым входом мажоритарного элемента 14, пятый информационный вход логического преобразователя 5 соединен с пятым входом мажоритарного элемента 14, первый настроечный вход логического преобразователя 6 соединен с шестым входом мажоритарного элемента 14, первым входом первого элемента И 10 и с первым входом второго элемента И 11, второй настроечный вход логического преобразователя 7 соединен со вторым входом первого элемента И 10, третий настроечный вход логического преобразователя 8 соединен со вторым входом второго элемента И 11, выход первого элемента И 10 соединен с седьмым входом мажоритарного элемента 14, с первым входом третьего элемента И 12 и с первым входом элемента ИЛИ 13, выход второго элемента И 11 соединен со вторым входом третьего элемента И 12 и со вторым входом элемента ИЛИ 13, выход третьего элемента И 12 соединен с восьмым входом мажоритарного элемента 14, выход элемента ИЛИ 13 соединен с девятым входом мажоритарного элемента 14, выход мажоритарного элемента 14 соединен с выходом логического преобразователя 9.

Работа предлагаемого логического преобразователя осуществляется следующим образом. На его первый - пятый информационные входы 1, 2, 3, 4, 5 подаются соответственно двоичные сигналы X1, Х2, Х3, Х4, Х5∈{0,1}. На настроечные входы логического преобразователя 6,7,8 подаются в соответствии с заданной реализуемой симметричной логической функцией двоичные сигналы Y1, Y2, Y3∈{0,1}. В таблице приведены значения настроечных сигналов Y1, Y2, Y3, значения сигналов на входах 6, 7, 8, 9 мажоритарного элемента 14 (обозначенные соответственно М6, М7, M8, М9) и реализуемые при этом на выходе 9 логического преобразователя симметрические логические функции пяти переменных (Z).

Мажоритарный элемент 14 формирует на своем выходе сигнал «1», если пять и более сигналов на его входах равны «1». В зависимости от значений настроечных сигналов Y1, Y2, Y3 изменяются значения сигналов на входах 6, 7, 8, 9 мажоритарного элемента 14 и соответственно реализуемая симметричная логическая функция от пяти переменных.

Сравним характеристики прототипа и заявляемого устройства. В прототипе 11 мажоритарных элементов. В заявленном устройстве один мажоритарный элемент, три элемента И и один элемент ИЛИ. В прототипе задержка информационного сигнала происходит в пяти последовательно соединенных мажоритарных элементах, а в заявленном устройстве - только в одном мажоритарном элементе. Следовательно, заявленное устройство имеет меньшую аппаратную сложность и большее быстродействие при сохранении функциональных возможностей прототипа.

Логический преобразователь, предназначенный для реализации простых симметричных булевых функций, зависящих от пяти аргументов, содержащий пять информационных входов логического преобразователя, три настроечных входа логического преобразователя, выход логического преобразователя, мажоритарный элемент, причем выход мажоритарного элемента соединен с выходом логического преобразователя, отличающийся тем, что содержит три элемента И, элемент ИЛИ, мажоритарный элемент имеет девять входов, причем первый информационный вход логического преобразователя соединен с первым входом мажоритарного элемента, второй информационный вход логического преобразователя соединен со вторым входом мажоритарного элемента, третий информационный вход логического преобразователя соединен с третьим входом мажоритарного элемента, четвертый информационный вход логического преобразователя соединен с четвертым входом мажоритарного элемента, пятый информационный вход логического преобразователя соединен с пятым входом мажоритарного элемента, первый настроечный вход логического преобразователя соединен с шестым входом мажоритарного элемента, первым входом первого элемента И и с первым входом второго элемента И, второй настроечный вход логического преобразователя соединен со вторым входом первого элемента И, третий настроечный вход логического преобразователя соединен со вторым входом второго элемента И, выход первого элемента И соединен с седьмым входом мажоритарного элемента, с первым входом третьего элемента И и с первым входом элемента ИЛИ, выход второго элемента И соединен со вторым входом третьего элемента И и со вторым входом элемента ИЛИ, выход третьего элемента И соединен с восьмым входом мажоритарного элемента, выход элемента ИЛИ соединен с девятым входом мажоритарного элемента.