Синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиоэлектронике, в частности к синтезаторам частот на основе петли фазовой автоподстройки частоты (ФАПЧ). Технический результат заключается в снижении уровня фазовых шумов и побочных дискретных составляющих в спектре выходного сигнала, что в свою очередь повышает качество выходного сигнала, при сохранении высокого разрешения по частоте и широкой полосы перестройки. Синтезатор частот содержит соединенные последовательно умножитель частоты входного сигнала, делитель с фиксированным коэффициентом деления, первую микросхему прямого цифрового синтеза, фазочастотный детектор, первый фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи, включающий в себя соединенные последовательно смеситель, один из входов которого соединен с выходом генератора, управляемого напряжением, а второй вход соединен с выходом умножителя частоты входного сигнала, второй фильтр низких частот и вторую микросхему прямого цифрового синтеза, выход которой соединен с входом фазочастотного детектора, и управляющее устройство, выходы которого соединены с входами первой и второй микросхем прямого цифрового синтеза. Изобретение обеспечивает снижение уровня фазовых шумов и дискретных составляющих в спектре выходного сигнала, что, в свою очередь, повышает качество выходного сигнала, при сохранении высокого разрешения по частоте и широкой полосы перестройки. 1 ил.

Реферат

СИНТЕЗАТОР ЧАСТОТ

Изобретение относится к радиоэлектронике, в частности, к синтезаторам частот на основе петли фазовой автоподстройки частоты (ФАПЧ).

Известен синтезатор частот, содержащий соединенные последовательно преобразователь частоты входного сигнала, фазочастотный детектор, фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи, включающий в себя преобразователь частоты выходного сигнала, выход которого соединен с входом фазочастотного детектора, и управляющее устройство, выходы которого соединены с входами преобразователей частоты входного и выходного сигналов (см., например, статью Белова Л. «Синтезаторы стабильных частот», в ж. «Электроника: наука, технология, бизнес», 3/2004, стр. 38-44, рис. 2).

В известном синтезаторе в качестве преобразователей входного и выходного сигналов использованы делители с целочисленным коэффициентом деления.

Недостаток известного синтезатора состоит в низком разрешении по частоте, ограничивающем область его применения.

Кроме этого, использование делителей с целочисленным коэффициентом деления приводит к значительному увеличению фазовых шумов в спектре выходного сигнала синтезатора.

Также известен синтезатор частот, содержащий соединенные последовательно преобразователь частоты входного сигнала, в качестве которого использована микросхема прямого цифрового синтеза, делитель с целочисленным коэффициентом деления, фазочастотный детектор, фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи, включающий в себя преобразователь частоты выходного сигнала, в качестве которого использован делитель с целочисленным коэффициентом деления, выход которого соединен с входом фазочастотного детектора, и управляющее устройство, выходы которого соединены с входами преобразователей частоты входного и выходного сигналов (см. US 5801589, 01.09.1998).

Недостаток известного синтезатора частот также состоит в достаточно высоком уровне фазовых шумов в спектре выходного сигнала, обусловленным использованием делителя с целочисленным коэффициентом деления в петле ФАПЧ.

Кроме этого, использование микросхемы прямого цифрового синтеза в качестве преобразователя входного сигнала неизбежно приводит к появлению побочных дискретных составляющих в спектре выходного сигнала, при том, что схема известного синтезатора не позволяет реализовать их существенное подавление.

Известный синтезатор частот принят в качестве ближайшего аналога заявленного синтезатора частот.

Задачей настоящего изобретения является создание синтезатора частот, лишенного указанных недостатков.

В результате достигается технический результат, заключающийся в снижении уровня фазовых шумов и побочных дискретных составляющих в спектре выходного сигнала, что, в свою очередь, повышает качество выходного сигнала, при сохранении высокого разрешения по частоте и широкой полосы перестройки.

Конкретно, технический результат достигается путем создания синтезатора частот, содержащего соединенные последовательно умножитель частоты входного сигнала, делитель с фиксированным целочисленным коэффициентом деления, первую микросхему прямого цифрового синтеза (далее - МПЦС), фазочастотный детектор, первый фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи (далее - ООС), включающий в себя соединенные последовательно смеситель, один из входов которого соединен с выходом генератора, управляемого напряжением, а второй вход соединен с выходом умножителя частоты входного сигнала, второй фильтр низких частот и вторую МПЦС, выход которой соединен с входом фазочастотного детектора, и управляющее устройство, выходы которого соединены с входами первой и второй МПЦС.

Снижение уровня фазовых шумов обеспечивается уменьшением коэффициента деления частоты в петле ФАПЧ в результате замены делителя с целочисленным коэффициентом деления на смеситель, второй фильтр низких частот и вторую МПЦС, соединенные последовательно.

Снижение уровня побочных дискретных составляющих обеспечивается использованием в схеме заявленного синтезатора частот двух микросхем прямого цифрового синтеза, входы которых соединены с выходами управляющего устройства, что позволяет реализовывать вариативный алгоритм, подходящий для подавления побочных дискретных составляющих с различным, в том числе, постоянным шагом перестройки частоты в широком диапазоне частот, в частности, алгоритм, подобный описанному в US 5801589, 01.09.1998.

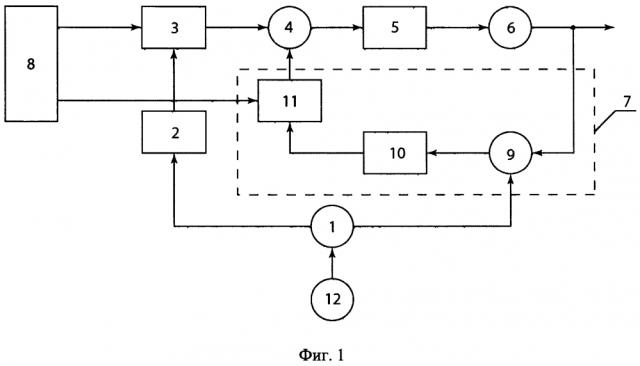

На фиг. 1 представлена схема заявленного синтезатора частот.

Синтезатор частот, показанный на фиг. 1, содержит соединенные последовательно умножитель частоты входного сигнала 1, делитель с фиксированным целочисленным коэффициентом деления 2, первую МПЦС 3, используемую в качестве преобразователя частоты входного сигнала, фазочастотный детектор 4, первый фильтр низких частот 5, генератор 6, управляемый напряжением, контур ООС 7 и управляющее устройство 8.

Контур ООС 7 включает в себя соединенные последовательно смеситель 9, один из входов которого соединен с выходом генератора 6, управляемого напряжением, а второй вход соединен с выходом умножителя частоты входного сигнала 1, второй фильтр низких частот 10 и вторую МПЦС 11, используемую в качестве преобразователя частоты выходного сигнала.

Выход второй МПЦС 11 соединен с входом фазочастотного детектора 4 с образованием петли ФАПЧ.

Выходы управляющего устройства 8 соединены с входами первой и второй МПЦС 3 и 11.

Заявленный синтезатор частот работает следующим образом.

Как показано на фиг. 1, с опорного генератора 12 (не входит в состав синтезатора частот) получают входной сигнал заданной частоты. Производят умножение частоты опорного генератора при помощи умножителя 1 и ее последующее деление на целочисленный коэффициент D (например, D=2) при помощи делителя 2.

В результате получают сигнал частотой Fсинхр и производят тактирование этим сигналом первой МПЦС 3 для получения на ее выходе опорного сигнала частотой Fdds1=α1Fсинхр, где α1 - коэффициент преобразования частоты в первой МПЦС 3.

Далее производят сравнение фазы и частоты опорного и синхронизируемого сигналов для выработки аналогового напряжения, пропорционального фазовому и/или частотному рассогласованию при помощи фазочастотного детектора 4, а затем осуществляют фильтрацию полученного напряжения по низкой частоте при помощи первого фильтра низких частот 5.

Далее это напряжение подают на генератор 6, управляемый напряжением, для получения на его выходе сигнала частотой Fвых, а затем ответвляют часть полученного сигнала в контур ООС 7.

В контуре ООС 7 синхронизируемый сигнал получают при помощи второй МПЦС 11, тактируя ее сигналом частотой Fвых-DFсинхр, для получения на ее выходе сигнала частотой:

Fdds2=α2(Fвых-DFсинхр), где α2 - коэффициент преобразования частоты во второй МПЦС 11.

Сигнал частотой Fвых-DFсинхр получают смешиванием сигналов с частотами Fвых и DFсинхр в смесителе 9 с дальнейшим выделением разностной составляющей в фильтре низких частот 10.

Последовательность выбора выходных частот Fdds1 и Fdds2 реализуют при помощи управляющего устройства 8, путем присваивания соответствующим выходным частотам Fвыхi значений α1 и α2 для первой и второй МПЦС 3 и 11, выбираемых в соответствии с алгоритмом частотной корректировки, обеспечивающим подавление дискретных составляющих в спектре выходного сигнала.

В частности, может быть использован алгоритм, подобный известному алгоритму, описанному в US 5801589.

Ниже приведена оценка уровня фазовых шумов синтезатора частот, принятого в качестве ближайшего аналога, и заявленного синтезатора частот.

Для оценки использовано математическое выражение, взятое из Venceslav F. Kroupa. Phase Locked Loops and Frequency Synthesizers, 2003, John Wiley and Sons, Ltd, стр. 222.

Для наглядности из оценки исключены собственные фазовые шумы первой МПЦС.

В результате:

SФ,вых(ω)=[SФ,вх(ω)+SФ,ООС(ω)]·N2·|H(jω)|2+SФ,гун(ω)|1-H(jω)|2, где

SФ,вых(ω) - спектральная плотность мощности фазовых флуктуаций (далее - СПМФФ) выходного сигнала;

SФ,вх(ω) - СПМФФ входного сигнала (сигнала опорного генератора);

SФ,ООС(ω) - СПМФФ компонентов контура ООС;

N - коэффициент деления делителя частоты в контуре ООС;

SФ,гун(ω) - СПМФФ генератора, управляемого напряжением;

H(jω) - передаточная характеристика замкнутой петли ФАПЧ.

Так как в полосе пропускания первого фильтра низких частот SФ,гун(ω) можно пренебречь, a H(jω) не зависит от выбора N в полосе пропускания первого фильтра низких частот, данное выражение можно переписать в следующем виде:

SФ,вых(ω)=[SФ,вх(ω)+SФ,ООС(ω)]·N2.

Таким образом, основной вклад в СПМФФ выходного сигнала синтезатора частот вносят фазовые шумы сигнала опорного генератора и компонентов контура ООС,

СПМФФ которых умножается на квадрат целочисленного коэффициента деления делителя частоты.

В заявленном синтезаторе частот коэффициент деления снижен путем замены делителя частоты на смеситель, второй фильтр низких частот и вторую МПЦС, соединенные последовательно.

Тогда СПМФФ выходного сигнала можно записать как:

, где

- СПМФФ контура ООС с учетом собственных шумов смесителя и фазовых шумов сигнала с выхода умножителя сигнала опорного генератора.

Приняв собственные шумы второй МПЦС приблизительно равными собственным шумам делителя частоты с целочисленным коэффициентом деления, запишем:

Учитывая, что частота на выходе генератора, управляемого напряжением, и умножителя частоты должны незначительно отличаться, СПМФФ на выходе умножителя для схемы заявленного синтезатора частот можно представить как:

SФ,УМ(ω)=SФ,вх(ω)K2≈SФ,вх(ω)N2.

В результате:

Так как в схеме заявленного синтезатора частот предполагается α2<<N, то влияние собственных шумов компонентов SФ,ООС(ω)+SФ,СМ(ω) ООС на уровень СПМФФ выходного сигнала значительно ослабевает.

Синтезатор частот, содержащий соединенные последовательно первую микросхему прямого цифрового синтеза, фазочастотный детектор, первый фильтр низких частот, генератор, управляемый напряжением, контур отрицательной обратной связи, включающий в себя преобразователь частоты выходного сигнала, выход которого соединен с входом фазочастотного детектора, и управляющее устройство, один из выходов которого соединен с первым входом первой микросхемы прямого цифрового синтеза, а второй выход соединен с первым входом преобразователя частоты выходного сигнала, отличающийся тем, что он снабжен умножителем частоты входного сигнала и соединенным с ним последовательно делителем с фиксированным целочисленным коэффициентом деления, выход которого соединен со вторым входом первой микросхемы прямого цифрового синтеза, а в контур отрицательной обратной связи дополнительно введены соединенные последовательно смеситель, один из входов которого соединен с выходом генератора, управляемого напряжением, а второй вход соединен с выходом умножителя частоты входного сигнала, и второй фильтр низких частот, выход которого соединен со вторым входом преобразователя частоты выходного сигнала, в качестве которого использована вторая микросхема прямого цифрового синтеза.