Твердотельный датчик изображения и система восприятия изображения

Иллюстрации

Показать всеИзобретение относится к твердотельному датчику изображения и системе восприятия изображения. Датчик содержит блок восприятия изображения, включающий в себя блоки пикселов, и блок считывания для считывания сигнала из блока восприятия изображения. Блок пикселов включает в себя фотоэлектрический преобразователь, первый и второй транзисторы и источник тока. Первые основные электроды первого и второго транзисторов соединены с общим узлом, а источник тока обеспечен между общим узлом и предварительно заданным напряжением. Операция считывания сигнала включает в себя операцию, в которой напряжение, соответствующее зарядам в фотоэлектрическом преобразователе, подается на управляющий электрод первого транзистора, а изменяющееся во времени опорное напряжение подается на управляющий электрод второго транзистора. Блок считывания считывает сигнал из блока восприятия изображения через второй основной электрод первого транзистора. Изобретение обеспечивает увеличение точности считывания сигнала пиксела. 2 н. и 19 з.п. ф-лы, 24 ил.

Реферат

УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к твердотельному датчику изображения и системе восприятия изображения.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Фиг. 2 выложенного патента Японии №2001-223566 изображает компаратор, включающий в себя пикселы 201, 202 и 203, блок 210 формирования пути тока, путь 211 тока и блок 215 сравнения. Блок 210 формирования пути тока включает в себя МОП-транзисторы 204, 205 и 206, имеющие затворы, с которыми соответствующим образом соединяются преобразователи заряда в напряжение пикселов 201, 202 и 203. Путь 211 тока включает в себя МОП-транзистор, имеющий затвор, на который подается опорное напряжение 212. Блок 215 сравнения включает в себя арифметический усилитель, включающий в себя блок 210 формирования пути тока и путь 211 тока, в качестве дифференциальной пары, и может получить цифровой сигнал, соответствующий сигналу пиксела, на основании выходного сигнала из блока 215 сравнения.

[0003] В данной компоновке, изображенной на Фиг. 2 выложенного патента Японии №2001-223566, транзистор 213, который, в сочетании с усилительными транзисторами 204, 205 и 206 пикселов 201, 202 и 203, формирует дифференциальную пару, обеспечивается за пределами пикселов 201, 202 и 203. В подобной компоновке трудно улучшить баланс между одним путем тока и другим путем тока, которые образуют дифференциальную пару, и это иногда препятствует увеличению точности считывания сигнала пиксела в достаточной мере.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] Настоящее изобретение обеспечивает метод, являющийся предпочтительным для увеличения точности считывания сигнала пиксела.

[0005] Один из аспектов настоящего изобретения обеспечивает твердотельный датчик изображения, содержащий блок восприятия изображения, включающий в себя множество блоков пикселов, и блок считывания, выполненный с возможностью считывания сигнала из блока восприятия изображения, в котором блок пикселов включает в себя фотоэлектрический преобразователь, первый транзистор, второй транзистор и источник тока, причем первый основной электрод первого транзистора и первый основной электрод второго транзистора соединяются с общим узлом, источник тока обеспечивается в пути между общим узлом и предварительно заданным напряжением, операция считывания для считывания сигнала из блока восприятия изображения включает в себя операцию, в которой напряжение, соответствующее зарядам, сгенерированным в фотоэлектрическом преобразователе, подается на управляющий электрод первого транзистора, изменяющееся во времени опорное напряжение подается на управляющий электрод второго транзистора, и блок считывания считывает сигнал из блока восприятия изображения через второй основной электрод первого транзистора.

[0006] Дополнительные отличительные признаки настоящего изобретения явствуют из нижеследующего описания иллюстративных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

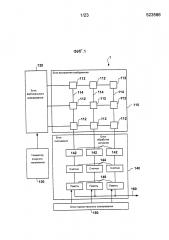

[0007] Фиг. 1 является видом, показывающим компоновку твердотельного датчика изображения в соответствии с одним вариантом осуществления настоящего изобретения;

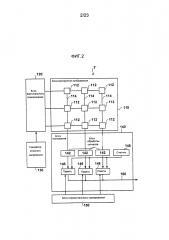

[0008] Фиг. 2 является видом, показывающим компоновку твердотельного датчика изображения в соответствии с другим вариантом осуществления настоящего изобретения;

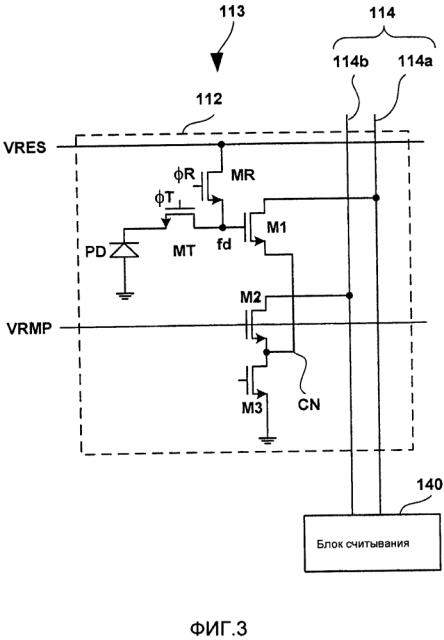

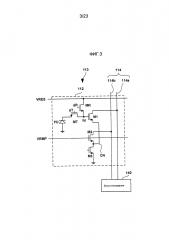

[0009] Фиг. 3 является видом для иллюстративного разъяснения принципа настоящего изобретения;

[0010] Фиг. 4 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии с первым вариантом осуществления настоящего изобретения;

[0011] Фиг. 5 является видом, показывающим работу твердотельного датчика изображения в соответствии с первым вариантом осуществления настоящего изобретения;

[0012] Фиг. 6 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии со вторым вариантом осуществления настоящего изобретения;

[0013] Фиг. 7 является видом, показывающим работу твердотельного датчика изображения в соответствии со вторым вариантом осуществления настоящего изобретения;

[0014] Фиг. 8А и 8 В является видами, показывающими примеры компоновок блока обработки сигналов, применимых к первому и второму вариантам осуществления;

[0015] Фиг. 9 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии с третьим вариантом осуществления настоящего изобретения;

[0016] Фиг. 10 является видом, показывающим пример компоновки блока обработки сигналов, применимой к третьему варианту осуществления;

[0017] Фиг. 11 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии с четвертым вариантом осуществления настоящего изобретения;

[0018] Фиг. 12 является видом, показывающим работу твердотельного датчика изображения в соответствии с четвертым вариантом осуществления настоящего изобретения;

[0019] Фиг. 13 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии с пятым вариантом осуществления настоящего изобретения;

[0020] Фиг. 14 является видом, показывающим работу твердотельного датчика изображения в соответствии с пятым вариантом осуществления настоящего изобретения;

[0021] Фиг. 15 является видом, показывающим компоновку блока восприятия изображения твердотельного датчика изображения в соответствии с шестым вариантом осуществления настоящего изобретения;

[0022] Фиг. 16 является видом, показывающим первый пример применения в качестве примера применения первого варианта осуществления, изображенного на Фиг. 4;

[0023] Фиг. 17 является видом, показывающим работу первого примера применения;

[0024] Фиг. 18 является видом, показывающим пример компоновки блока обработки сигналов в первом примере применения;

[0025] Фиг. 19 является видом, показывающим другую работу первого примера применения;

[0026] Фиг. 20 является видом для разъяснения еще одной работы первого примера применения;

[0027] Фиг. 21 является видом, показывающим второй пример применения в качестве примера применения четвертого варианта осуществления, изображенного на Фиг. 11;

[0028] Фиг. 22 является видом, показывающим работу второго примера применения;

[0029] Фиг. 23 является видом, показывающим третий пример применения в качестве другого примера применения четвертого варианта осуществления, изображенного на Фиг. 11; и

[0030] Фиг. 24 является видом, показывающим компоновку системы восприятия изображения в качестве варианта осуществления настоящего изобретения.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0031] Далее, со ссылкой на прилагаемые чертежи, будут разъясняться иллюстративные варианты осуществления настоящего изобретения.

[0032] Фиг. 1 изображает компоновку твердотельного датчика 1 изображения, в соответствии с одним вариантом осуществления настоящего изобретения. Твердотельный датчик 1 изображения включает в себя блок 110 восприятия изображения и блок 14 0 считывания для считывания сигнала из блока 110 восприятия изображения. Блок 110 восприятия изображения включает в себя множество пикселов 112, которые располагаются таким образом, чтобы они формировали множество строк и множество столбцов, при этом каждый пиксел 112 включает в себя фотоэлектрический преобразователь, такой как, например, фотодиод. С других точек зрения, блок 110 восприятия изображения включает в себя множество блоков пикселов, причем каждый блок пикселов включает в себя, по меньшей мере, один пиксел 112, при этом каждый пиксел включает в себя фотоэлектрический преобразователь.

[0033] Твердотельный датчик 1 изображения включает в себя блок 120 вертикального сканирования (блок выбора по вертикали) и блок 150 горизонтального сканирования (блок выбора по горизонтали) для выбора пиксела 112, от которого считывается сигнал. Блок 120 вертикального сканирования выбирает подлежащую считыванию строку из множества строк в блоке 110 восприятия изображения, при этом блок 14 0 считывания считывает сигналы пикселов 112 в выбранной строке через вертикальный путь 114 передачи. Блок 150 горизонтального сканирования выбирает пикселы 112 в подлежащем считыванию столбце из сигналов пикселов 112 во множестве столбцов, считываемых посредством блока 140 считывания, и выводит сигналы выбранных пикселов 112 на линию 160 передачи выходных сигналов. То есть, блок 150 горизонтального сканирования выбирает подлежащий считыванию столбец из множества столбцов в блоке 110 восприятия изображения.

[0034] Твердотельный датчик 1 изображения дополнительно включает в себя генератор 130 опорного напряжения. Генератор 130 опорного напряжения генерирует изменяющееся во времени опорное напряжение. Как правило, такое изменяющееся во времени опорное напряжение является линейно изменяющимся сигналом. Опорное напряжение, сгенерированное посредством генератора 130 опорного напряжения, может быть подано через блок 120 вертикального сканирования на блок 113 пикселов, включающий в себя пикселы 112 в подлежащей считыванию строке блока 110 восприятия изображения. Опорное напряжение также может быть подано на блок 113 пикселов без использования блока 120 вертикального сканирования. Как иллюстративно изображается на Фиг. 3, каждый блок 113 пикселов включает в себя, по меньшей мере, один фотоэлектрический преобразователь PD (например, фотодиод), первый транзистор M1, второй транзистор М2 и источник М3 тока. Первый основной электрод (в данном примере - электрод истока) первого транзистора M1 и первый основной электрод (в данном примере электрод истока) второго транзистора М2 соединяются с общим узлом CN, при этом третий транзистор М3 обеспечивается в пути между общим узлом CN и предварительно заданным потенциалом (в данном примере - потенциалом земли). Третий транзистор М3 функционирует в качестве источника тока, когда предварительно заданное напряжение смещения прикладывается к управляющему электроду (затвору). Первый транзистор M1, второй транзистор М2 и источник тока МЗ образуют схему дифференциального усилителя. Выходной сигнал из этой схемы дифференциального усилителя передается на блок 140 считывания через вертикальный путь 114 передачи. В изображенном на Фиг. 3 примере один вертикальный путь 114 передачи включает в себя первые и вторые вертикальные линии 114а и 114b передачи сигналов, которые образуют дифференциальную пару линий передачи сигналов. В другом примере один вертикальный путь 114 передачи включает в себя одну вертикальную линию 114а передачи сигналов.

[0035] Операция считывания для считывания сигнала из блока 110 восприятия изображения включает в себя операцию, в которой напряжение, соответствующее зарядам, сгенерированным в фотоэлектрическом преобразователе PD подлежащего считыванию пиксела 112, подается на управляющий электрод первого транзистора M1, при этом изменяющееся во времени опорное напряжение VRMP подается на управляющий электрод второго транзистора М2. Следует отметить, что управляющий электрод является электродом затвора. Блок 140 считывания считывает сигнал из блока 110 восприятия изображения через второй основной электрод (в данном примере - электрод стока) первого транзистора M1 и вертикальный путь 114 передачи. В изображенном на Фиг. 3 примере блок 140 считывания считывает сигнал из блока 110 восприятия изображения на основании сигнала, который передается по первой вертикальной линии 114а передачи сигналов, соединенной со вторым основным электродом первого транзистора M1, и сигнала, который передается по второй вертикальной линии 114b передачи сигналов, соединенной с основным электродом второго транзистора М2. Заряды, сгенерированные в фотоэлектрическом преобразователе PD, переносятся через транзистор МТ переноса в преобразователь fd заряда в напряжение (плавающую диффузную область), соединенный с управляющим электродом (затвором) первого транзистора M1, и преобразовываются в напряжение посредством преобразователя fd заряда в напряжение. Напряжение преобразователя fd заряда в напряжение сбрасывается посредством транзистора MR управления напряжением.

[0036] Сигнал φΤ переноса, находящийся под управлением блока 120 вертикального сканирования, прикладывается к затвору транзистора МТ переноса. Сигнал φR управления напряжением, находящийся под управлением блока 12 0 вертикального сканирования, прикладывается к затвору транзистора MR управления напряжением. В нижеследующем описании, для проведения различия между одним сигналом переноса и другим сигналом переноса, после φΤ добавляются номера, подобно φΤ1 и φΤ2. Подобным образом, для проведения различия между одним сигналом управления напряжением и другим сигналом управления напряжением, после φR добавляются номера, подобно φR1 и φR2. Это также относится и к другим сигналам.

[0037] Блок 140 считывания преобразовывает сигнал, который передается от пиксела 112 блока 110 восприятия изображения через вертикальный путь 114 передачи, в цифровой сигнал, а также выводит сигнал в линию 160 передачи выходных сигналов. В общеизвестном твердотельном датчике изображения, который выводит сигнал пиксела в качестве цифрового сигнала, усилитель столбца, сформированный для каждого столбца блока восприятия изображения, считывает сигнал из пиксела в форме аналогового сигнала напряжения, при этом аналого-цифровой (AD) преобразователь преобразовывает этот аналоговый сигнал напряжения в цифровой сигнал. Для сравнения, в твердотельном датчике 1 изображения данного варианта осуществления, сигнал, который передается от пиксела на вертикальный путь 114 передачи, имеет форму в токовом сигнале, и этот токовый сигнал преобразовывается в цифровой сигнал.

[0038] Блок 140 считывания может включать в себя блок 142 обработки сигналов, счетчик 144 и память 146. Набор из блока 142 обработки сигналов, счетчика 144 и памяти 14 6 может быть сформирован для каждого столбца блока 110 восприятия изображения. Блок 142 обработки сигналов принимает электрический ток, который подается от второго основного электрода первого транзистора M1, через вертикальный путь 114 передачи. На основании значения этого электрического тока, блок 142 обработки сигналов обнаруживает момент, при котором соотношение величин между напряжением управляющего электрода первого транзистора M1 (это напряжение также является напряжением преобразователя fd заряда в напряжение) и напряжением (опорным напряжением VRMP) управляющего электрода второго транзистора М2 инвертируется. Например, блок 142 обработки сигналов сравнивает значение первого электрического тока, который подается от второго основного электрода первого транзистора M1 через первую вертикальную линию 114а передачи сигналов, со значением второго электрического тока, который подается от второго основного электрода второго транзистора М2 через вторую вертикальную линию 114b передачи сигналов. Затем блок 142 обработки сигналов выводит сигнал результата сравнения, указывающий соотношение величин между значениями первого и второго электрических токов. Инверсия этого сигнала результата сравнения означает, что соотношение величин между значениями первого и второго электрических токов было инвертировано. Кроме того, инверсия соотношения величин между значениями первого и второго электрических токов является эквивалентной инверсии соотношения величин между напряжениями управляющих электродов первого и второго транзисторов M1 и М2.

[0039] Счетчик 144 начинает операцию отсчета при предварительно заданном тактировании, и прекращает операцию отсчета, в соответствии с инверсией сигнала результата сравнения. Память 146 сохраняет значение отсчета (то есть, значение пиксела), полученное посредством счетчика 144, и выводит значение отсчета на линию 160 передачи выходных сигналов при выборе посредством блока 150 горизонтального сканирования. То есть, блок 140 считывания принимает решение о том, что значение отсчета счетчика 144 является значением сигнала, считанного из блока 110 восприятия изображения, в соответствии с инверсией выходного сигнала из блока 142 обработки сигналов.

[0040] Фиг. 2 изображает компоновку твердотельного датчика 11 изображения другого варианта осуществления настоящего изобретения. Твердотельный датчик 1′ изображения отличается от твердотельного датчика 1 изображения тем, что множество счетчиков 144 (то есть, счетчик 144, сформированный для каждого столбца) твердотельного датчика 1 изображения заменяются одним общим счетчиком 148. В твердотельном датчике 1′ изображения память 146 сохраняет значение отсчета счетчика 148 в ответ на инверсию сигнала результата сравнения от блока 142 обработки сигналов. В изображенном на Фиг. 2 примере блок 140 считывания принимает решение о том, что значение отсчета общего счетчика 148 для каждого столбца является значением сигнала, считанного от блока 110 восприятия изображения, в соответствии с инверсией выходного сигнала из блока 142 обработки сигналов.

[0041] В вышеописанной компоновке первый транзистор M1, второй транзистор М2 и источник М3 тока обеспечиваются в непосредственной близости друг с другом. Этот предоставляет возможность уменьшить паразитные сопротивления на сторонах истока первого и второго транзисторов M1 и М2. В соответствии с этим, предоставляется возможность улучшения баланса между путем тока, включающим в себя первый транзистор M1, и путем тока, включающим в себя второй транзистор М2, благодаря чему улучшается баланс характеристик дифференциального входа. В результате этого увеличивается точность считывания сигнала пикселов.

[0042] Дополнительные практические варианты осуществления будут разъясняться ниже. Фиг. 4 изображает компоновку блока 110 восприятия изображения твердотельного датчика изображения первого варианта осуществления. Для ясности, множество пикселов 112, формирующих блок 110 восприятия изображения, будут представлены в виде двух строк и двух столбцов пикселов 112. В этом твердотельном датчике изображения первого варианта осуществления, один пиксел 112 формирует один блок пикселов. Каждый пиксел 112 (блок пикселов) включает в себя фотоэлектрический преобразователь PD, такой как, например, фотодиод, первый транзистор M1, второй транзистор М2 и источник М3 тока, сформированный посредством транзистора, и т.п. Каждый пиксел 112 также может включать в себя транзистор МТ переноса и транзистор MR управления напряжением.

[0043] Первый основной электрод (электрод истока) первого транзистора M1 и первый основной электрод (электрод истока) второго транзистора М2 соединяются с общим узлом CN, при этом третий транзистор М3 обеспечивается в пути между общим узлом CN и предварительно заданным потенциалом (в данном примере потенциалом земли). Третий транзистор М3 функционирует в качестве источника следового тока, когда предварительно заданное напряжение Vbias смещения прикладывается к управляющему электроду (затвору). Первый транзистор M1, второй транзистор М2 и источник М3 тока образуют схему дифференциального усилителя. Эта схема, сформированная посредством первого транзистора M1, второго транзистора М2 и источника М3 тока, также может быть рассмотрена в качестве компаратора напряжения для сравнения напряжения управляющего электрода первого транзистора M1 (это напряжение также является напряжением преобразователя fd заряда в напряжение) с напряжением (опорным напряжением VRMP) управляющего электрода второго транзистора М2.

[0044] Операция считывания для считывания сигнала из блока 110 восприятия изображения включает в себя операцию, в которой напряжение, соответствующее зарядам, сгенерированным в фотоэлектрическом преобразователе PD подлежащего считыванию пиксела 112, подается на управляющий электрод первого транзистора M1, при этом изменяющееся во времени опорное напряжение VRMP подается на управляющий электрод второго транзистора М2. Блок 140 считывания считывает сигнал из блока 110 восприятия изображения через второй основной электрод первого транзистора M1 и вертикальный путь 114 передачи.

[0045] Фиг. 5 изображает операцию твердотельного датчика изображения первого варианта осуществления, более конкретно, операцию считывания сигнала двух строк. Фиг. 5 изображает период считывания одной строки в качестве «1Н» (один период горизонтального сканирования). Период считывания первой строки является периодом, в течение которого сигнал φΒ1 смещения первой строки имеет высокий уровень (напряжение смещения), а сигнал φΒ2 смещения второй строки имеет низкий уровень. Когда сигнал φΒ1 смещения активирует источник М3 тока пикселов 112 в первой строке, пикселы 112 в первой строке устанавливаются в выбранное состояние. Когда сигнал φΒ1 смещения дезактивирует источник М3 тока пикселов 112 в первой строке, пикселы 112 в первой строке устанавливаются в невыбранное состояние. Когда сигнал φΒ2 смещения активирует источник М3 тока пикселов 112 во второй строке, пикселы 112 во второй строке устанавливаются в выбранное состояние. Когда сигнал φΒ2 смещения дезактивирует источник М3 тока пикселов 112 во второй строке, пикселы 112 во второй строке устанавливаются в невыбранное состояние.

[0046] В течение периода считывания первой строки предварительно заданное напряжение Vbias смещения прикладывается к затвору транзистора, формирующего каждый источник М3 тока в первой строке, при этом источник М3 тока функционирует в качестве источника постоянного следового тока. Изначально сигнал φR1 управления напряжением активируется до высокого уровня. Вследствие этого, транзистор MR управления напряжением включается, а преобразователь fd заряда в напряжение сбрасывается до напряжения (напряжения сброса), соответствующего напряжению VRES сброса.

[0047] Затем сигнал φR1 управления напряжением дезактивируется до низкого уровня, и преобразователь fd заряда в напряжение отключается. Начальное напряжение опорного напряжения VRMP задается намного большим по сравнению с напряжением сброса преобразователя fd заряда в напряжение, чтобы почти весь электрический ток, который подается посредством источника М3 тока (электрический ток, образованный посредством источника М3 тока), протекал через второй транзистор М2, а электрический ток, протекающий через первый транзистор M1, являлся практически нулевым. Опорное напряжение VRMP линейно понижается, и счетчик 144 (148) измеряет время до инверсии сигнала результата сравнения, выводимого с блока 142 обработки сигналов, вследствие инверсии соотношения величин между напряжением сброса и опорным напряжением VRMP. Значение отсчета, полученное посредством счетчика 144 (148) и сохраненное в памяти 146, является цифровым значением (далее в настоящем документе будет называться значением шума), соответствующим напряжению сброса (уровню шума) пиксела 112. Ссылочная позиция N_AD обозначает операцию сохранения цифрового значения, соответствующего напряжению сброса, в памяти 146 вышеописанным способом.

[0048] Впоследствии опорное напряжение VRMP возвращается к начальному напряжению, при этом сигнал φΤ1 переноса активируется до высокого уровня. Вследствие этого, заряды, которые были подвержены фотоэлектрическому преобразованию и накоплены посредством фотоэлектрического преобразователя PD, переносятся в преобразователь fd заряда в напряжение. После того как сигнал φΤ1 переноса дезактивируется до низкого уровня, опорное напряжение VRMP линейно понижается. Счетчик 144 (148) измеряет время до инверсии сигнала результата сравнения, выводимого с блока 142 обработки сигналов, вследствие инверсии соотношения величин между напряжением преобразователя fd заряда в напряжение и опорным напряжением VRMP. Значение отсчета, полученное посредством счетчика 144 (148) и сохраненное в памяти 146, является цифровым значением (далее в настоящем документе будет называться значением оптического сигнала), соответствующим количеству зарядов, сгенерированных посредством фотоэлектрического преобразования в фотоэлектрическом преобразователе PD пиксела 112. Ссылочная позиция S_AD обозначает операцию сохранения цифрового значения, соответствующего количеству зарядов, сгенерированных посредством фотоэлектрического преобразования, в памяти 146 вышеописанным способом. Значение шума и значение оптического сигнала, сохраненные в памяти 146, могут быть выведены по отдельности. Также можно вывести значение, полученное посредством вычитания значения шума из значения оптического сигнала (то есть, значения, подвергнутого выборке CDS (двойной коррелированной выборке)).

[0049] Второй период считывания является периодом, в течение которого сигнал φΒ2 смещения второй строки имеет высокий уровень (напряжение смещения), при этом сигнал φΒ1 смещения первой строки имеет низкий уровень. Операция считывания второй строки выполняется тем же способом, как и для первой строки.

[0050] Фиг. 6 изображает компоновку блока 110 восприятия изображения твердотельного датчика изображения второго варианта осуществления. Фиг. 7 изображает работу твердотельного датчика изображения второго варианта осуществления, более конкретно, операцию считывания сигнала двух строк. Фиг. 7 изображает период считывания одной строки в качестве «1Н» (один период горизонтального сканирования). Для ясности, множество пикселов 112, формирующих блок 110 восприятия изображения, будут представлены в виде двух строк и двух столбцов пикселов 112. Во втором варианте осуществления два пиксела 112 совместно используют третий транзистор М3, функционирующий в качестве источника следового тока. В первом варианте осуществления сигналы φΒ1 и φΒ2 смещения управляют выбором и снятием выбора строки. Во втором варианте осуществления сигналы φSEL1 и φSEL2 выбора управляют выбором и снятием выбора строки. Кроме того, во втором варианте осуществления транзистор MS выбора обеспечивается между вторым транзистором М2 и источником М3 тока посредством сигналов φSEL (φSEL1 и φSEL2) выбора. Второй вариант осуществления является тем же, что и первый вариант осуществления, за исключением вышеупомянутых отличий.

[0051] Во втором варианте осуществления два пиксела 112 совместно используют третий транзистор М3. Однако третий транзистор М3 может быть совместно использован посредством большего количества пикселов 112. Например, третий транзистор М3 могут совместно использовать пикселы 112, находящиеся в одном столбце.

[0052] Фиг. 8А изображают первый пример блока 142 обработки сигналов, применимого к первому и второму вариантам осуществления. Первая вертикальная линия 114а передачи сигналов соединяется с токовым зеркалом СМ1, сформированным посредством транзистора, такого как, например, p-МОП-транзистор. Вторая вертикальная линия 114b передачи сигналов соединяется с токовым зеркалом СМ2, сформированным посредством транзистора, такого как, например, р-МОП-транзистор. Транзистор М71 обеспечивается между токовым зеркалом СМ1 и опорным потенциалом, транзистор М72 обеспечивается между токовым зеркалом СМ2 и опорным потенциалом, при этом транзисторы М71 и М72 образуют токовое зеркало. В результате этого, напряжение узла вывода между токовым зеркалом СМ1 и транзистором М71 определяется посредством соотношения величин между электрическими токами первой и второй вертикальных линий 114а и 114b передачи сигналов. Сигнал, возникающий в этом узле вывода, выводится в качестве сигнала «comp out» результата сравнения через буферную схему BF, такую как, например, инвертор. Источники CS1 и CS2 тока также могут быть соединены с первой и второй вертикальными линиями 114а и 114b передачи сигналов, соответственно. Источники CS1 и CS2 тока предотвращают обнуление электрического тока, протекающего токовые зеркала СМ1 и СМ2, благодаря чему улучшается характеристика чувствительности блока 142 обработки сигналов. Предпочтительно, чтобы электрические токи, которые подаются посредством источников CS1 и CS2 тока, были меньше электрического тока, который подается посредством источника МЗ тока.

[0053] Фиг. 8В изображает второй пример блока 142 обработки сигналов, применимого к первому и второму вариантам осуществления. Напряжение в первой вертикальной линии 114а передачи сигналов повышается до предварительно заданного напряжения VDD питания посредством нагрузочного повышающего резистора R1. Подобным образом, напряжение во второй вертикальной линии 114b передачи сигналов повышается до напряжения VDD питания посредством нагрузочного повышающего резистора R1. В результате этого, электрические токи, которые протекают через первую и вторую вертикальные линии 114а и 114b передачи сигналов, преобразовываются в напряжения посредством узлов N1 и N2, соответственно. Узлы N1 и N2 соединяются с узлами ввода дифференциального усилителя DA в состоянии разомкнутого контура. Дифференциальный усилитель DA выводит сигнал «comp out» результата сравнения.

[0054] Фиг. 9 изображает компоновку блока 110 восприятия изображения твердотельного датчика изображения третьего варианта осуществления. Для ясности, множество пикселов 112, формирующих блок 110 восприятия изображения, будут представлены в виде двух строк и двух столбцов пикселов 112. Третий вариант осуществления отличается от первого и второго вариантов осуществления тем, что каждый вертикальный путь 114 передачи формируется посредством одной вертикальной линии 114а передачи сигналов. В третьем варианте осуществления предварительно заданный потенциал (например, напряжение VDD питания) подается на второй основной электрод второго транзистора М2. Фиг. 10 изображает первый пример блока 142 обработки сигналов, применимого к третьему варианту осуществления. Вертикальная линия 114а передачи сигналов и источник CS3 тока соединяются с токовым зеркалом СМ3, значение электрического тока, который протекает через вертикальную линию 114а передачи сигналов, сравнивается со значением электрического тока, который протекает через источник CS3 тока, и выводится сигнал «comp out» результата сравнения. Блок 142 обработки сигналов генерирует сигнал «comp out» результата сравнения, указывающий соотношение величин между напряжением преобразователя fd заряда в напряжение и опорным напряжением VRMP в третьем варианте осуществления.

[0055] Фиг. 11 изображает компоновку блока 110 восприятия изображения твердотельного датчика изображения четвертого варианта осуществления. Фиг. 12 изображает работу твердотельного датчика изображения четвертого варианта осуществления, более конкретно, операцию считывания сигнала двух строк. Фиг. 12 изображает период считывания одной строки в качестве «1Н» (один период горизонтального сканирования). Для ясности, множество пикселов 112, формирующих блок 110 восприятия изображения, будут представлены в виде двух строк и двух столбцов пикселов 112.

[0056] В четвертом варианте осуществления, если пиксел 112а является подлежащим считыванию пикселом, то сигнал пиксела 112а считывается посредством использования транзистора М2 пиксела 112b, отличного от пиксела 112а, в качестве второго транзистора. Кроме того, если пиксел 112b является подлежащим считыванию пикселом, то сигнал пиксела 112b считывается посредством использования транзистора M1 пиксела 112а, отличного от пиксела 112b, в качестве второго транзистора. С другой точки зрения, можно расценить, что пикселы 112а и 112b образуют один блок 113 пикселов, при этом блок 113 пикселов включает в себя первый транзистор M1, второй транзистор М2 и источник М3 тока. Операция считывания для считывания сигнала из блока 110 восприятия изображения включает в себя операцию, в которой напряжение, соответствующее зарядам, сгенерированным в фотоэлектрическом преобразователе PD блока 113 пикселов, подается на управляющий электрод первого транзистора M1, при этом изменяющееся во времени опорное напряжение VRMP подается на управляющий электрод второго транзистора М2.

[0057] Напряжение VRES сброса или опорное напряжение VRMP подается на сток транзистора TR управления напряжением через переключатели S (S1 и S2). Более конкретно, напряжение VRES сброса подается на преобразователь fd (fd1 или fd2) заряда в напряжение подлежащего считыванию пиксела 112 (112а или 112b) в блоке 113 пикселов. В то же время, опорное напряжение VRMP подается на преобразователь fd заряда в напряжение пиксела 112 (112а или 112b), который не подлежит считыванию.

[0058] В течение периода считывания первой строки сигналы φS1 и φR2 изменяются на высокоуровневые, а сигнал φS2 изменяется на низкоуровневый. Изначально сигнал φR1 управления напряжением первой строки активируется до высокого уровня. Вследствие этого, транзистор MR управления напряжением пиксела 112а в первой строке включается, а преобразователь fd1 заряда в напряжение пиксела 112а в первой строке сбрасывается до напряжения (напряжения сброса), соответствующего напряжению VRES сброса. Опорное напряжение VRMP подается на преобразователь fd2 заряда в напряжение пиксела 112b во второй строке. В соответствии с этим, подобно первому варианту осуществления, выполняется операция (N_AD) сохранения цифрового значения, соответствующего напряжению сброса, в памяти 146, и операция (S_AD) сохранения цифрового значения, соответствующего количеству зарядов, сгенерированных посредством фотоэлектрического преобразования, в памяти 146.

[0059] В течение периода считывания второй строки сигналы φS2 и φR1 изменяются на высокоуровневые, а сигнал φS1 изменяется на низкоуровневый. Изначально сигнал φR2 управления напряжением второй строки активируется до высокого уровня. Вследствие этого, транзистор MR управления напряжением пиксела 112b во второй строке включается, а преобразователь fd2 заряда в напряжение пиксела 112b во второй строке сбрасывается до напряжения (напряжения сброса), соответствующего напряжению VRES сброса. Опорное напряжение VRMP подается на преобразователь fd1 заряда в напряжение пиксела 112а в первой строке. В соответствии с этим, операция (N_AD) сохранения цифрового значения, соответствующего напряжению сброса, в памяти 14 6, и операция (S_AD) сохранения цифрового значения, соответствующего количеству зарядов, сгенерированных посредством фотоэлектрического преобразования, в памяти 14 6, выполняются для пиксела во второй строке.

[0060] Фиг. 13 изображает компоновку блока 110 восприятия изображения твердотельного датчика изображения пятого варианта осуществления. Фиг. 14 изображает работу твердотельного датчика изображения пятого варианта осуществления, более конкретно, операции считывания сигнала четырех строк. Для ясности, множество пикселов 112, формирующих блок 110 восприятия изображения, будут представлены в виде четырех строк и двух столбцов пикселов 112. В пятом варианте осуществления линия передачи сигналов для подачи опорного напряжения VRMP и линия передачи сигналов для подачи напряжения VRES сброса объединяются в общую линию VRES/VRMP передачи сигналов. Первый переключатель MR1, управление которым осуществляется посредством первого сигнала φR1 управления напряжением, обеспечивается в пути между первым преобразователем fd1 заряда в напряжение и линией VRES/VRMP передачи сигналов. Кроме того, второй переключатель MR2, управление которым осуществляется посредством второго сигнала φR2 управления напряжением, обеспечивается в пути между вторым преобразователем fd2 заряда в напряжение и линией VRES/VRMP передачи сигналов. Более того, в пятом варианте осуществления два фотоэлектрических преобразователя в соседних строках совместно используют один преобразователь заряда в напряжение. Более конкретно, фотоэлектрические преобразователи PD1 и PD2 совместно используют первый преобразователь fd1 заряда в напряжение, а фотоэлектрические преобразователи PD3 и PD4 совместно используют второй преобразователь fd2 заряда в напряжение.

[0061] В течение периодов считывания строк, а именно, с первой по четвертую строку, напряжение Vbias смещения подается на управляющий электрод (затвор) третьего транзистора М3. В течение периода считывания первой строки, первый сигнал φR1 управления напряжением для первой и второй строк активируется до высокого уровня, при этом напряжение сброса (напряжение, которое ниже начального напряжения опорного напряжения) подается с линии VRES/VRMP передачи сигналов. После этого, первый сигнал φR1 управления напряжением дезактивируется до низкого уровня. В течение периода, на протяжении которого первый сигнал φR1 управления напряжением активируется до высокого уровня, выполняется сброс первого преобразователя fd1 заряда в напряжение для первой и второй строк.

[0062] Затем опорное напряжение VRMP подается на линию VRES/VRMP передачи