Архитектура расширения оптической памяти

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в увеличении полосы пропускания запоминающего устройства. Система расширения оптического запоминающего устройства содержит первую электрическую логическую схему для передачи данных в соответствии с протоколом взаимного межточечного соединения для пакетной передачи данных в соответствии с полной скоростью передачи данных; первую промежуточную схему, соединенную для приема данных от первой электрической логической схемы по электрической линии связи, причем первая промежуточная схема выполнена с возможностью преобразования данных в оптический формат, предназначенный для передачи со скоростью, по меньшей мере в два раза большей полной скорости передачи данных; вторую промежуточную схему, соединенную для приема данных в оптическом формате от первой промежуточной схемы по оптической линии связи, причем вторая промежуточная схема выполнена с возможностью преобразования данных в электрический формат, соответствующий протоколу взаимного межточечного соединения для пакетной передачи данных; и вторую электрическую логическую схему, соединенную для приема данных от первой электрической логической схемы, при этом оптическая линия связи инициализируется в соответствии с оптическими обучающими состояниями. 3 н. и 33 з.п. ф-лы, 24 ил., 2 табл.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к оптической связи с системами памяти в главном устройстве. Более конкретно, варианты осуществления изобретения относятся к технологиям обеспечения оптической связи между электронными устройствами (например, ядрами обработки, запоминающими устройствами, контроллерами запоминающего устройства), в соответствии с протоколами, используемыми электронными устройствами.

Уровень техники

По мере повышения вычислительной мощности обработки и увеличения количества ядер обработки, которые могут быть включены в один кристалл, необходимо соответствующее увеличение полосы пропускания запоминающего устройства для поддержания сбалансированных рабочих характеристик системы. Существующая архитектура и технологии обычно не обеспечивают достаточную масштабируемость для обеспечения соответствующего увеличения полосы пропускания запоминающего устройства.

Краткое описание чертежей

Варианты осуществления изобретения представлены в качестве примера, а не для ограничения, и на чертежах одинаковые номера ссылочных позиций обозначают аналогичные элементы.

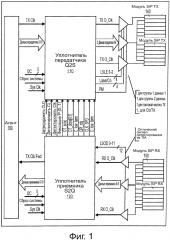

На фиг. 1 показана блок-схема одного варианта осуществления оптического интерфейса.

На фиг. 2 показана временная диаграмма одного варианта осуществления процесса инициализации сигнала интерфейса уплотнителя.

На фиг. 3 показана блок-схема последовательности операций одного варианта осуществления для операции уплотнителя Q2S в состоянии оптической тренировочной структуры.

На фиг. 4 показана блок-схема последовательности операций одного варианта осуществления для операции уплотнителя S2Q в состоянии оптической тренировочной структуры.

На фиг. 5 показана блок-схема одного варианта осуществления системы расширения оптического запоминающего устройства (ОМЕ).

На фиг. 6 показана схема высокого уровня одного варианта осуществления модуля Q2S.

На фиг. 7 показана блок-схема одного варианта осуществления аналогового входного блока Q2S (Q2SAFE).

На фиг. 8 показана блок-схема одного варианта осуществления Q2S, приемного аналогового входного блока (RxAFE).

На фиг. 9а показана принципиальная схема одного варианта осуществления архитектуры RxAFE для операции с нормальной скоростью.

На фиг. 9b показана принципиальная схема одного варианта осуществления архитектуры RxAFE для операции с высокой скоростью.

На фиг.10 показана блок-схема одного варианта осуществления схемы двухвыводного DFE/сэмплера.

На фиг. 11 показана, в качестве примера, схема выборки для половинной скорости.

На фиг. 12 показана схема одного варианта осуществления полного канала передачи данных Q2S и архитектуры канала тактовой частоты.

На фиг. 13 показана схема высокого уровня одного варианта осуществления модуля S2Q.

На фиг. 14 показана блок-схема одного варианта осуществления логики управления (SCL) S2Q.

На фиг. 15 показана блок-схема одного варианта осуществления аналогового входного блока S2Q.

На фиг. 16 показана блок-схема одного варианта осуществления S2Q, приемного аналогового входного блока (RxAFE).

На фиг. 17а показана принципиальная схема одного варианта осуществления архитектуры RxAFE для операции с нормальной скоростью.

На фиг. 17b показана принципиальная схема одного варианта осуществления архитектуры RxAFE для операции с высокой скоростью.

На фиг. 18, в качестве примера, показана схема выборки с квадратичной частотой.

На фиг. 19 показана блок-схема одного варианта осуществления архитектуры схемы передачи S2Q.

На фиг. 20 показана принципиальная схема одного варианта осуществления полной архитектуры канала передачи данных S2Q и канала тактовой частоты.

На фиг. 21 показаны варианты осуществления многопроцессорных конфигураций, использующих архитектуру взаимного соединения с высокими рабочими характеристиками.

На фиг. 22 показан вариант осуществления многоуровневого стека для архитектуры взаимного соединения с высокими рабочими характеристиками.

Подробное описание изобретения В следующем описании представлены различные конкретные детали. Однако варианты осуществления изобретения могут быть выполнены на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и технологии не были подробно представлены для того, чтобы не усложнять понимание данного описания.

Архитектура и технологии, описанные здесь, предусматривают оптический конечный автомат и секвенсер обучающей последовательности, для обеспечения расширения оптического запоминающего устройства. Используя масштабирование технологии, современные встроенные серверные процессоры и графические процессоры уже содержат десятки сотен ядер на одном кристалле, и количество ядер продолжает увеличиваться до тысяч узлов при использовании технологии 11 нм или 8 нм. Соответствующее увеличение полосы пропускания запоминающего устройства и емкости также требуется для повышения сбалансированных рабочих характеристик системы. Эти архитектуры и технологии нацелены на расширение полосы пропускания запоминающего устройства, используя оптические взаимные соединения, называемыми оптическим расширением запоминающего устройства.

В одном варианте осуществления описанные архитектура и технология могут использоваться для внедрения протокола скоростного канала взаимных соединений (QPI) корпорации Intel с оптическими взаимными соединениями с общепринятыми серверами, клиентами, системами на микросхеме (SoC), компьютерами для высокопроизводительных вычислений (НРС), и платформами информационных центров обработки данных. Взаимное соединение QuickPath компании Intel представляет собой взаимное соединение процессора из "точки-в-точку", разработанное компанией Intel<http://en.wikipedia.org/wiki/Intel>, которое на некоторых платформах заменяет системную шину <http://en.wikipedia.org/wiki/Front-side_bus>(FSB).

Протокол QPI представляет собой высокоскоростной протокол пакетной передачи данных для взаимного соединения из точки в точку, который позволяет с помощью узких высокоскоростных соединений соединять вместе обрабатывающие ядра и другие узлы в архитектуре распределенной платформы, работающей в стиле совместно используемого запоминающего устройства. Протокол QPI предлагает широкую полосу пропускания с малой задержкой. Протокол QPI включает в себя протокол слежения, оптимизированный для малой задержки и обладающий высокой степенью масштабируемости, а также структуры пакетов и структуры линий, обеспечивающие быстрое завершение транзакций.

В одном варианте осуществления уровень протокола QPI управляет когерентностью кэш для интерфейса, используя протокол с обратной записью. В одном варианте осуществления также он имеет набор правил для управления некогерентной передачей сообщений. Уровень протокола обычно соединяется с конечным автоматом когерентности кэш в агентах кэширования, и с собственной логикой агента в контроллерах запоминающего устройства. Уровень протокола также отвечает на функции системного уровня, такие как прерывания, I/O, отображаемые запоминающем устройстве, и фиксацию. Одна основная характеристика уровня протокола представляет собой то, что он работает с сообщениями через множество соединений, включающих в себя множество агентов во множестве устройств.

В одном варианте осуществления архитектура и технологии, описанные здесь, используются для расширения QPI с помощью оптического средства. В одном варианте осуществления конечный автомат и секвенсер, описанные ниже, работают так, чтобы получить протокол QPI без информирования о лежащем в его основе оптическом соединении.

В результате масштабирования технологии современные встроенные процессоры сервера и графические процессоры уже содержат от десятков до сотен ядер на одном кристалле, и количество ядер продолжает увеличиваться даже до тысячи или больше при использовании процессов с технологией производства 11 нм или 8 нм. Такая архитектура, описанная здесь, работает для обеспечения такой полосы пропускания запоминающего устройства, используя оптические взаимные соединения, называемые оптическим расширением запоминающего устройства в протоколе QPI.

Для установления оптического домена соединения с полной скоростью передачи данных, как для тактовой частоты, так и для линий передачи данных, необходима фаза оптического обучения. В одном варианте осуществления после нее следует фаза согласования QPI, в течение которой удаленные и промежуточные компоненты устанавливают протокол передачи данных для линии 0 передачи данных и линии 5 передачи данных, для каждой половины оптического соединения. Сообщения передают по оптическому соединению с полной скоростью передачи данных. В одном варианте осуществления фрейм сообщения синхронизируют с опорной тактовой частотой, и только один фрейм сообщения передают за период опорной тактовой частоты.

В одном варианте осуществления сообщение включает в себя преамбулу, команду, данные и заключительную часть. В одном варианте осуществления преамбула представляет собой 16-битовый поток со структурой данных FFFE, которая помечает начало фрейма сообщения. Другие структуры также можно использовать. В одном варианте осуществления поле команды представляет собой 8-битное поле потока для передачи действия для приема интерфейса, который следует применить. Каждый бит представляет команду для очень простого декодирования. Бит 7 может использоваться для расширенных команд, если необходимо. В одном варианте осуществления поле данных представляет собой поле 8-битного потока, содержащее данные, относящиеся к команде. В одном варианте осуществления заключительная часть представляет собой 4-битный поток, повторяющий структуру 1100 для заполнения остаточной части потока данных до конца периода опорной тактовой частоты. Эта структура заканчивается последними двумя битами в потоке, такими, как 0, таким образом, чтобы можно было идентифицировать преамбулу.

На фиг. 1 показана блок-схема одного варианта осуществления оптического интерфейса. Основные компоненты интерфейса представляют собой следующие: 1) микросхема уплотнителя электро (например, QPI) - оптической (например, на основе кремниевой фотоники, SiP) передачи (Тх), (Q2S) 110; 2) микросхема уплотнителя оптико-электрического приема (Рос), (S2Q) 120; 3) возбуждение модулятора; 4) оптический модуль (SiP) передачи (ТХ) 140; 5) приемный (RX) модуль 150 SiP; и 6) трансимпедансный усилитель (TIA).

В одном варианте осуществления промежуточные компоненты (110, 120) содержат 2:1 параллельно-последовательный/последовательно-параллельный преобразователь (SERDES), который мультиплексирует электрические (например, 20 QPI) линии передачи данных в (например, 10) линии, которые стыкуются с модулем SiP, выполняющим электро-оптическое преобразование. В других вариантах осуществления могут поддерживаться другие отношения и другие количества линий. В одном варианте осуществления оптическая линия разделена на две половины, по нижней половине передают нижние линии 0:9 данных, и по верхней половине передают верхние линии 10:19 данных. В других вариантах осуществления могут поддерживаться другие конфигурации.

Агент 190 представляет собой электрический компонент, который связывается с удаленным компонентом (например, запоминающим устройством), который не показан на фиг. 1. Агент 190 может, например, представлять собой ядро обработки или другой системный компонент. В одном варианте осуществления агент 190 предоставляет сигнал тактовой частоты передачи (ТХ), а также данные ТХ (например, 0-19) в микросхему 110 уплотнителя Q2S. В некоторых вариантах осуществления агент 190 также может предоставлять сигнал системной тактовой частоты, сигнал системного сброса и сигнал I2C в микросхему 110 уплотнителя Q2S. В одном варианте осуществления агент 190 принимает из микросхемы 120 уплотнителя S2Q сигнал опережения тактовой частоты ТХ и принимает (RX) данные (например, 0-19). В некоторых вариантах осуществления агент 190 также может предоставлять сигнал системной тактовой частоты, сигнал системного сброса и сигнал I2C в микросхему 120 уплотнителя S2Q.

В одном варианте осуществления микросхема 110 уплотнителя Q2S и микросхема 120 уплотнителя S2Q соединены так, что микросхема 120 уплотнителя S2Q передает сигналы управления в микросхему 110 уплотнителя Q2S. Выходные сигналы из микросхемы 110 уплотнителя Q2S включают в себя сигнал тактовой частоты ТХ (например, ТХ O_Clk), сигналы данных (например, ТХ O_Data 0:9) и сигналы управления в один или больше передающих оптических модулей 140. Входные сигналы в микросхему 120 уплотнителя S2Q включают в себя сигнал тактовой частоты RX (например, RX O_Clk), сигналы данных (например, RX O_Data 0:9) и сигналы управления из одного или больше приемных оптических модулей 150.

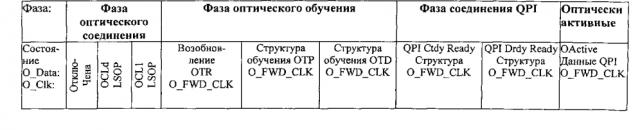

Для установления возможности оптического соединения, конечный автомат, описанный ниже с обучающей последовательностью, используется с оптическим интерфейсом по фиг. 1. В одном варианте осуществления первыми устанавливаются инициирующая последовательность изнутри наружу оптико-электронного соединения, возможность соединения оптического домена. Эта прозрачная оптическая линия затем используется для электрического (например, QPI) согласования параметров связи, и соединение устанавливается между электрическими агентами. Оптический домен имеет 4 основных фазы для последовательности инициализации, представленной в Таблице 1:

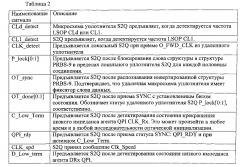

В одном варианте осуществления существует локальный интерфейс уплотнителя между микросхемой 110 уплотнителя Q2S и микросхемой 120 уплотнителя S2Q, которая синхронизирует оптические действия Тх и Rx соединений между двумя компонентами. Этот интерфейс управляется из уплотнителя S2Q 120 и обеспечивает соответствующий переход состояния и фаз уплотнителя Q2S110, соответственно. Один вариант осуществления этого интерфейса определен в Таблице 2.

На фиг. 2 показана временная диаграмма одного варианта осуществления процесса инициализации сигнала интерфейса уплотнителя. В одном варианте осуществления, на фазе 210 оптического соединения оптический модуль вводит состояние оптического соединения либо в ходе полного/"холодного" сброса, "горячего" сброса, или из сброса в полосе (IBreset), детектируемого в электронном (например, QPI) интерфейсе. Функция этого состояния состоит в том, чтобы установить оптическую связь по соединению. В одном варианте осуществления, после ввода в фазу 210 оптического соединения, микросхема 120 уплотнителя S2Q отменяет завершение (в состоянии высокого импеданса), всех линий тактовой частоты и Data Rx на электрической стороне.

В одном варианте осуществления, фаза 210 оптического соединения включает в себя три уровня: Отключено, исходное состояние уровня оптического соединения (OCLd) и уровень 1 оптического соединения (OLC1). В одном варианте осуществления, на уровне отключения после приема сигнала получения пихания или "холодного" сброса, оптический домен переходит в отключенное состояние. Микросхема 120 уплотнителя S2Q при этом отменяет завершение (в состоянии высокого импеданса), всех линий интерфейса тактовой частоты и данных RX на электрической стороне. В отключенном состоянии все лазеры выключены. Все логические состояния инициализируют до их состояния сброса при включении питания. После окончания сигнала "сброс" оптический модуль входит в оптическое состояние. В одном варианте осуществления все PLL блокированы, во время состояния отключения.

В одном варианте осуществления, в состоянии OCLd, оптический модуль передает оптические импульсы с низкой скоростью LSOP через оптические линии тактовой частоты O_CLK между оптическими модулями, которые содержат соединение. В одном варианте осуществления LSOP представляет собой LSLE при заданной скорости CLd и рабочем цикле, используя разрешенную работу лазера для передачи с низкой скоростью. В одном варианте осуществления выходной сигнал LSLE включает и выключает лазер вместо использования схемы модулятора высокой мощности. В одном варианте осуществления это осуществляется только в линиях опережения тактовой частоты в этом состоянии, для определения исходной оптической связи по соединению.

В одном варианте осуществления, в этом состоянии микросхема 110 уплотнителя Q2S поддерживает свое состояние завершения Rx в состоянии высокого импеданса для обеих линий тактовой частоты и передачи данных. Это предотвращает выход электрического агента (например, 190 на фиг. 1) за пределы состояния детектирования тактовой частоты протокола инициализации электрического соединения.

В одном варианте осуществления микросхема 120 уплотнителя S2Q при приеме сигнала LSOD выполняют детектирование света из удаленного оптического модуля. В одном варианте осуществления, когда микросхема 120 уплотнителя S2Q принимает три последовательных LSOP, она вырабатывает сигнал CLd_detected для идентификации локальной микросхемы 110 уплотнителя Q2S, которая принимает импульсы. Следует отметить, что возможно принимать LSOP со скоростью CL1, зависящей от порядка, в котором подключены кабели. В этом случае микросхема 120 уплотнителя S2Q будет подсчитывать 16 последовательных импульсов CL1 перед активацией сигнала CLddectect.

В одном варианте осуществления микросхема 110 уплотнителя Q2S остается в состоянии OCLd минимум в течение времени TCLD_sync, которое определено регистром CSR. В этом варианте осуществления микросхема 110 уплотнителя Q2S переходит в состояние OCL1 после выработки сигнала CLd_dectect и по завершению работы таймера TCLD_sync.

В одном варианте осуществления состояние Уровень 1 оптического соединения обозначает, что микросхема 120 уплотнителя S2Q принимает LSOP по линиям тактовой частоты и вырабатывает сигнал CLd_detect. В одном варианте осуществления микросхема 110 уплотнителя Q2S подтверждает CLd_dectect путем передачи LSOP по линиям O_CLK с определенной скоростью CL1. Когда микросхема 120 уплотнителя S2Q принимает два последовательных импульса CL1 (после выработки CLd_detect), она подает сигнал CLl_detect, обеспечивающий переход 110 уплотнителя Q2S в фазу оптического обучения.

В одном варианте осуществления, если микросхема 110 уплотнителя Q2S прекращает принимать LSOP по линиям O_CLK в течение неактивного периода, она формирует сигналы CLd_detect и CLl_detect. Затем микросхема 110 уплотнителя Q2S переходит обратно в состояние OCLd и перестает передавать LSOP в течение периода времени для повторной синхронизации LSOP, для синхронизации последовательности оптического соединения.

В варианте осуществления, в состоянии ОСЫ, микросхема 110 уплотнителя Q2S поддерживает свое завершение Rx в состоянии высокого импеданса для обоих линий передачи тактовой частоты и данных. Это предотвращает выход электрического агента за пределы состояния детектирования тактовой частоты в протоколе инициализации QPI.

Назначение фазы 230 оптического обучения состоит в том, чтобы устанавливать оптический домен соединения с полной скоростью передачи данных по обеим линиям для передачи тактовой частоты и данных. В этой фазе O_FWD_CLK начинает передачу во время состояния восстановления обучения при рабочей тактовой частоте, используя выход модулятора. В то же время микросхема 110 уплотнителя Q2S начинает передачу заранее выбранной структуры (например, структуры PRBS-9) по линиям передачи данных для обучения соединения.

В состоянии восстановления оптического обучения, OTR, оптоволоконное соединение было установлено на обоих концах оптического соединения. В этом состоянии микросхема уплотнителя Q2S прекращает передачу LSOP и начинает передачу O_FWD_CLK, используя модулированный выходной сигнал. Тактовая частота будет передана при рабочей скорости тактовой частоты, (например, 3,2 ГГц), генерируемой из опорной тактовой частоты PLL. Альтернативная операция в медленном режиме будет описана в других местах. Когда микросхема уплотнителя S2Q фиксируется на O_FWD_CLK, она передает сигнал CLK_detect и переходит в состояние структуры оптического обучения.

Цель состояния структуры оптического обучения состоит в том, чтобы обучить оптическое соединение и установить взаимосвязи фаз электрической линии для мультиплексированных данных по оптической линии в соответствии с опережающей оптической тактовой частотой. В одном варианте осуществления это выполняется путем передачи заданной структуры (например, PRBS 9) через линию оптических данных с четными битами (0, 2, 4, …), генерируемыми в линии А для пучка линий передачи данных и нечетных битов (1, 3, 5, …) в линии В для пучка линий передачи данных. В одном варианте осуществления дополнительный бит добавляют к стандартным потокам битов 511, для получения нечетного количества битов. Ориентацию линии демультиплексирования выводят из синхронизации управления высокоскоростного канала передачи данных по структуре фиксирования слова.

В одном варианте осуществления таймер фиксации данных начинает работу, когда подают одну из P_lock [0:1], и выключается, когда подают оба сигнала. В случае окончания работы таймера, микросхема уплотнителя предполагает, что нет возможности обеспечить фиксацию структуры, и отключает половину соединения, по которой не был передан его сигнал фиксации структуры. Затем обработка переходит к оптической инициализации оптического домена в режиме половины соединения. Микросхема уплотнителя останется в состоянии OTP, если не будет подан ни один из сигналов Р_lock.

На фиг. 3 показана блок-схема последовательности операций одного варианта осуществления работы уплотнителя Q2S в течение состояния структуры оптического обучения. В одном варианте осуществления, во время состояния структуры оптического обучения, микросхема уплотнителя Q2S передает заданную структуру обучения 305. В одном варианте осуществления она представляет собой структуру обучения PRBS-9; однако, другие структуры обучения также могут использоваться.

Микросхема уплотнителя Q2S ожидает приема сигнала тактовой частоты из уплотнителя S2Q, 310. В одном варианте осуществления, в состоянии OTP, (подан сигнал Clk_detect), S2Q выполняет обучение по входящему потоку данных, присутствующему в линиях передачи данных. В случае, когда она будет затем зафиксирована по структуре слова по всем линиям передачи данных, содержащимся в половине соединения, 315, микросхема уплотнителя S2Q подает соответствующий сигнал Р_lock [0:1].

В одном варианте осуществления, после подачи сигнала Р_lock, микросхема уплотнителя Q2S передает инвертированную, предварительно выбранную (например, PRBS-9) структуру по одной из линий данных для соответствующей половины соединения, 320. Это действует, как подтверждение для удаленного конца о том, что выполняется приема и была выполнена фиксация потока битов. В одном варианте осуществления Q2S не требуется ожидать обоих сигналов Р_lock или Р_lock по истечению времени для передачи инвертированных данных. Следует отметить, что при этом возможно принимать инвертированную структуру PRBS перед достижением фиксации локальной структуры. Схема фиксации, в этом случае, должна будет различать не инвертированную или инвертированную структуру.

После выработки сигнала OT_sync, 325, микросхема уплотнителя Q2S передает в сообщении Sine синхронизации полосы Р_lock и состояние обучение выполнено, 350. Если микросхема уплотнителя находится в диагностическом режиме, 330, статус выполнено не будет передан. В диагностическом режиме передают команду на запуск, 335, и запускается диагностика, 340, пока не будет принята команда остановки, 345. Статус выполнено передают, 350, после окончания режима диагностики для вывода оптического соединения из фазы обучения. Микросхема уплотнителя Q2S передает сообщение Sine со статусом QPI_rdy, обозначающим, что ее локальный агент QPI готов передавать тактовую частоту FWD и что оптическое обучение закончено (OT_done), 355.

На фиг. 4 показана блок-схема последовательности операций одного варианта осуществления для работы уплотнителя S2Q во время состояния структуры оптического обучения. В одном варианте осуществления S2Q принимает переданный сигнал тактовой частоты из уплотнителя Q2S. После получения фиксации бита по сигналу тактовой частоты, 400, микросхема уплотнителя S2Q передает сигнал Clk_detect, 405, в микросхему уплотнителя Q2S, переходящую в состояние оптического обучения. Микросхема уплотнителя Q2S продолжает передавать структуру обучения (например, PRJBS-9) по линиям передачи данных.

В одном варианте осуществления, в состоянии OTP, (при переданном Clk_detect), микросхема уплотнителя S2Q выполняет обучение по входящему потоку данных, присутствующих в линиях 0_DRx. После ее успешной фиксации по структуре слова для всех линий передачи данных, содержащихся в половине соединения, 410, микросхема уплотнителя S2Q подает соответствующий сигнал Р_lock [0:1], 415. В одном варианте осуществления, после распознавания инвертированной обучающей структуры для минимального числа (например, 2, 3, 4) успешных последовательностей по обеим половинам соединения, 420, микросхема уплотнителя S2Q подает сигнал OT_sync, 425. В одном варианте осуществления, если истекает время для Р_lock, тогда сигнал OT_sync будет передан, и последовательность инициализации продолжается с использованием половины соединения, которая закончила обучение. Выработка OT_sync обозначает, что удаленная микросхема уплотнителя S2Q имеет фиксацию структуры данных и что локальная микросхема уплотнителя приняла подтверждение, как обозначено инвертированной структурой обучения. S2Q принимает сообщение Sine с активным битом статуса выполнено, 430, она передает сигналы OT_done [0:1], 450, в соответствии со статусом Р_lock переданным в сообщении.

В заключение описания фиг. 3 и 4 микросхемы уплотнителя Q2S и S2Q находятся в состоянии выполненного оптического обучения (OTD). Назначение состояния выполненного оптического обучения состоит в том, чтобы синхронизировать готовность электрического агента по окончанию оптического обучения. В одном варианте осуществления микросхема уплотнителя Q2S продолжает находиться в этом состоянии, передавая инвертированную структуру обучения до тех пор, пока она не детектирует, что электрический агент находится в состоянии низкого импеданса. Следует отметить, что электрический агент мог бы включить состояние низкого импеданса в любое время в течение последовательности оптической инициализации.

Что касается фиг. 2, фаза 250 соединения QPI отвечает за установление электрического соединения агента QPI с оптическим доменом, (компоненты уплотнителя). На этой фазе состояние детектирования тактовой частоты QPI из удаленного Агента QPI, синхронизируется с состоянием детектирования тактовой частоты QPI локального агента QPI, как обозначено сигналом QPI_rdy уплотнителя S2Q. В состоянии, готовности приема данных QPI, QPI Drdy, микросхема уплотнителя S2Q будет определять входные данные линии передачи данных из агента QPI. Когда она определяет значение постоянного тока, (1 или 0), она переходит к внутренним линиям передачи данных из генератора структуры к линиям передачи данных от агента QPI. В оптически активном состоянии модуль SiP является прозрачным для соединения QPI.

В альтернативных вариантах осуществления другие протоколы, кроме QPI, можно использовать в обучающих последовательностях с другой длиной, скремблированных с другими структурами PRBS и/или рассеянными с другими структурами, используемыми для обучения и/или быстрой фиксации.

На фиг. 5 показана блок-схема одного варианта осуществления системы расширения оптического запоминающего устройства (ОМЕ). В одном варианте осуществления системная архитектура по фиг. 5 включает в себя конструкцию микроархитектуры уплотнителя для формирования интерфейса для оконечных агентов ядра QPI обработки с оптическим расширением для взаимного соединения со строительными блоками Тх и Rx, и схемами примеров варианта осуществления.

В одном варианте осуществления микросхема уплотнителя имеет два типа модулей. Микросхема уплотнителя 510 Q2S и микросхема уплотнителя 545 Q2S представляют собой модули одного и того же типа, которые принимают сигналы от конечного агента QPI (например, ядро 505, ядро 540), и передают эти сигналы в модуль возбуждения модулятора SiP (например, 515, 550). В следующем описании, модули этого типа называются модулем Q2S (QPI2SIP) или микросхемой уплотнителя Тх.

В одном варианте осуществления модуль Q2S (например, 510, 545) принимает дифференциальные сигналы передачи Данных в 20 линиях с собственной скоростью QPI (например, 6,4 Гбит/с, 8 Гбит/с, 9,6 Гбит/с, 11,2 Гбит/с, 12,8 Гбит/с), и дифференциальные сигналы тактовый частоты с опережением по одной линии тактовой частоты с половинной частотой относительно скорости передачи данных (соответственно, 3,2 ГГц, 4 ГГц, 4,8 ГГц, 5,6 ГГц и 6,4 ГГц) из оконечного агента QPI (например, 505, 540). Другие рабочие частоты также могут поддерживаться. Затем модуль Q2S (например, 510, 545) будет обеспечивать соответствующую выборку данных, используя сэмплеры с половинной частотой, перенастроенные с использованием буфера синхронизации, последовательно включенные (2:1) в потоки данных с удвоенной частотой (соответственно, 12,8 Гбит/с, 16 Гбит/с, 19,2 Гбит/с, 22,4 Гбит/с, 25,6 Гбит/с), и передаваемые в модули возбуждения модулятора SiP (например, 515, 550). Следовательно, в одном варианте осуществления выходы Q2S имеют 10 линий для передачи данных с удвоенной скоростью передачи данных и одну линию передачи тактовой частоты при половинной частоте передачи данных. В альтернативном варианте осуществления линия передачи тактовой частоты может отсутствовать, и любые и все из линий данных можно использовать вместо линии для передачи тактовой частоты.

В одном варианте осуществления модуль S2Q (например, 535, 570) принимает дифференциальные сигналы данных по 10 линиям с удвоенной частотой передачи данных и дифференциальные сигналы тактовой частоты по одной линии тактовой частоты с частотой, составляющей половину частоты, из модуля TIA (например, 530, 565). Аналогично, модули S2Q (например, 535, 570) обеспечивают то, что сигналы будут правильным образом квантованы с использованием сэмплеров с квадратичной частотой, перенастроенные с буферами синхронизации, включенными последовательно (2:1) в потоки данных с полной скоростью передачи данных, и передаваемые в разные оконечные агенты QPI (например, 540, 505). Следовательно, выходы Q2S (например, 535, 570) возвращаются обратно в 20 линии передачи данных при собственной скорости QPI и одной линии передачи тактовой частоты с частотой, составляющей половину скорости передачи данных. В одном варианте осуществления операции между микросхемой уплотнителя Q2S и микросхемой уплотнителя S2Q (например, 510-535 и 545-570) должны быть прозрачными для оконечных агентов QPI (505, 540), за исключением индуцированной задержки.

На фиг. 6 показана схема верхнего уровня одного варианта осуществления модуля Q2S. В одном варианте осуществления модуль 600 Q2S включает в себя два основных участка: цифровая сторона 610 и аналоговая сторона 650. В одном варианте осуществления цифровая сторона 610 включает в себя цепь 615 сканирования, регистры 620 управления и состояния, логические схемы оптического управления (OCL) 625 и логическую схему 630 управления Q2S (QCL). В одном варианте осуществления аналоговая сторона 650 включает в себя систему 655 фазовой автоподстройки частоты (PLL), модуль (VRM) 660 регулятора напряжения, аналоговый генератор 665 и аналоговый входной блок (Q2SAFE) Q2S 670.

Ключевой блок в модуле 600 микросхемы уплотнителя Q2S представляет собой модуль 670 Q2SAFE, который выполняет прием данных восстановления синхронизации, преобразования в последовательные данные 2:1, и передачу данных с удвоенной скоростью в возбуждение модулятора SiP. Качество конструкции Q2SAFE и ее воплощение определяют рабочую скорость, задержку и потребление энергии уплотнителя 600 Q2S.

В одном варианте осуществления QCL 625 представляет собой логическую схему, которая содержит несколько модулей, которые управляют функций Q2SAFE 670. QCL 625 не является частью пути передачи данных, но она обеспечивает установку синхронизации буфера, которая приводит к различной задержке в канале передачи данных. В одном варианте осуществления QCL 625 состоит, по меньшей мере, из следующих функций для управления каналом передачи данных и управления каналом передачи тактовой частоты.

В одном варианте осуществления, при управлении каналом передачи данных, QCL 625 обеспечивает, по меньшей мере, соединение онлайн (описанное ниже), синхронизацию буфера (Sync_FIFO), управление Icomp, управление Rcomp, управление AG и DFE, управление PLL и управление DFX. В одном варианте осуществления, при управлении каналом передачи тактовой частоты, QCL 625 обеспечивает, по меньшей мере, управление CDR, детектирование активности тактовой частоты, переданной с опережением, и управление PLL

На фиг. 7 показана блок-схема одного варианта осуществления аналогового переднего блока предварительной обработки данных по Q2S (Q2SAFE). Q2SAFE 670 представляет собой канал передачи данных по Q2S 600. В одном варианте осуществления Q2SAFE 670 определяет рабочие характеристики модуля 600 с микросхемой Q2S. В одном варианте осуществления Q2SAFE 670 включает в себя 3 основных блока: RxAFE 710, SyncFIFO 730 и TxAFE 750, как показано на фиг. 7. Функция RXAFE 710 состоит в том, чтобы принимать, усиливать для различения дифференциального аналогового сигнала с малым размахом колебаний с входных контактных площадок переходной платы SiP, и для выборки приблизительно в центре данных. Функция SyncFIFO 730 состоит в том, чтобы синхронизировать передаваемые сигналы тактовой частоты и тактовую частоту передачи уплотнителя, для восстановления временных характеристик принимаемых данных, для того, чтобы остановить накопление дрожания и для минимизации дрейфа PVT. Функция TxAFE 750 состоит в том, чтобы преобразовать в последовательную форму (2:1) потоки данных и передать в модуль возбуждения SiP.

На фиг. 8 показана блок-схема одного варианта осуществления Q2S, аналогового приемного блока предварительной обработки (RxAFE) для Q2S. В одном варианте осуществления, схема 820 аналогового приемного блока предварительной обработки (RxAFE) в Q2S работает для приема, усиления, выборки дифференциальных сигналов данных (например, с контактных площадок 810), и выполнения непрерывного поддержания фазового интерполятора (PI). В одном варианте осуществления выход Q2S RxAFE 820 будет передан повторно в блок восстановления тактовой частоты, называемый Sync_FIFO. В одном варианте осуществления блок 820 RxAFE соединен с площадкой 810 массива решетки с шариковыми контактами (BGA) переходной платы SiP через схему 830 защиты ESD. Входные узлы также совместно используются с завершениями Rt 840 и детектором 850 активности соединения.

На фиг. 9а показана принципиальная схема одного варианта осуществления архитектуры RxAFE для работы с нормальной скоростью. На фиг. 9b показана принципиальная схема одного варианта осуществления архитектуры RxAFE для операции с высокой скоростью. Внутренняя архитектура RxAFE показана на фиг. 9а, и 9b, присутствующих в двух вариантах цепей (фиг. 9а) с номинальной скоростью, (например, 6,4 Гб/с); и на (фиг. 9b) с высокой скоростью, (например, 9,6 Гбит/с, вплоть до 12,8 Гбит/с). На фиг. 9а представлена двусторонняя архитектура приемника с перемежением, состоящая из дифференциального буфера 905, после чего следует сэмплер 910, запоминающее устройство 915 CDR для восстановления синхронизации, интерполятор 920 фазы для генерирования тактовой частоты выборки.

На фиг. 9b показана архитектура двустороннего приемника с перемежением, включающая в себя непрерывный эквалайзер 950 с непрерывным временем (CTLE), с автоматическим регулированием 955 усиления (AGC), после которого следует эквалайзер обратной связи для передачи решения (ОРЕ)/сэмплер 960, модуль CDR 970 для восстановления синхронизации, интерполятор 975 фазы для генерирования тактовой частоты выборки. В одном варианте осуществления два варианта выбора могут быть воплощены с использованием перепуска или выбора мультиплексора для выполнения обеих архитектур в одной конструкции.

Технология эквализации может компенсировать эффекты канала, такие как взаимные помехи между символами в области времени (ISI), потери, зависящие от частоты, дисперсию и отражение. В одном варианте осуществления два каскада эквализации используются в архитектуре на фиг. 9b. В одном варианте осуществления первый каскад может представлять собой CTLE, воплощенный с использованием усилителя Черри-Хупера для усиления канала по частоте. Второй каскад представляет собой DFE, в котором используется DFE с программны