Способ и устройство счета импульсов

Иллюстрации

Показать всеИзобретение относится к области цифровой вычислительной техники и может быть использовано в устройствах цифровой автоматики. Техническим результатом является увеличение быстродействия, уменьшение аппаратных затрат в декадах двоично-десятичных счетчиков и повышение надежности за счет упрощения конструкции устройства. Он достигается тем, что каждая десятичная цифра представляется четырьмя двоичными кодами, счет выполняют за счет занесения в младший разряд кода «1» или «0» и сдвигом на один разряд между первым-четвертым разрядами в сторону старших разрядов. Каждый десятичный разряд устройства содержит три логических элемента И-НЕ, логический элемент И, вход СИ счетных импульсов, вход CLR установки устройства в нуль, вход СЕ разрешения работы от предыдущей младшей тетрады счетчика, выход сигнала CR разрешения работы в старшую тетраду и четыре двоичных разряда, при этом каждый двоичный разряд содержит один RS-триггер, выполненный на основе двух логических элементов И-НЕ, и четыре логических элемента И-НЕ, тактовый вход ТИ и вход установки в нуль. 2 н.п. ф-лы, 1 ил., 1 табл.

Реферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в устройствах цифровой автоматики.

Известны способы и устройства счета импульсов (см., например, Угрюмов Е.П. Цифровая схемотехника. СПб: БХВ - Санкт-петербург, 2000, стр. 160, рис. 3.50; Лехин С.Н. Схемотехника ЭВМ. СПб: БХВ - Санкт-петербург, 2010, стр. 370, рис. 5.130; Бабич Н.П., Жуков И.А. Основы цифровой схемотехники: учебн. пос. М.: Издательский дом «Додэка-XXI», К.: «МК-Пресс», 2007, стр. 135, рис. 3.21). В данных счетчиках кодирование информации в десятичной декаде выполняется в коде 8421 или 8421+3, каждый разряд счетчика содержит один триггер, выполненный на основе логических элементов И-НЕ или ИЛИ-НЕ, реализует логику работы JK- или Т-триггера, организована синхронная работа разрядов, переносы между разрядами десятичной декады и перносы в старшую декаду.

Недостатком данных схем является наличие дополнительных логических элементов в цепях переноса между разрядами десятичной декады.

Известен счетчик импульсов (RU №2308801 С1, МПК H03K 23/40, заявлен 15.02.2006, опубликован 20.10.2007, Бюл. №29), в котором каждый разряд счетчика содержит один RS-триггер, четыре элемента И, три элемента ИЛИ, четыре элемента ИЛИ, четыре элемента НЕ, четыре шины управления и информационный вход.

Недостатком данного счетчика является то, что сигнал переноса внутри тетрады формируется как сквозной перенос между разрядами во время паузы между импульсами, что достигается за счет дополнительных затрат оборудования.

Наиболее близким изобретением того же назначения к заявленному изобретению по совокупности признаков являются принятые за прототип способ и устройство счета импульсов (RU №2538949 С1, МПК H03K 23/50, заявлено 03.10.2013, опубликованы 10.01.2015, Бюл. №1). В способе-прототипе счета импульсов каждую десятичную цифру одного разряда (декаду) представляют четырьмя двоичными разрядами, при этом десятичные цифры от нуля до девяти одной тетрады представляют двоичными кодами четырех триггеров 0000, 0001, 0010, 0100, 1000, 1001, 1010, 1100, 1101 и 1110 соответственно, выполнение счета импульсов от «0» до «9» производят путем добавления «1» к коду числа, хранящемуся в первом-четвертом триггерах тетрады A1, А2, A3, А4, при этом добавление «1» к коду тетрады осуществляется путем занесения «1» в А1 или сдвига «1» на один разряд в сторону старших двоичных разрядов, первым счетным импульсом СИ 1 при нулевых значениях A1, А2 и A3, т.е. not A1 and not A2 and not A3=1, устанавливают A1 в «1», вторым счетным импульсом СИ 2 устанавливают А2 в «1» и устанавливают А1 в «0», третьим счетным импульсом СИ 3 устанавливают A3 в «1», а А2 в «0», четвертым счетным импульсом СИ 4 устанавливают А4 в «1», а A3 в «0», при этом код А4 сохраняют до конца счета в рассматриваемой тетраде, пятым СИ 5 при not A1 and not A2 and not A3=1 принимают код «1» в A1, шестым счетным импульсом СИ 6 устанавливают А2 в «1», а А1 в «0», седьмым счетным импульсом СИ 7 устанавливают A3 в «1», а А2 в «0», при этом код A3 сохраняют до конца счета в рассматриваемой тетраде, при условии А4 and not A3 and not A2=1 по СИ 8 разрешают запись кода «1» в A1, по СИ 9 устанавливают А2 в «1» и А1 в «0», по десятому СИ 10 формируют сигнал переноса СП в старшую тетраду, при этом СП=А4 and A3 and А2 and СИ 10=1, и устанавливают все триггеры тетрады в «0», подавая СП по цепи вторых элементов ИЛИ, первых элементов И, вторых элементов НЕ на нулевые входы каждого RS-триггера тетрады.

Устройство-прототип счета импульсов выполнено на логических элементах И, ИЛИ, НЕ, содержащее в каждой десятичной декаде четыре двоичных разряда, четыре логических элемента И, один логический элемент ИЛИ, вход установки устройства в нуль, вход счетных импульсов из младшей тетрады, выход счетных импульсов в старшую тетраду, причем каждый из двоичных разрядов выполнен на основе одного RS-триггера, а также содержит три логических элемента И, два логических элемента ИЛИ, три логических элемента НЕ.

Недостатком прототипа является большие аппаратные и временные затраты, связанные с большим количеством логических элементов в цепях распространения сигналов.

К причинам, препятствующим достижению указанного ниже технического результата, относятся большие аппаратные затраты и связи между ними, что приводит к снижению быстродействия, уменьшению надежности и усложнению устройства.

Задача, на решение которой направлено заявляемое изобретение, состоит в том, чтобы разработать способ и устройство для счета импульсов, техническим результатом которых является увеличение быстродействия, уменьшение аппаратных затрат в декадах двоично-десятичных счетчиков и повышение надежности за счет упрощения конструкции устройства.

Поставленная задача решается способом счета импульсов, заключающимся в представлении каждой десятичной цифры от нуля до девяти одного разряда (декады) четырьмя двоичными разрядами, при этом выполнение счета импульсов от «0» до «9» производят путем добавления «1» к коду числа, хранящемуся в первом-четвертом триггерах Q1, Q2, Q3, Q4 тетрады,

отличающимся тем, что десятичные цифры от нуля до девяти одной тетрады представляют двоичными кодами 0000, 0001, 0011, 0111, 1111, 1110, 1101, 1010, 0101 и 1011 соответственно, перед началом счета все триггеры устанавливают в нулевое состояние, подавая сигнал сброса CLR=0 на входы установки в «0» каждого триггера, затем на входе сброса устанавливают единичное значение CLR=1, счетные импульсы СИ, при наличии единичного значения на внешнем входе разрешения работы СЕ=1 от предыдущей младшей тетрады счетчика, инвертируют, формируют сигнал счета ТИ=not (СИ and СЕ), который поступает на тактовые входы всех триггеров Q1, Q2, Q3, Q4,

добавление «1» к коду тетрады осуществляют по первому-девятому счетным импульсам СИ путем занесения в младший триггер Q1 кода «1», при условии D1=not(Q1 and Q4)=1, т.е. при нулевом значении хотя бы на одном из прямых выходов соответственно первого триггера Q1 или четвертого триггера Q4, или кода «0», при условии D1=not(Q1 and Q3)=0, т.е. при единичных значениях на прямых выходах соответственно первого триггера Q1 и четвертого триггера Q4, и выполняют сдвиг между разрядами тетрады на один разряд в сторону старших двоичных разрядов для второго Q2, третьего Q3 и четвертого Q4 триггеров, после девятого счетного импульса СИ 9 формируют нулевое значение сигнала установки триггеров в «0», при условии D9=not (Q4 and not Q3 and Q1)=0, т.е. при единичных значениях на прямых выходах соответственно четвертого Q4 и первого триггера Q1 и инверсном выходе третьего триггера not Q3, и единичное значение сигнала разрешения работы CR=1 в старшую тетраду, при этом CR=Q4 and not Q3 and Q1 and CE=1, по десятому счетному импульсу СИ 10 все триггеры Q1, Q2, Q3, Q4 тетрады устанавливают в «0».

Также предложено устройство счета импульсов, содержащее в каждой десятичной декаде четыре двоичных разряда 11, 12, 13, 14, логический элемент И 11, вход 14 счетных импульсов СИ устройства и вход 12 установки устройства в нуль CLR, причем каждый из двоичных разрядов выполнен на основе одного RS-триггера,

отличающееся тем, что в него дополнительно введены первый 8, второй 9 и третий 10 логические элементы И-НЕ устройства, вход 13 разрешения работы устройства СЕ от предыдущей младшей тетрады счетчика, внешние выходы разрядов устройства 151, 152, 153, 154 и выход 16 сигнала разрешения работы CR в старшую тетраду, а в каждом двоичном разряде тетрады RS-триггера выполнены на основе первого 2 и второго 3 логических элементов И-НЕ и дополнительно введены третий 4, четвертый 5, пятый 6 и шестой 7 логические элементы И-НЕ и тактовый вход ТИ двоичного разряда,

причем выходы первых элементов И-НЕ 2 каждого разряда являются прямыми Q выходами RS-триггера, а также являются внешними выходами устройства 151, 152, 153, 154 соответственно, выходы вторых элементов И-НЕ 3 каждого разряда являются инверсными NQ выходами RS-триггера, выход первого элемента И-НЕ 2 соединен с первым входом второго элемента И-НЕ 3, выход которого соединен со вторым входом первого элемента И-НЕ 2,

первый вход которого соединен с выходом третьего элемента И-НЕ 4, первым входом пятого элемента И-НЕ 6 и первым входом четвертого элемента И-НЕ 5, третий вход которого соединен с третьим входом третьего элемента И-НЕ 4 и является тактовым входом ТИ двоичного разряда, выход шестого элемента И-НЕ 7 соединен со вторым входом пятого элемента И-НЕ 6 и вторым входом четвертого элемента И-НЕ 5, выход которого соединен со вторым входом второго элемента И-НЕ 3 и со вторым входом шестого элемента И-НЕ 7, первый вход которого соединен с первым входом третьего элемента И-НЕ 4 и является входом установки триггера в нулевое состояние,

вход 12 установки устройства в нуль CLR соединен с входами установки всех триггеров в нулевое состояние,

вход 13 разрешения работы устройства СЕ от предыдущей младшей тетрады счетчика соединен с четвертым входом элемента И 11 устройства и первым входом третьего элемента И-НЕ 10 устройства, второй вход которого соединен с входом 14 счетных импульсов СИ устройства, а выход третьего элемента И-НЕ 10 устройства соединен с тактовыми входами ТИ каждого двоичного разряда 11, 12, 13, 14,

прямой Q1 выход 151 первого двоичного разряда 11 соединен с третьим входом шестого элемента И-НЕ 7 второго двоичного разряда 12, прямой Q2 выход 152 второго двоичного разряда 12 соединен с третьим входом шестого элемента И-НЕ 7 третьего двоичного разряда 13, прямой Q3 выход 153 третьего двоичного разряда 13 соединен с третьим входом шестого элемента И-НЕ 7 четвертого двоичного разряда 14,

первый вход первого элемента И-НЕ 8 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, а второй вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, выход первого элемента И-НЕ 8 устройства соединен с третьим входом шестого элемента И-НЕ 7 первого двоичного разряда 11,

первый вход второго элемента И-НЕ 9 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход второго элемента И-НЕ 9 устройства соединен с четвертым входом шестого элемента И-НЕ 7 второго двоичного разряда 12 и с четвертым входом шестого элемента И-НЕ 7 третьего двоичного разряда 13,

первый вход элемента И 11 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход элемента И 11 является выходом 16 сигнала разрешения работы CR в старшую тетраду.

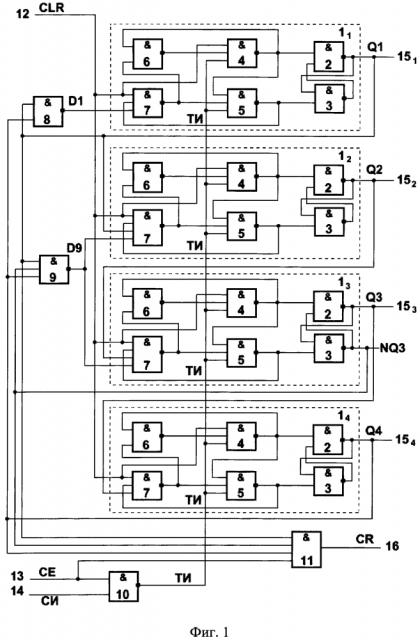

На фиг. 1 приведена схема устройства, реализующего предлагаемый способ счета импульсов.

На фиг. 1 приняты следующие обозначения:

11, 12, 13, 14 - двоичные разряды,

2 - первый логический элемент И-НЕ двоичного разряда,

3 - второй логический элемент И-НЕ двоичного разряда,

4 - третий логический элемент И-НЕ двоичного разряда,

5 - четвертый логический элемент И-НЕ двоичного разряда,

6 - пятый логический элемент И-НЕ двоичного разряда,

7 - шестой логический элемент И-НЕ двоичного разряда,

8 - первый логический элемент И-НЕ устройства,

9 - второй логический элемент И-НЕ устройства,

10 - третий логический элемент И-НЕ устройства,

11 - логический элемент И устройства,

12 - вход установки устройства в нуль CLR,

13 - вход разрешения работы устройства СЕ от предыдущей младшей тетрады,

14 - вход счетных импульсов СИ устройства,

151, 152, 153, 154 - внешние выходы разрядов устройства,

16 - выход сигнала CR разрешения работы в старшую тетраду.

Предлагаемое устройство осуществляется следующим образом.

В каждом двоичном разряде тетрады RS-триггер выполнен на основе первого 2 и второго 3 логических элементов И-НЕ и дополнительно введены третий 4, четвертый 5, пятый 6 и шестой 7 логические элементы И-НЕ, вход установки триггера в нулевое состояние и тактовый вход ТИ двоичного разряда, прямой Q и инверсный NQ выходы разряда.

Выходы первых элементов И-НЕ 2 каждого разряда являются прямыми Q выходами RS-триггера, а также являются внешними выходами устройства 151, 152, 153, 154 соответственно, выходы вторых элементов И-НЕ 3 каждого разряда являются инверсными NQ выходами RS-триггера, выход первого элемента И-НЕ 2 соединен с первым входом второго элемента И-НЕ 3, выход которого соединен со вторым входом первого элемента И-НЕ 2.

Первый вход первого элемента И-НЕ 2 соединен с выходом третьего элемента И-НЕ 4, первым входом пятого элемента И-НЕ 6 и первым входом четвертого элемента И-НЕ 5, третий вход которого соединен с третьим входом третьего элемента И-НЕ 4 и является тактовым входом ТИ двоичного разряда, выход шестого элемента И-НЕ 7 соединен со вторым входом пятого элемента И-НЕ 6 и вторым входом четвертого элемента И-НЕ 5, выход которого соединен со вторым входом второго элемента И-НЕ 3 и со вторым входом шестого элемента И-НЕ 7, первый вход которого соединен с первым входом третьего элемента И-НЕ 4 и является входом установки триггера в нулевое состояние.

Вход 12 установки устройства в нуль CLR соединен с входами установки всех триггеров в нулевое состояние.

Вход 13 разрешения работы устройства СЕ от предыдущей младшей тетрады счетчика соединен с четвертым входом элемента И 11 устройства и первым входом третьего элемента И-НЕ 10 устройства, второй вход которого соединен с входом 14 счетных импульсов СИ устройства, а выход третьего элемента И-НЕ 10 устройства соединен с тактовыми входами ТИ каждого двоичного разряда 11, 12, 13, 14.

Прямой Q1 выход 151 первого двоичного разряда 11 соединен с третьим входом шестого элемента И-НЕ 7 второго двоичного разряда 12, прямой Q2 выход 152 второго двоичного разряда 12 соединен с третьим входом шестого элемента И-НЕ 7 третьего двоичного разряда 13, прямой Q3 выход 153 третьего двоичного разряда 13 соединен с третьим входом шестого элемента И-НЕ 7 четвертого двоичного разряда 14.

Первый вход первого элемента И-НЕ 8 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, а второй вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, выход первого элемента И-НЕ 8 устройства соединен с третьим входом шестого элемента И-НЕ 7 первого двоичного разряда 11.

Первый вход второго элемента И-НЕ 9 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход второго элемента И-НЕ 9 устройства соединен с четвертым входом шестого элемента И-НЕ 7 второго двоичного разряда 12 и с четвертым входом шестого элемента И-НЕ 7 третьего двоичного разряда 13.

Первый вход элемента И 11 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход элемента И 11 является выходом 16 сигнала CR разрешения работы в старшую тетраду.

Принцип работы устройства состоит в следующем.

В предлагаемом способе счета импульсов каждую десятичную цифру от нуля до девяти одной декады представляют четырьмя двоичными разрядами. В таблице 1 приведены десятичные цифры и соответствующие им значения кода двоичных разрядов предлагаемого устройства и двоично-десятичных кодов. Выполнение счета импульсов производят путем добавления «1» к коду числа, хранящемуся в первом-четвертом триггерах Q1, Q2, Q3, Q4 тетрады, по счетным импульсам СИ.

Каждый двоичный разряд, на основе RS-триггера, выполнен как триггер с динамическим управлением (триггер управляемый фронтом) с прямым динамическим входом синхронизации (тактовый вход) и асинхронным инверсным входом установки в нулевое состояние. Динамический триггер реализует логику D-триггера с одним (разряды 11 и 14) или двумя (разряды 12 и 13) информационными входами.

Перед началом счета все триггеры устанавливают в нулевое состояние. Счетные импульсы СИ, при наличии единичного значения на внешнем входе разрешения работы СЕ=1, от предыдущей младшей тетрады, счетчика, инвертируют и подают на тактовые входы ТИ всех разрядов Q1, Q2, Q3, Q4. Триггеры срабатывают по фронту 1/0 входных счетных импульсов СИ.

По первому-девятому счетным импульсам производят добавление «1» к коду тетрады. При этом в младший разряд записывают код «1», при условии D1=not(Q1 and Q4)=1, т.е. при нулевом значении хотя бы на одном из прямых выходов соответственно первого триггера Q1 или четвертого триггера Q4, или кода «0», при условии D1=not(Q1 and Q3)=0, т.е. при единичных значениях на прямых выходах соответственно первого триггера Q1 и четвертого триггера Q4, а между остальными разрядами выполняют сдвиг в сторону старших разрядов - от первого к четвертому разряду.

После девятого счетного импульса СИ 9 на триггерах будет установлен код 1011, по которому формируют нулевое значение сигнала D9=not (Q4 and not Q3 and Q1)=0 установки триггеров в «0», т.е. при единичных значениях на прямых выходах соответственно четвертого Q4 и первого триггера Q1 и инверсном выходе третьего триггера not Q3,. По этому сигналу D9=0 по десятому счетному импульсу СИ 10 все триггеры Q1, Q2, Q3, Q4 тетрады устанавливают в «0».

Кроме того, после девятого счетного импульса СИ 9 на выходе декады формируют единичное значение сигнала CR=1 разрешения работы в старшую тетраду, с учетом сигнала на внешнем входе разрешения работы СЕ=1, от предыдущей младшей тетрады, счетчика: CR=Q4 and not Q3 and Q1 and CE=1.

Предлагаемое устройство счета импульсов работает следующим образом.

Перед началом счета на вход 12 начальной установки задают нулевое значение CLR=0. При этом на счетном входе 14 также установлено нулевое значение СИ=0. По этим сигналам в каждом двоичном разряде единичные значения будут установлены на выходах элементов И-НЕ 7, И-НЕ 4 и элементе И-НЕ 10 устройства, по которым установится в нулевое значение выход элемента И-НЕ 5 и по нему в единичное значение выход элемента И-НЕ 3 (инверсный выход триггера NQ). Так как на первом и втором входах элемента И-НЕ 2 будут установлены единичные значения, то на выходе И-НЕ 2 будет установлено нулевое значение (прямой выход триггера Q). Таким образом, в триггеры Q1, Q2, Q3, Q4 будет занесен код 0000.

При работе счетчика устанавливают единичное значение на входе 12 начальной установки CLR=1. Каждая тетрада счетчика работает при единичном значении на входе разрешения работы СЕ=1 от предыдущей младшей тетрады счетчика.

При коде на триггерах 0000 на выходах элементов И-НЕ 8 и И-НЕ 9 будут установлены единичные значения. При подаче единичного значения СИ=1 по счетному входу 14 на выходе элемента И-НЕ 10 будет установлено нулевое значение, по которому будут установлены единичные значения на выходах элементов И-НЕ 4 и И-НЕ 5 всех разрядов, а по ним нулевое значение на элементе И-НЕ 7 и единичное значение на элементе И-НЕ 6 первого разряда 11. Во втором-четвертом разрядах 12, 13, 14 на элементах И-НЕ 7 установится единичное значение, так как на их входы поступают нулевые сигналы с прямых выходов Q1, Q2, Q3, а элементах И-НЕ 6 нулевое значение

По фронту 1/0 первого счетного импульса СИ 1 установится единичное значение на выходе элемента И-НЕ 10 устройства и далее в первом разряде 11, нулевое значение на выходе элемента И-НЕ 4, единичное значение на элементе И-НЕ 2 и нулевое значение на выходе элемента И-НЕ 3, таким образом, первый триггер переключится в «1». Одновременно во втором-четвертых разрядах 12, 13, 14 установится нулевое значение на выходе элемента И-НЕ 5, единичное значение на элементе И-НЕ 3 и нулевое значение на выходе элемента И-НЕ 2, таким образом, второй-четвертый триггеры сохранят код «0» и, следовательно, в тетраде будет установлен следующий двоичный код 0001, соответствующий десятичной цифре «1».

По нулевому значению счетного импульса СИ=0 в первом разряде 11 сохранятся единичное значение на выходе элемента И-НЕ 6 и нулевое значение на выходе элемента И-НЕ 7. При этом во втором разряде 12 также установятся единичное значение на выходе элемента И-НЕ 6 и нулевое значение на выходе элемента И-НЕ 7, так как на его третий вход приходит единичное значение с выхода Q1 и установлены единичные значения на других входах. Поэтому далее по фронту 1/0 второго счетного импульса СИ 2 в первом разряде 11 сохранится значение Q1=1, а во втором разряде 12 установится значение Q2=1, и, следовательно, в тетраде установится код 0011, соответствующий десятичной цифре «2».

Аналогично по третьему СИ 3 и четвертому СИ 4 импульсам будут установлены коды 0111 и 1111, соответствующие десятичным цифрам «3» и «4».

Далее нулевое значение D1=0 будет установлено на выходе элемента И-НЕ 8, так как Q1=1 и Q4=1, и, соответственно, единичное значение на выходе элемента И-НЕ 7 и нулевое значение на выходе И-НЕ 6. Поэтому по фронту 1/0 пятого счетного импульса СИ 5 в первом триггере 11 выход переключится в нулевое значение Q1=0, а в других разрядах сохранятся единичные значения соответствующие двоичному коду тетрады 1110 - десятичная цифра «5».

По фронту 1/0 шестого счетного импульса СИ 6 в первом триггере 11 выход переключится в единичное значение Q1=1 так как установлено значение D1=1 на выходе элемента И-НЕ 8, а во второй-четвертый разряды будет загружен код из предыдущих разрядов и установится двоичный код тетрады 1101 - десятичная цифра «6».

Аналогично будет проведена запись в первом разряде 11 по значениям сигнала D1 и сдвиги во втором-четвертом разрядах 12, 13, 14 по седьмому-девятому импульсам СИ 7, СИ 8, СИ 9 и соответствующие двоичные коды 1010, 0101, 1011 - десятичные цифры «7», «8», «9».

По двоичному коду 1011 нулевые значения будут установлены на выходе элементов И-НЕ 8 и И-НЕ 9, а также единичное значение на выходе элемента И 11 и выходе 16 сигнала CR=1 разрешения работы в старшую декаду, при наличии единичного значения на входе разрешения работы СЕ=1 от предыдущей младшей тетрады счетчика.

По фронту 1/0 десятого счетного импульса СИ 10 в двоичных разрядах будет установлен код 0000 - десятичная цифра «0». Далее повторяется рассмотренный цикл счета импульсов.

Оценим быстродействие предлагаемого устройства и устройства-прототипа.

В устройстве-прототипе при установленном двоичном коде 1110 десятым счетным импульсом СИ 10 счетчик переключается в нулевое состояние 0000. При этом для RS-триггера третьего разряда время задержки переключения от фронта 0/1 десятого счетного импульса СИ 10 до фронта 1/0 прямого выхода Q14(tr3) равно:

где τ - время задержки одного логического элемента.

Максимальное время переходного процесса от фронта 1/0 десятого счетного импульса СИ 10 до установки единичного значения на входе элемента И 2 первого разряда равно:

В предлагаемом устройстве максимальное время задержки переключения от фронта 1/0 девятого счетного импульса СИ 9 до фронта 1/0 прямого выхода Q3 третьего разряда 13 равно:

Максимальное время переходного процесса для подготовки переключения триггера в «1» от фронта 0/1 счетного импульса СИ (для СИ 1, СИ 6, СИ 8) до установки единичного значения на выходе элемента И-НЕ 6 первого разряда 11 равно:

Максимальное время переходного процесса от фронта 1/0 счетного импульса СИ до фронта 0/1 или 1/0 сигнала CR на выходе 16 разрешения работы в старшую тетраду равно:

Таким образом, в предлагаемом устройстве повышение быстродействия достигается за счет меньшего количества элементов в цепях распространения сигналов.

Кроме того, в предлагаемом устройстве, в отличие от прототипа, сокращается объем аппаратных затрат, так как устройство-прототип счета импульсов выполнено на сорока пяти логических элементах И, ИЛИ, НЕ и суммарное число входов логических элементов равно 83 (при выполнении RS-триггеров на двух элементах И-НЕ), а предлагаемое устройство выполнено на двадцати семи однотипных элементах И-НЕ и одном элементе И и суммарное число входов логических элементов равно 73.

Вышеизложенные сведения позволяют сделать вывод, что в предлагаемом способе и устройстве счета импульсов изобретения выполняется счет импульсов в двоично-десятичном коде, устройство для счета импульсов обладает регулярностью узлов и связей, выполнено на однотипных элементах и соответствует заявляемому техническому результату - увеличение быстродействия, сокращение аппаратных затрат и повышение надежности за счет упрощения структуры устройства.

1. Способ счета импульсов, заключающийся в представлении каждой десятичной цифры от нуля до девяти одного разряда (декады) четырьмя двоичными разрядами, при этом выполнение счета импульсов от «0» до «9» производят путем добавления «1» к коду числа, хранящемуся в первом-четвертом триггерах Q1, Q2, Q3, Q4 тетрады, отличающийся тем, что десятичные цифры от нуля до девяти одной тетрады представляют двоичными кодами 0000, 0001, 0011, 0111, 1111, 1110, 1101, 1010, 0101 и 1011 соответственно, перед началом счета все триггеры устанавливают в нулевое состояние, подавая сигнал сброса CLR=0 на входы установки в «0» каждого триггера, затем на входе сброса устанавливают единичное значение CLR=1, счетные импульсы СИ, при наличии единичного значения на внешнем входе разрешения работы СЕ=1 от предыдущей младшей тетрады счетчика, инвертируют, формируют сигнал счета ТИ=not(СИ and СЕ), который поступает на тактовые входы всех триггеров Q1, Q2, Q3, Q4, добавление «1» к коду тетрады осуществляют по первому-девятому счетным импульсам СИ путем занесения в младший триггер Q1 кода «1», при условии D1=not(Q1 and Q4)=1, т.е. при нулевом значении хотя бы на одном из прямых выходов соответственно первого триггера Q1 или четвертого триггера Q4, или кода «0», при условии D1=not(Q1 and Q4)=0, т.е. при единичных значениях на прямых выходах соответственно первого триггера Q1 и четвертого триггера Q4, и выполняют сдвиг между разрядами тетрады на один разряд в сторону старших двоичных разрядов для второго Q2, третьего Q3 и четвертого Q4 триггеров, после девятого счетного импульса СИ 9 формируют нулевое значение сигнала установки триггеров в «0», при условии D9=not(Q4 and not Q3 and Q1)=0, т.е. при единичных значениях на прямых выходах соответственно четвертого Q4 и первого триггера Q1 и инверсном выходе третьего триггера not Q3, и единичное значение сигнала разрешения работы CR=1 в старшую тетраду, при этом CR=Q4 and not Q3 and Q1 and CE=1, по десятому счетному импульсу СИ 10 все триггеры Q1, Q2, Q3, Q4 тетрады устанавливают в «0».

2. Устройство счета импульсов, содержащее в каждой десятичной декаде четыре двоичных разряда 11, 12, 13, 14, логический элемент И 11, вход 14 счетных импульсов СИ устройства и вход 12 установки устройства в нуль CLR, причем каждый из двоичных разрядов выполнен на основе одного RS-триггера, отличающееся тем, что в него дополнительно введены первый 8, второй 9 и третий 10 логические элементы И-НЕ устройства, вход 13 разрешения работы устройства СЕ от предыдущей младшей тетрады счетчика, внешние выходы разрядов устройства 151, 152, 153, 154 и выход 16 сигнала разрешения работы CR в старшую тетраду, а в каждом двоичном разряде тетрады RS-триггера выполнены на основе первого 2 и второго 3 логических элементов И-НЕ и дополнительно введены третий 4, четвертый 5, пятый 6 и шестой 7 логические элементы И-НЕ и тактовый вход ТИ двоичного разряда, причем выходы первых элементов И-НЕ 2 каждого разряда являются прямыми Q выходами RS-триггера, а также являются внешними выходами устройства 151, 152, 153, 154 соответственно, выходы вторых элементов И-НЕ 3 каждого разряда являются инверсными NQ выходами RS-триггера, выход первого элемента И-НЕ 2 соединен с первым входом второго элемента И-НЕ 3, выход которого соединен со вторым входом первого элемента И-НЕ 2, первый вход которого соединен с выходом третьего элемента И-НЕ 4, первым входом пятого элемента И-НЕ 6 и первым входом четвертого элемента И-НЕ 5, третий вход которого соединен с третьим входом третьего элемента И-НЕ 4 и является тактовым входом ТИ двоичного разряда, выход шестого элемента И-НЕ 7 соединен со вторым входом пятого элемента И-НЕ 6 и вторым входом четвертого элемента И-НЕ 5, выход которого соединен со вторым входом второго элемента И-НЕ 3 и со вторым входом шестого элемента И-НЕ 7, первый вход которого соединен с первым входом третьего элемента И-НЕ 4 и является входом установки триггера в нулевое состояние, вход 12 установки устройства в нуль CLR соединен с входами установки всех триггеров в нулевое состояние, вход 13 разрешения работы устройства СЕ от предыдущей младшей тетрады счетчика соединен с четвертым входом элемента И 11 устройства и первым входом третьего элемента И-НЕ 10 устройства, второй вход которого соединен с входом 14 счетных импульсов СИ устройства, а выход третьего элемента И-НЕ 10 устройства соединен с тактовыми входами ТИ каждого двоичного разряда 11, 12, 13, 14, прямой Q1 выход 151 первого двоичного разряда 11 соединен с третьим входом шестого элемента И-НЕ 7 второго двоичного разряда 12, прямой Q2 выход 152 второго двоичного разряда 12 соединен с третьим входом шестого элемента И-НЕ 7 третьего двоичного разряда 13, прямой Q3 выход 153 третьего двоичного разряда 13 соединен с третьим входом шестого элемента И-НЕ 7 четвертого двоичного разряда 14, первый вход первого элемента И-НЕ 8 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, а второй вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, выход первого элемента И-НЕ 8 устройства соединен с третьим входом шестого элемента И-НЕ 7 первого двоичного разряда 11, первый вход второго элемента И-НЕ 9 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход второго элемента И-НЕ 9 устройства соединен с четвертым входом шестого элемента И-НЕ 7 второго двоичного разряда 12 и с четвертым входом шестого элемента И-НЕ 7 третьего двоичного разряда 13, первый вход элемента И 11 устройства соединен с прямым Q1 выходом 151 первого двоичного разряда 11, второй вход соединен с инверсным NQ3 выходом третьего двоичного разряда 13, третий вход соединен с прямым Q4 выходом 154 четвертого двоичного разряда 14, а выход элемента И 11 является выходом 16 сигнала разрешения работы CR в старшую тетраду.