Логический элемент «и—или—не» и «и-или»

Иллюстрации

Показать всеРеферат

260680

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства J¹

3ая влено 05.VI II.1968 (Гй 1262737/18-24) Кл, 21а>, 36/18 с присоединением заявки ¹

Приоритет

МПК Н 03k

УДК 681.325 65(088.8) Комитет по делам изаоретений и открытий при Совете Министров

СССР

Опубликовано 06.1.1970. Бюллетень ¹ 4

Дата опубликования описания 19Х.1970

Автор изобретения

В. А. Гринкевич

Заявитель

ЛОГИЧЕСКИЙ ЭЛГМЕНт «И — ИЛИ вЂ” HE» и «И вЂ” ИЛИ»

Предложенный логический элемент относится к элементам вычислигельной техники и может быть использован в устройствах цифровой автоматики и вычислительной техники, в частности в логических сетях электронных цифровых машин.

Известны транзисторные логические схемы, содержащие входной многоэмиттерный транзистор и выходной транзистор, включенный по схеме с общим эмиттером, либо более сложные схемы, содержащие, кроме того, транзистор, выполняющий роль парафазного усилительного каскада, и один или два последовательно включенных эмиттерных повторителя.

Однако известные схемы обладают рядом недостатков, основными пз которы.;. являются сильная зависимость задержки сигнала от числа входов «ИЛИ» при реализации логической функции «И вЂ” ИЛИ вЂ” НЕ» и отсутствие возможности совмещенной во времени и месте реализации логических функций «И вЂ” ИЛИ вЂ” НЕ» и «И вЂ” ИЛИ», что важно для построения логических сетей быстродействующих вычислительных машин.

Предложенный логический элемент отличается тем, что коллектор усил тельного транзистора через инерционный диод |подключен к базе дополнительного транзистора, включенного по схеме с общим эмиттером, коллектор которого соединен с выходом -лемента. Это позволяет одновременно реализовать функции

«И — ИЛИ вЂ” НЕ» и «И вЂ” ИЛИ».

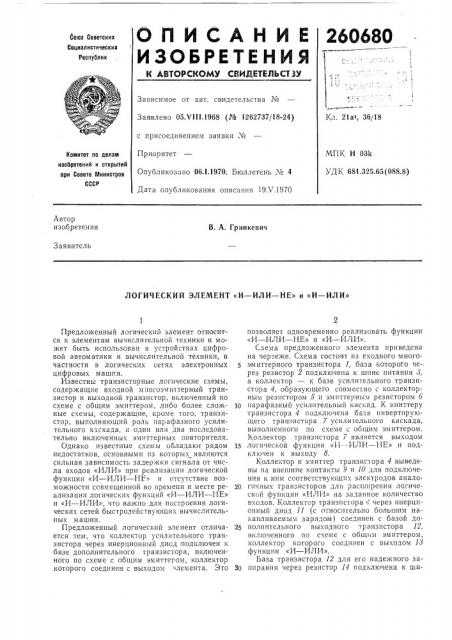

Схема предложенного элемента приведена на чертеже. Схема состоит из входного многоэмиттерного транзистора 1, база которого через резистор 2 подключена к шине питания 3, а коллектор — к базе усилительного транзистора 4, образующего совместно с коллекторным резистором 5 и эмиттерным резистором 6

1О парафазный усилительный каскад, К эмиттеру транзистора 4 подключена база инвертпрующего транзистора 7 усилительного каскада, выполненного по схеме с общим эмиттером.

Коллектор транзистора 7 является выходом

15 логической функции «11--ИЛИ вЂ” НЕ» и подключен к выходу 8.

Коллектор и эмиттер транзистора 4 выведены на внешние контакты 9 и 10 для подключения к ним соответствующих электродов анало20 гцчных транзисторов для расширения логической функции «ИЛИ» на заданное количество входов. Коллектор транзистора . через инерционный диод 11 (с относительно большим накапливаемым зарядом) соединен с базой до25 полнительного выходного транзистора 12, вкл|оченного по схеме с общим эмиттером, коллектор которого соединен с выходом 13 функции «И вЂ” ИЛИ».

База транзистора 12 для его надежного за30 пирания через резистор 14 подключена к ши260680

Предмет изобретения

Составитель Ю. H. Колотов

Редактор T. Зенбицкая Техред А. А. Камышиикова Корректор Н. С. Сударенкова

Заказ 1116/12 Тираж ЬОО Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 не нулевого потенциала. Коллекторы транзисторов 7 и 12 могут быть подключены к шине питания 8 через резисторы 15 и 1б.

При низком уровне входного сигнала, поданного хотя бы на один из эмиттеров транзистора 1, транзистор 4 и инвертирующий транзистор 7 заперты. При этом на выходе 8 устанавливается высокий уровень напряжения. На коллекторе транзистора 4 устанавливается уровень напряжения, равный сумме падения напряжений на переходе база — эмиттер транзистора 12 и диода 11, от тока, заданного резистором 5. На коллекторе открытого и насыщенного транзистора !2, а следовательно, и на выходе 18 устанавливается низкий уровень н а и р яж ения.

Если на всех входах схемы скачком устанавливается высокий уровень напряжения, fo транзистор 4 начинает открываться. При этом напряжение на его коллекторе повышается под действием тока, протекающего от коллектора к эмиттеру. Коллекторный ток транзистора 4 слагается из двух составляющих: тока, протекающего от шины питания 3 через резистор 5, и тока рассасывания накопленных зарядов в ичерционном диоде 11 и транзисторе 12.

Вторая составляющая тока, представляющая собой обратный базовый ток насыщенного транзистора 12, оказывается больше .первой, что обуславливает быстрое включение транзистора 7 и выключение транзистора 12.

После завершения процесса включения транзистора 7 и выключения транзистора 12 на коллекторе транзистора 4 устанавливается уровень напряжения, равный сумме падения напряжения на промежутке коллектор — эмиттер насыщенного транзистора 4 и перехода база — эмиттер транзнстсра 7.

10 Таким образом, перепад напряжения на коллекторе транзистора 4 для кремниевых планарных транзисторов и интегральных схем составляет величину около 0,4 в, что приблизительно в 10 раз меньше аналогичного перепада

lS напряжения известных схем.

Логический элемент «И — ИЛИ вЂ” НЕ» и

20 «И — ИЛИ», содержащий входной многоэмиттерный транзистор, усилительный транзистор с парафазным выходом, эмитчер которого соединен с базой инвертирующегс транзистора, отличающийся тем, что, с целью одновремен25 ной реализации функций «И вЂ” ИЛИ вЂ” НЕ» и

«И — ИЛИ», коллектор усилительного транзистора через инерционный диод подключен к базе дополнительного транзистора, включенного по схеме с общим эмиттерсм, коллектор

ЗО которого соединен с выходом элемента.