Высокочастотный фазовращатель на моп-транзисторах

Иллюстрации

Показать всеИзобретение относится к областям радиотехники и связи. Высокочастотный фазовращатель выполнен на основе КМОП-технологии, при этом усилители с переменным коэффициентом усиления построены на основе модифицированных ячеек Гильберта, а аналоговый дифференциальный квадратурный сумматор подключен к квадратурному полифазному фильтру напрямую. Каждая модифицированная ячейка Гильберта состоит из десяти МОП-транзисторов. При этом затворы первого и четвертого МОП-транзисторов являются высокочастотными входами, истоки первого и второго МОП-транзисторов соединены со стоком девятого МОП-транзистора, истоки третьего и четвертого МОП-транзисторов соединены со стоком десятого МОП-транзистора, исток девятого и десятого МОП-транзисторов подключен к общему узлу, затворы девятого и десятого МОП-транзисторов подключены к первому выходу источника напряжений смещения, затворы второго и третьего МОП-транзисторов подключены ко второму выходу источника напряжений смещения, стоки первого и третьего МОП-транзисторов подключены к узлу, к которому подключены истоки пятого и шестого МОП-транзисторов, стоки второго и четвертого МОП-транзисторов подключены к узлу, к которому подключены истоки седьмого и восьмого МОП-транзисторов, затворы пятого и восьмого МОП-транзисторов и затворы шестого и седьмого МОП-транзисторов представляют собой управляющие дифференциальные входы соответственно, стоки пятого и седьмого МОП-транзисторов и стоки шестого и восьмого МОП-транзисторов подключены к двум входам цепи нагрузки соответственно Высокочастотный фазовращатель на МОП-транзисторах с конструкцией согласно изобретению обладает уменьшенной ошибкой установки фазы и потребляемой мощностью, а также более низкой себестоимостью. 3 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в области радиоэлектроники.

Известен «Перестраиваемый фазовращатель-аттенюатор» [US патент №8724739]. Фазовращатель состоит из полифазного фильтра, цифроаналогового преобразователя, аттенюатора с переменным коэффициентом ослабления и аналогового квадратурного сумматора, построенного на основе усилителей с переменным коэффициентом усиления в виде ячеек Гильберта и цепи нагрузки. Изменение коэффициента передачи усилителя осуществляется путем параллельного подключения нескольких усиливающих каскадов. Недостатком фазовращателя является увеличение ошибки установки фазы при изменении коэффициентов передачи усилителей из-за увеличения входной емкости сумматора, на которую нагружен полифазный фильтр, формирующий квадратурные дифференциальные сигналы.

Известен патент «Фазоздвигающая схема на биполярных транзисторах для использования в передающих устройствах, состоящая из двух блоков, через которые протекают токи, представляющие произведение синфазных компонент и весовых коэффициентов, соответственно» [FR патент №2984638]. Фазовращатель состоит из двух усилителей с переменным коэффициентом усиления в виде ячеек Гильберта, цепей нагрузки и преобразователей частоты. Фазовый сдвиг осуществляется за счет перемножения высокочастотного сигнала с квадратурными опорными сигналами и переносом на промежуточную частоту. Недостатком фазовращателя является возможность реализации только с переносом частоты несущей, при этом ошибка установки фазы зависит от амплитудно-фазового дисбаланса опорного колебания, что требует синтезатора частот низким уровнем фазовых шумов.

Известен «Активный фазовращатель», выбранный за прототип [RU патент №2510980]. Фазовращатель построен на биполярных транзисторах на основе SiGe-технологии и включает квадратурный полифазный фильтр, повторители напряжения, аналоговый квадратурный сумматор, состоящий из двух усилителей с переменным коэффициентом усиления в виде ячеек Гильберта и цепи нагрузки, источник питания, цифроаналоговый преобразователь, источник напряжения смещения, блок преобразователя дифференциального сигнала в однополярный. Эмиттерные повторители включены между выходами полифазного фильтра и входами сумматора для предотвращения влияния входного импеданса аналогового дифференциального сумматора на характеристики полифазного фильтра. Использование повторителей напряжения увеличивает потребляемую мощность фазовращателя и может вызывать паразитную автогенерацию, использование SiGe-технологии увеличивает себестоимость устройства, что является недостатками прототипа.

Задачей изобретения является снижение себестоимости фазовращателя, уменьшение ошибки установки фазы и потребляемой мощности.

Для решения поставленной задачи предложен высокочастотный фазовращатель на МОП-транзисторах, который включает квадратурный полифазный фильтр, аналоговый квадратурный дифференциальный сумматор, состоящий из двух усилителей с переменным коэффициентом усиления в виде модифицированных ячейках Гильберта, дифференциальные выходы которых подключены к цепи нагрузки, включенной между выходами аналогового сумматора и шины питания и цепи нагрузки, блок преобразователя дифференциального сигнала в однополярный с согласующей цепью, входы преобразователя подключены к выходам аналогового сумматора. Фазовращатель выполнен на основе КМОП-технологии, при этом аналоговый квадратурный дифференциальный сумматор подключен к полифазному фильтру напрямую. Каждая модифицированная ячейка Гильберта состоит из десяти МОП-транзисторов. Затворы первого и четвертого МОП-транзисторов являются высокочастотными входами модифицированной ячейки Гильберта. Истоки первого и второго МОП-транзисторов соединены со стоком девятого МОП-транзистора. Истоки третьего и четвертого МОП-транзистора соединены со стоком десятого МОП-транзистора. Истоки девятого и десятого МОП-транзисторов подключены к общему узлу. Затворы девятого и десятого МОП-транзисторов подключены к первому выходу источника напряжений смещения. Затворы второго и третьего МОП-транзисторов подключены ко второму выходу источника напряжений смещения. Стоки первого и третьего МОП-транзисторов подключены к узлу, к которому подключены истоки пятого и шестого МОП-транзисторов. Стоки второго и четвертого МОП-транзисторов подключены к узлу, к которому подключены истоки седьмого и восьмого МОП-транзисторов. Затворы пятого и восьмого МОП-транзисторов и затворы шестого и седьмого МОП-транзисторов представляют собой управляющие дифференциальные входы соответственно. Стоки пятого и седьмого МОП-транзисторов и стоки шестого и восьмого МОП-транзисторов подключены к двум дифференциальным входам цепи нагрузки соответственно.

Квадратурный полифазный фильтр преобразует дифференциальный сигнал на входах в два квадратурных дифференциальных сигнала на выходах. Каждый из квадратурных дифференциальных сигналов поступает на высокочастотные входы усилителя с переменным коэффициентом усиления и передается на выходы с коэффициентом передачи, который задается аналоговым дифференциальным управляющим сигналом на управляющих входах усилителя. Аналоговые дифференциальные управляющие сигналы поступают с выходов цифроаналогового преобразователя, который преобразует цифровой управляющий сигнал на его входах в два аналоговых дифференциальных управляющих сигнала на его выходах. Дифференциальные выходы усилителей с переменным коэффициентом усиления подключены к дифференциальным входам цепи нагрузки и к дифференциальным входам блока преобразователя дифференциального сигнала в однополярный. В цепи нагрузки происходит сложение квадратурных дифференциальных сигналов с весовым коэффициентами. Результирующий сигнал преобразуется к небалансному виду блоком преобразователя дифференциального сигнала в однополярный.

Модифицированная ячейка Гильберта обеспечивает двукратное уменьшение входной емкости по сравнению с классической ячейкой Гильберта при сравнимом коэффициенте усиления. Усилители в виде модифицированной ячейки Гильберта позволяют уменьшить влияние входного импеданса сумматора на характеристики полифазного фильтра, что приводит к повышению точности установки фазы за счет уменьшения влияния входного импеданса сумматора на характеристики полифазного фильтра и позволяет подключить полифазный фильтр напрямую ко входу сумматора без использования повторителей напряжения. Исключение повторителей напряжения позволяет снизить потребляемую мощность. Снижение себестоимости фазовращателя достигается за счет использования КМОП-технологии.

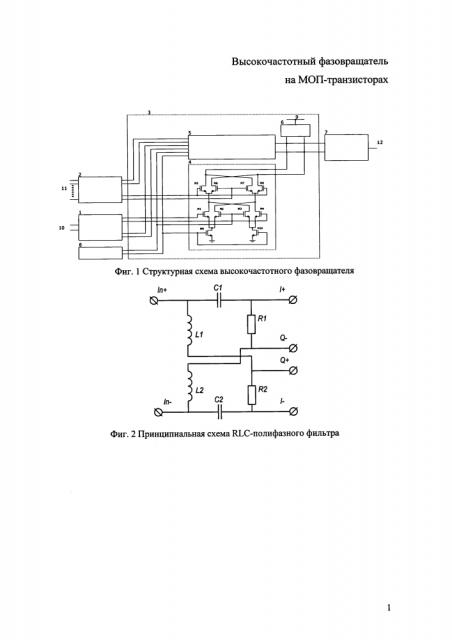

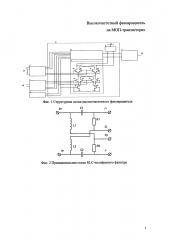

Предлагаемое изобретение иллюстрируется графическими материалами, представленными на фиг. 1, 2 и 3:

на фиг. 1 изображена структурная схема высокочастотного фазовращателя;

на фиг. 2 изображена принципиальная схема RLC-полифазного фильтра;

на фиг. 3 приведена зависимость фаз RLC-полифазного фильтра от емкости нагрузки.

Высокочастотный фазовращатель включает: квадратурный полифазный фильтр 1; цифроаналоговый преобразователь 2; аналоговый квадратурный дифференциальный сумматор 3, состоящий из двух усилителей с переменным коэффициентом усиления построенных на основе модифицированной ячейки Гильберта, 4 и 5, и цепи нагрузки 6; блок преобразователя дифференциального сигнала в однополярный 7; источник напряжений смещения 8; шину питания 9; высокочастотный дифференциальный вход 10 фазовращателя; вход цифровых управляющих сигналов 11 фазовращателя; высокочастотный выход 12 фазовращателя.

К выходам квадратурного полифазного фильтра подключены высокочастотные входы аналогового квадратурного сумматора 3, который состоит из двух одинаковых усилителей с переменным коэффициентом усиления, построенных на основе модифицированной ячейки Гильберта, 4 и 5. Высокочастотные дифференциальные входы усилителя с переменным коэффициентом усиления подключены к одной из пар дифференциальных выходов квадратурного полифазного фильтра 1. Управляющие дифференциальные входы усилителя с переменным коэффициентом усиления подключены к одной из пар дифференциальных выходов цифроаналогового преобразователя 2. Входы цифроаналогового преобразователя являются входами цифровых управляющих сигналов 11 фазовращателя. Дифференциальные выходы усилителей с переменным коэффициентом усиления подключены к дифференциальным входам цепи нагрузки 6, которая также обеспечивает питание усилителей с переменным коэффициентом усиления от шины питания 9 и к дифференциальным входам блока преобразователя дифференциального сигнала в однополярный 7, выходы источника напряжений смещения 8 подключены ко входам напряжений смещения усилителей с переменным коэффициентом усиления. Выходом фазовращателя 12 является выход блока преобразователя дифференциального сигнала в однополярный.

Каждая модифицированная ячейка Гильберта состоит из десяти МОП-транзисторов. При этом затворы первого и четвертого МОП-транзисторов являются высокочастотными входами модифицированной ячейки Гильберта. Истоки первого и второго МОП-транзисторов соединены со стоком девятого МОП-транзистора. Истоки третьего и четвертого МОП-транзисторов соединены со стоком десятого МОП-транзистора. Истоки девятого и десятого МОП-транзисторов подключен к общему узлу. Затворы девятого и десятого МОП-транзисторов подключены к первому выходу источника напряжений смещения, затворы второго и третьего МОП-транзисторов подключены ко второму выходу источника напряжений смещения. Стоки первого и третьего МОП-транзисторов подключены к узлу, к которому подключены истоки пятого и шестого МОП-транзисторов. Стоки второго и четвертого МОП-транзисторов подключены к узлу, к которому подключены истоки седьмого и восьмого МОП-транзисторов. Затворы пятого и восьмого МОП-транзисторов и затворы шестого и седьмого МОП-транзисторов представляют собой управляющие дифференциальные входы соответственно. Стоки пятого и седьмого МОП-транзисторов и стоки шестого и восьмого МОП-транзисторов подключены к двум входам цепи нагрузки соответственно.

Принцип работы высокочастотного фазовращателя (фиг. 1, фиг. 2, фиг. 3) заключается в следующем.

Входной дифференциальный сигнал, проходя через квадратурный полифазный фильтр 1, преобразуется в два квадратурных дифференциальных сигнала на выходах полифазного фильтра, которые поступают на вход аналогового квадратурного сумматора 3, который осуществляет сложение квадратурных дифференциальных сигналов с весовыми коэффициентами, заданными двумя парами дифференциальных управляющих сигналов на его входах. Пара аналоговых дифференциальных управляющих сигналов формируется при помощи цифроаналогового преобразователя 2, который преобразует цифровой управляющий сигнал на его входах в дифференциальные аналоговые управляющие сигналы. Блок преобразователя дифференциального сигнала в однополярный 7 преобразует балансный сигнал в однополярный и осуществляет согласование выходного сигнала с нагрузкой. Сложение квадратурных дифференциальных сигналов в аналоговом квадратурном сумматоре осуществляется следующим образом. Квадратурные дифференциальные сигналы поступают на усилители с переменным коэффициентом усиления 4 и 5, коэффициент усиления которых зависит от входных управляющих сигналов. Сигналы с выходов усилителей с переменным коэффициентом усиления 4 и 5 складываются в цепи нагрузки.

Усилитель с переменным коэффициентом усиления в виде модифицированной ячейки Гильберта работает следующим образом. Входной сигнал, поступая на затворы первого и четвертого МОП-транзисторов, приводит к противофазному изменению токов стоков этих транзисторов. Это в свою очередь приводит к изменению токов стоков второго и третьего МОП-транзисторов. Причем изменение тока первого МОП-транзистора синфазно с изменением тока третьего МОП-транзистора, а изменение тока второго МОП-транзистора синфазно с изменением тока четвертого МОП-транзистора, так как суммарный ток первого и второго транзисторов, а также третьего и четвертого МОП-транзисторов не зависит от входного сигнала и определяется токами стоков девятого и десятого МОП-транзисторов соответственно. Далее ток первого МОП-транзистора складываются в фазе с током третьего МОП-транзистора, а ток второго МОП-транзистора складывается в фазе с током четвертого МОП-транзистора. Благодаря этому ток транзисторов удваивается, что позволяет в два раза уменьшить размеры транзисторов с первого по четвертый и, следовательно, в два раза уменьшить входную емкость сумматора, что приводит к уменьшению амплитудно-фазового дисбаланса на выходе квадратурного полифазного фильтра и, как следствие, уменьшению ошибки установки фазы. Цепь нагрузки обеспечивает сложение сигналов и питание транзисторов от шины питания 9.

На фиг. 2 представлен RLC-полифазный фильтр, а на фиг. 3 представлены результаты моделирования зависимости дисбаланса фаз от нагрузочной емкости RLC-квадратурного полифазного фильтра. Как видно из приведенной зависимости, уменьшение нагрузочной емкости позволяет уменьшить дисбаланс фаз. Таким образом, снижение входной емкости сумматора позволяет повысить точность установки фазы.

Построение фазовращателя на МОП-транзисторах на основе КМОП-технологии в отличие от прототипа, построенного на биполярных транзисторах на основе SiGe-технологии, позволяет снизить себестоимость фазовращателя, а также уменьшить ошибку установки фазы и потребляемой мощности фазовращателя.

Высокочастотный фазовращатель на МОП-транзисторах, включающий квадратурный полифазный фильтр, цифроаналоговый преобразователь, аналоговый дифференциальный квадратурный сумматор, состоящий из цепи нагрузки и двух усилителей с переменным коэффициентом усиления в виде ячеек Гильберта, дифференциальные выходы которых подключены к цепи нагрузки, включенной между выходами аналогового сумматора и шины питания, блок преобразователя дифференциального сигнала в однополярный с согласующей цепью, входы преобразователя подключены к выходам аналогового сумматора, отличающийся тем, что аналоговый сумматор подключен к полифазному фильтру, усилители построены в виде модифицированных ячеек Гильберта, каждая из которых построена на МОП-транзисторах, при этом затворы первого и четвертого МОП-транзисторов являются высокочастотными входами, истоки первого и второго МОП-транзисторов соединены со стоком девятого МОП-транзистора, истоки третьего и четвертого МОП-транзисторов соединены со стоком десятого МОП-транзистора, исток девятого и десятого МОП-транзисторов подключен к общему узлу, затворы девятого и десятого МОП-транзисторов подключены к первому выходу источника напряжений смещения, затворы второго и третьего МОП-транзисторов подключены ко второму выходу источника напряжений смещения, стоки первого и третьего МОП-транзисторов подключены к узлу, к которому подключены истоки пятого и шестого МОП-транзисторов, стоки второго и четвертого МОП-транзисторов подключены к узлу, к которому подключены истоки седьмого и восьмого МОП-транзисторов, затворы пятого и восьмого МОП-транзисторов и затворы шестого и седьмого МОП-транзисторов представляют собой управляющие дифференциальные входы соответственно, стоки пятого и седьмого МОП-транзисторов и стоки шестого и восьмого МОП-транзисторов подключены к двум входам цепи нагрузки соответственно.