Способ кодирования изображения, устройство кодирования изображения, способ декодирования изображения и устройство декодирования изображения

Иллюстрации

Показать всеИзобретение относится к технологиям кодирования и декодирования изображений. Техническим результатом является повышение эффективности кодирования/декодирования видео за счет арифметического кодирования/декодирования информации последней позиции. Предложен способ кодирования для кодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть кодирован. Способ содержит этап, на котором осуществляют преобразование в двоичную форму информации последней позиции для формирования двоичного сигнала, который включает в себя префиксную часть сигнала, имеющую длину, меньшую или равную предопределенной максимальной длине, и не включает в себя суффиксную часть сигнала или двоичного сигнала, который включает в себя префиксную часть сигнала, имеющую предопределенную максимальную длину, и суффиксную часть сигнала. Способ содержит этап арифметического кодирования каждого из двоичных символов, включенных в префиксную часть сигнала, с использованием контекста, переключаемого среди множества контекстов в соответствии с битовой позицией двоичного символа. 7 н. и 4 з.п. ф-лы, 50 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение имеет отношение к методике кодирования изображения и методике декодирования изображения для арифметического кодирования или арифметического декодирования.

УРОВЕНЬ ТЕХНИКИ

Растет количество приложений для предоставления услуг через Интернет (например, услуг видеоконференций, цифрового видеовещания и передачи видео по запросу, включающих в себя потоковую передачу видео). Эти приложения полагаются на передачу видеоданных. Когда приложения передают видеоданные, большинство видеоданных передается через традиционный канал передачи, имеющий ограниченную пропускную способность. Кроме того, когда приложения записывают видеоданные, большинство видеоданных записывается на традиционном носителе записи, имеющем ограниченную емкость. Чтобы передать видеоданные через традиционный канал передачи или записать видеоданные на традиционном носителе записи, необходимо сжать или уменьшить объем видеоданных.

С этой целью было разработано много стандартов кодирования видео для сжатия видеоданных. Этими стандартами кодирования видео являются, например, стандарты ITU-T, обозначенные как H.26x, и стандарты ISO/IEC, обозначенные как MPEG-x. В настоящий момент последним и наиболее усовершенствованным стандартом кодирования видео является стандарт, обозначенный как H.264/MPEG-4 AVC (см. не патентную литературу (NPL) 1 и не патентную литературу (NPL) 2).

Подход к кодированию, лежащий в основе большинства этих стандартов кодирования видео, основан на кодировании с предсказанием, которое включает в себя следующие основные этапы (a)-(d): (a) разделить каждый видеокадр на блоки, каждый из которых имеет пиксели, для сжатия данных видеокадра блок за блоком, (b) предсказать каждый блок на основе ранее кодированных видеоданных, чтобы идентифицировать временную и пространственную избыточность, (c) вычесть предсказанные данные из видеоданных, чтобы удалить идентифицированную избыточность, (d) сжать оставшиеся данные (остаточные блоки) посредством преобразования Фурье, квантования и энтропийного кодирования.

Что касается этапа (a), текущий стандарт кодирования видео обеспечивает различные режимы предсказания в зависимости от макроблока, который должен быть предсказан. В соответствии с большинством стандартов кодирования видео оценка движения и компенсация движения используются для предсказания видеоданных на основе ранее кодированного и декодированного кадра (межкадровое (inter) предсказание). В качестве альтернативы, данные блока могут быть экстраполированы из смежного блока того же самого кадра (внутрикадровое (intra) предсказание).

На этапе (d) квантованные коэффициенты, включенные в текущий блок, который должен быть кодирован, сканируются в предопределенном порядке (порядке сканирования). Затем кодируется информация (SignificantFlag), указывающая, являются ли сканированные коэффициенты нулевыми коэффициентами или ненулевыми коэффициентами (например, двоичная информация (символ), указывающая ненулевой коэффициент как 1 и нулевой коэффициент как 0).

Кроме того, информация, указывающая позицию последнего ненулевого коэффициента в порядке сканирования (информация последней позиции), преобразовывается в двоичную форму, кодируется посредством контекстно-адаптивного двоичного арифметического кодирования и декодируется посредством контекстно-адаптивного двоичного арифметического декодирования.

СПИСОК ЛИТЕРАТУРЫ

НЕПАТЕНТНАЯ ЛИТЕРАТУРА

[NPL 1] ITU-T Recommendation H.264 "Advanced video coding for generic audiovisual services", March 2010.

[NPL 2] JCT-VC "WD4: Working Draft 4 of High-Efficiency Video Coding", JCTVC-F803, July 2011.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Однако в традиционной методике надлежащее переключение среди контекстов является трудным при контекстно-адаптивном двоичном арифметическом кодировании и контекстно-адаптивном двоичном арифметическом декодировании информации последней позиции. Например, когда один и тот же контекст используется для двоичных символов, которые существенно отличаются по вероятности появления, точность предсказания вероятности появления символа уменьшается, и, таким образом, также уменьшается эффективность кодирования.

С этой целью один неограничивающий и иллюстративный вариант осуществления обеспечивает способ кодирования изображения и способ декодирования изображения для арифметического кодирования и арифметического декодирования информации последней позиции с использованием контекста, который надлежащим образом переключен среди множества контекстов.

РЕШЕНИЕ ПРОБЛЕМЫ

Способ кодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ кодирования изображения для кодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть кодирован, способ кодирования изображения содержит этапы, на которых: преобразовывают в двоичную форму информацию последней позиции для формирования (i) двоичного сигнала, который включает в себя первый сигнал, имеющий длину, меньшую или равную предопределенной максимальной длине, и не включает в себя второй сигнал или (ii) двоичного сигнала, который включает в себя первый сигнал, имеющий предопределенную максимальную длину, и второй сигнал; выполняют первое кодирование для арифметического кодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа; и выполняют второе кодирование для арифметического кодирования второго сигнала с использованием фиксированной вероятности, когда двоичный сигнал включает в себя второй сигнал, причем при первом кодировании двоичный символ в последней битовой позиции первого сигнала арифметически кодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Следует отметить, что этот общий аспект может быть реализован с использованием системы, устройства, интегральной схемы, компьютерной программы или считываемого компьютером носителя записи, такого как компакт-диск (CD-ROM), или любой комбинации систем, устройств, интегральных схем, компьютерных программ или считываемых компьютером носителей записи.

ПОЛЕЗНЫЕ ЭФФЕКТЫ ИЗОБРЕТЕНИЯ

С помощью способа кодирования изображения в соответствии с аспектом настоящего изобретения возможно арифметически кодировать информацию последней позиции с использованием контекста, который надлежащим образом переключен среди множества контекстов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - блок-схема, показывающая пример конфигурации устройства декодирования изображения в соответствии с основополагающим знанием.

Фиг.2 - блок-схема последовательности операций, показывающая пример способа декодирования изображения в соответствии с основополагающим знанием.

Фиг.3A - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 4×4.

Фиг.3B - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 8×8.

Фиг.3C - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 16×16.

Фиг 3D - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 32×32.

Фиг.4 - блок-схема последовательности операций, показывающая контекстно-адаптивное двоичное арифметическое декодирование.

Фиг.5 - блок-схема последовательности операций, показывающая обходное декодирование.

Фиг.6 - блок-схема последовательности операций, показывающая нормализацию.

Фиг.7 - блок-схема, показывающая функциональную конфигурацию устройства декодирования изображения в соответствии с вариантом осуществления 1.

Фиг.8A - блок-схема последовательности операций, показывающая пример операций обработки устройства декодирования изображения в соответствии с вариантом осуществления 1.

Фиг.8B - блок-схема последовательности операций, показывающая другой пример операций обработки устройства декодирования изображения в соответствии с вариантом осуществления 1.

Фиг.9A - блок-схема последовательности операций, показывающая пример операций обработки второго блока декодирования в соответствии с вариантом осуществления 1.

Фиг.9B - схема, показывающая пример соотношения между размером блока и максимальной длиной префиксной части в соответствии с вариантом осуществления 1.

Фиг.9C - схема, показывающая другой пример соотношения между размером блока и максимальной длиной префиксной части в соответствии с вариантом осуществления 1.

Фиг.9D - схема, показывающая пример соотношения между размером блока и параметром Райса в соответствии с вариантом осуществления 1.

Фиг.9E - схема, показывающая другой пример соотношения между размером блока и параметром Райса в соответствии с вариантом осуществления 1.

Фиг.10A - блок-схема последовательности операций, показывающая пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10B - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10C - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10D - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

Фиг.11A - схема для описания соотношения между битовыми позициями и контекстами в соответствии с вариантом осуществления 1.

Фиг.11B - схема для описания соотношения между битовыми позициями и контекстами в соответствии со сравнительным примером.

Фиг.12 - блок-схема, показывающая пример конфигурации устройства декодирования изображения в соответствии с изменением варианта осуществления 1.

Фиг.13 - блок-схема, показывающая функциональную конфигурацию устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.14A - блок-схема последовательности операций, показывающая пример операций обработки устройства кодирования изображения в соответствии с вариантом осуществления 2.

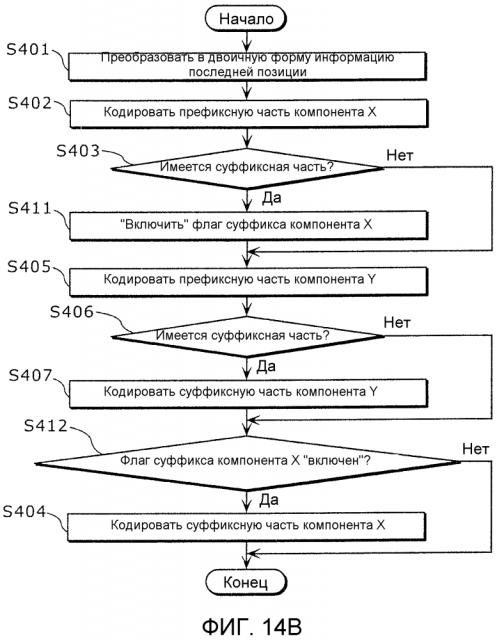

Фиг.14B - блок-схема последовательности операций, показывающая другой пример операций обработки устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.15 - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 16x16.

Фиг.16 - блок-схема, показывающая пример конфигурации устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.17 показывает общую конфигурацию системы обеспечения информационного содержания для реализации службы распространения информационного содержания.

Фиг.18 показывает общую конфигурацию системы цифрового вещания.

Фиг.19 показывает блок-схему, иллюстрирующую пример конфигурации телевизора.

Фиг.20 показывает блок-схему, иллюстрирующую пример конфигурации блока воспроизведения/записи информации, который считывает информацию с носителя записи и записывает информацию на носитель записи, являющийся оптическим диском.

Фиг.21 показывает пример конфигурации носителя записи, являющегося оптическим диском.

Фиг.22A показывает пример сотового телефона.

Фиг.22B - блок-схема, показывающая пример конфигурации сотового телефона.

Фиг.23 иллюстрирует структуру мультиплексированных данных.

Фиг.24 схематично показывает, каким образом каждый поток мультиплексирован в мультиплексированных данных.

Фиг.25 более подробно показывает, каким образом видеопоток сохранен в потоке пакетов PES.

Фиг.26 показывает структуру пакетов TS и пакетов источника в мультиплексированных данных.

Фиг.27 показывает структуру данных таблицы PMT.

Фиг.28 показывает внутреннюю структуру информации мультиплексированных данных.

Фиг.29 показывает внутреннюю структуру информации атрибутов потока.

Фиг.30 показывает этапы для идентификации видеоданных.

Фиг.31 показывает пример конфигурации интегральной схемы для реализации способа кодирования движущегося изображения и способа декодирования движущегося изображения в соответствии с каждым из вариантов осуществления.

Фиг.32 показывает конфигурацию для переключения между задающими частотами.

Фиг.33 показывает этапы для идентификации видеоданных и переключения между задающими частотами.

Фиг.34 показывает пример таблицы поиска, в которой стандарты видеоданных соответствуют задающим частотам.

Фиг.35A - схема, показывающая пример конфигурации для совместного использования модуля блока обработки сигналов.

Фиг.35B - схема, показывающая другой пример конфигурации для совместного использования модуля блока обработки сигналов.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

(Основополагающие знания, формирующие базис настоящего изобретения)

Авторы изобретения изложили следующий вопрос относительно арифметического кодирования и арифметического декодирования информации последней позиции в разделе "Уровень техники".

Следует отметить, что в последующем описании информация последней позиции указывает позицию по горизонтали и позицию по вертикали последнего ненулевого коэффициента в предопределенном порядке в текущем блоке. При этом информация последней позиции включает в себя горизонтальную компоненту (именуемую в дальнейшем "компонентой X") и вертикальную компоненту (именуемую в дальнейшем "компонентой Y"). Компонента X указывает позицию по горизонтали в текущем блоке. Компонента Y указывает позицию по вертикали в текущем блоке.

Фиг.1 является блок-схемой, показывающей пример конфигурации устройства 1000 декодирования изображения в соответствии с основополагающим знанием. Фиг.2 является блок-схемой последовательности операций, показывающей пример способа декодирования изображения в соответствии с основополагающим знанием. Как показано, на Фиг.1, устройство 1000 декодирования изображения включает в себя первый блок 1001 декодирования, второй блок 1002 декодирования, блок 1003 управления декодированием и блок 1004 восстановления.

Устройство 1000 декодирования изображения получает битовый поток (BS), который включает в себя информацию последней позиции. Затем устройство 1000 декодирования изображения вводит битовый поток BS в первый блок 1001 декодирования, второй блок 1002 декодирования и блок 1003 управления декодированием.

Блок 1003 управления декодированием выполняет определение, является ли каждый сигнал в полученном битовом потоке BS компонентой X или компонентой Y информации последней позиции.

Первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты X информации последней позиции, включенной в битовый поток BS (этап S1001). Более определенно, первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты X посредством контекстно-адаптивного двоичного арифметического декодирования. При этом префиксная часть является частью двоичного сигнала компоненты X или компоненты Y, которая кодирована посредством контекстно-адаптивного двоичного арифметического кодирования.

Затем первый блок 1001 декодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть (этап S1002). Суффиксная часть является частью двоичного сигнала компоненты X или компоненты Y, которая кодирована посредством обходного кодирования.

Префиксная часть и суффиксная часть определяются в соответствии с каждым значением (в дальнейшем называемым также "последним значением") компоненты X и компоненты Y, как показано, например, на Фиг.3A-3D. Таким образом, с помощью предопределенного способа первый блок 1001 декодирования может определить, содержит ли двоичный сигнал компоненты X суффиксную часть.

Более определенно, когда размер блока преобразования (именуемый в дальнейшем "размером преобразования"), например, составляет 4×4, двоичный сигнал компоненты X содержит только префиксную часть и не содержит суффиксную часть независимо от последнего значения, как показано на Фиг.3A. Таким образом, первый блок 1001 декодирования определяет, что двоичный сигнал компоненты X не содержит суффиксную часть, когда размер блока, который должен быть декодирован, составляет 4×4.

В случае, когда размер преобразования составляет 8x8, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 4-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3B. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 2 бита, когда значения двоичных символов вплоть до двоичного значения символа 4-го бита двоичного сигнала компоненты X все равны "0".

В случае, когда размер преобразования составляет 16×16, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 8-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3C. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 3 бита, когда значения двоичных символов вплоть до значения двоичного символа 8-го бита двоичного сигнала компоненты X все равны "0".

В случае, когда размер преобразования составляет 32x32, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 16-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3D. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 4 бита, когда значения двоичного символа вплоть до значения двоичного символа 16-го бита двоичного сигнала компоненты X все равны "0".

При этом, когда двоичный сигнал компоненты X содержит суффиксную часть ("Да" на этапе S1002), второй блок 1002 декодирования арифметически декодирует суффиксную часть, имеющую предопределенную фиксированную длину в битах (этап S1003). Более определенно, второй блок 1002 декодирования декодирует суффиксную часть компоненты X посредством обходного декодирования. С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть ("Нет" на этапе S1002), процесс декодирования для суффиксной части пропускается.

Блок 1004 восстановления восстанавливает компонент X информации последней позиции с использованием префиксной части и суффиксной части, которые декодированы (этап S1004). Более определенно, когда двоичный сигнал компоненты X содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент X посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть и суффиксную часть. С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент X посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть.

Затем первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты Y информации последней позиции, как на этапе S1001 (этап S1005). После этого первый блок 1001 декодирования определяет, содержит ли двоичный сигнал компоненты Y суффиксную часть, как на этапе S1002 (этап S1006).

При этом, когда двоичный сигнал компоненты Y содержит суффиксную часть ("Да" на этапе S1006), второй блок 1002 декодирования арифметически декодирует суффиксную часть, имеющую предопределенную фиксированную длину, как на этапе S1003 (этап S1007). С другой стороны, когда двоичный сигнал компоненты Y не содержит суффиксную часть ("Нет" на этапе S1006), процесс декодирования для суффиксной части пропускается.

Наконец, блок 1004 восстановления восстанавливает компонент Y информации последней позиции, как на этапе S1004 (этап S1008). Более определенно, когда двоичный сигнал компоненты Y содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент Y посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть и суффиксную часть. С другой стороны, когда двоичный сигнал компоненты Y не содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент Y посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть.

Таким образом, восстанавливаются компонент X и компонент Y, содержащиеся в информации последней позиции.

Затем будет описано кодирование переменной длины и декодирование переменной длины. Стандарт H.264 использует контекстно-адаптивное двоичное арифметическое кодирование (CABAC) как один из способов кодирования переменной длины. Префиксная часть кодируется посредством CABAC. Напротив, суффиксная часть кодируется посредством обходного кодирования, которое является арифметическим кодированием, в котором используется фиксированная вероятность (например, "0,5"). Далее контекстно-адаптивное двоичное арифметическое декодирование и обходное декодирование будут описаны с использованием Фиг.4-6.

Фиг.4 является блок-схемой последовательности операций, показывающей контекстно-адаптивное двоичное арифметическое декодирование. Следует отметить, что Фиг.4 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.4 является таким, которое дано в непатентной литературе 1.

В арифметическом декодировании сначала вводится контекст (ctxIdx), который определяется на основе типа сигнала текущего сигнала, который должен быть декодирован.

Затем на этапе S2001 выполняется следующий процесс.

Сначала вычисляется qCodIRangeIdx из первого параметра codIRange, указывающего текущее состояние арифметического декодирования. Кроме того, получается pStateIdx, который является значением состояния, соответствующим ctxIdx. Затем посредством ссылки на таблицу (rangeTableLPS) получается codIRangeLPS, соответствующий двум значениям (qCodIRangeIdx и pStateIdx).

Следует отметить, что codIRangeLPS указывает состояние арифметического декодирования, когда LPS возник в состоянии арифметического декодирования, указанном первым параметром codIRange. LPS определяет один из символов "0" и "1", который имеет меньшую вероятность возникновения.

Кроме того, codIRange устанавливается равным значению, полученному посредством вычитания упомянутого выше codIRangeLPS из текущего codIRange.

Затем на этапе S2002 выполняется сравнение между codIRange и вторым параметром codIOffset, который указывает состояние арифметического декодирования.

При этом, когда codIOffset больше или равен codIRange ("Да" на этапе S2002), выполняется следующий процесс на этапе S2003.

Сначала определяется, что возник LPS, и binVal, которое является выходным значением декодирования, устанавливается равным значению, отличающемуся от valMPS ("0", когда valMPS = 1, и "1", когда valMPS = 0). Значение valMPS указывает заданное значение MPS ("0" или "1"). Символ MPS определяет одно из значений "0" и "1" двоичного символа, который имеет более высокую вероятность возникновения.

Кроме того, второй параметр codIOffset, который указывает состояние арифметического декодирования, устанавливается равным значению, полученному посредством вычитания codIRange из текущего codIOffset. Кроме того, первый параметр codIRange, который указывает состояние арифметического декодирования, устанавливается равным значению codIRangeLPS, которое было установлено на этапе S2001.

Затем на этапе S2005 определяется, является ли значение pStateIdx равным "0".

При этом, когда значение pStateIdx равно "0" ("Да" на этапе S2005), это означает, что вероятность LPS больше вероятности MPS. Таким образом, значение valMPS переключается (то есть устанавливается "0", когда valMPS = 1, и устанавливается "1", когда valMPS = 0) (этап S2006). С другой стороны, когда значение pStateIdx не равно "0" ("Нет" на этапе S2005), значение pStateIdx обновляется на основе таблицы преобразования transIdxLPS, к которой обращаются, когда возникает символ LPS (этап S2007).

Кроме того, когда codIOffset меньше codIRange ("Нет" на этапе S2002), определяется, что возник символ MPS. Таким образом, значение binVal, которое является выходным значением декодирования, устанавливается равным valMPS, и значение pStateIdx обновляется на основе таблицы преобразования transIdxMPS, к которой обращаются, когда возникает символ MPS (этап S2004).

Наконец, выполняется нормализация (RenormD) (этап S2008), и арифметическое декодирование заканчивается.

Как показано выше, в контекстно-адаптивном двоичном арифметическом декодировании множественные вероятности возникновения символов, которые являются вероятностями возникновения двоичных символов, поддерживаются в связи с индексами контекста. Контексты переключены в соответствии с условием (например, значением смежного блока), и, таким образом, необходимо поддерживать порядок обработки.

Фиг.5 является блок-схемой последовательности операций, показывающей обходное декодирование. Следует отметить, что Фиг.5 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.5 является таким, которое дано в непатентной литературе 1.

Сначала второй параметр codlOffset, который указывает текущее состояние арифметического декодирования, смещается влево (удваивается). Кроме того, один бит считывается из битового потока, и когда считанный бит равен "1", единица добавляется к codIOffset (этап S3001).

Затем, когда codIOffset больше или равен первому параметру codIRange, который указывает состояние арифметического декодирования ("Да" на этапе S3002), значение binVal, которое является выходным значением декодирования, устанавливается равным "1", и codIOffset устанавливается равным значению, полученному посредством вычитания codIRange из текущего codIOffset (этап S3003). С другой стороны, когда codIOffset меньше первого параметра codIRange, который указывает состояние арифметического декодирования ("Нет" на этапе S3002), значение binVal, которое является выходным значением декодирования, устанавливается равным "0" (этап S3004).

Фиг.6 является блок-схемой последовательности операций для подробного описания нормализации (RenormD), показанной на этапе S2008 на Фиг.4. Фиг.6 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.6 является таким, которое дано в не патентной литературе 1.

Когда первый параметр codIRange, который указывает состояние арифметического декодирования, стал меньше 0x100 (в шестнадцатеричной системе; 256 в десятичной системе) ("Да" на этапе S4001), codIRange смещается влево (удваивается). Кроме того, второй параметр codIOffset, который указывает состояние арифметического декодирования, смещается влево (удваивается). Кроме того, один бит считывается из битового потока, и когда считанный бит равен "1", единица добавляется к codIOffset (этап S4002).

Когда codIRange в конечном счете достигает 256 или большего значения посредством этого процесса на этапе S4002 ("Нет" на этапе S4001), нормализация заканчивается.

Таким образом выполняется арифметическое декодирование.

Однако соответствующее переключение среди контекстов (моделей контекстов) является трудным при кодировании или декодировании префиксной части посредством контекстно-адаптивного двоичного арифметического кодирования или контекстно-адаптивного двоичного арифметического декодирования. Например, при арифметическом кодировании и арифметическом декодировании префиксной части контексты переключаются в соответствии с битовой позицией в двоичном сигнале. В это время, если контекст является общим для множества битовых позиций для уменьшения требуемой емкости памяти и уменьшения доступа к памяти, идентичный контекст в некоторых случаях используется для битовых позиций, которые существенно отличаются по вероятности возникновения символа. В таком случае точность предсказания вероятности возникновения символа уменьшается, и, таким образом, также уменьшается эффективность кодирования.

С этой целью способ кодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ кодирования изображения для кодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть кодирован, способ кодирования изображения содержит этапы, на которых: преобразовывают в двоичную форму информацию последней позиции для формирования (i) двоичного сигнала, который включает в себя первый сигнал, имеющий длину, меньшую или равную предопределенной максимальной длине, и не включает в себя второй сигнал или (ii) двоичного сигнала, который включает в себя первый сигнал, имеющий предопределенную максимальную длину, и второй сигнал; выполняют первое кодирование для арифметического кодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа; и выполняют второе кодирование для арифметического кодирования второго сигнала с использованием фиксированной вероятности, когда двоичный сигнал включает в себя второй сигнал, причем при первом кодировании двоичный символ в последней битовой позиции первого сигнала арифметически кодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Двоичный символ в последней битовой позиции первого сигнала указывает, содержит ли двоичный сигнал второй сигнал. Это означает, что двоичный символ в последней битовой позиции первого сигнала имеет большое влияние на эффективность кодирования. Таким образом, двоичный символ в последней битовой позиции первого сигнала имеет признак при возникновении символа, отличающийся от признака двоичных символов в других битовых позициях. С учетом этого возможно увеличить эффективность кодирования посредством арифметического кодирования двоичного символа в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции.

Например, при первом кодировании каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически кодирован с использованием контекста, общего для этих двух или более битовых позиций.

При этом каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически кодирован с использованием контекста, общего для этих двух или более битовых позиций. Это сокращает количество контекстов по сравнению со случаем использования разных контекстов для каждой битовой позиции, и тем самым может быть уменьшена требуемая емкость памяти.

Например, преобразование в двоичную форму может включать в себя изменение предопределенной максимальной длины в соответствии с размером текущего блока.

При этом максимальная длина первого сигнала может быть различной в соответствии с размером текущего блока, который должен быть кодирован. Это позволяет должным образом установить максимальную длину первого сигнала, тем самым увеличивая эффективность кодирования.

Например, способ кодирования изображения может дополнительно содержать этапы, на которых: переключают процесс кодирования либо на первый процесс кодирования, совместимый с первым стандартом, либо на второй процесс кодирования, совместимый со вторым стандартом; и добавляют к битовому потоку идентификационную информацию, указывающую либо первый стандарт, либо второй стандарт, с которым совместим процесс кодирования, на который выполнено переключение, причем когда процесс кодирования переключен на первый процесс кодирования, преобразование в двоичную форму, первое кодирование и второе кодирование могут быть выполнены как первый процесс кодирования.

Это позволяет переключаться между первым процессом кодирования, совместимым с первым стандартом, и вторым процессом кодирования, совместимым со вторым стандартом.

Кроме того, способ декодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ декодирования изображения для декодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть декодирован, способ декодирования изображения содержит этапы, на которых: выполняют первое декодирование для арифметического декодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа, первый сигнал включен в двоичный сигнал информации последней позиции и имеет длину, меньшую или равную предопределенной максимальной длине; и выполняют второе декодирование, когда двоичный сигнал информации последней позиции включает в себя второй сигнал, для арифметического декодирования второго сигнала с использованием фиксированной вероятности, причем при первом декодировании двоичный символ в последней битовой позиции первого сигнала арифметически декодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Двоичный символ в последней битовой позиции первого сигнала указывает, содержит ли двоичный сигнал второй сигнал. Это означает, что двоичный символ в последней битовой позиции первого сигнала имеет большое влияние на эффективность кодирования. Таким образом, двоичный символ в последней битовой позиции первого сигнала имеет признак возникновения значения, отличающийся от признака двоичных символов в других битовых позициях. С учетом этого возможно увеличить эффективность кодирования посредством арифметического декодирования двоичного символа в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции.

Например, при первом декодировании каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически декодирован с использованием контекста, общего для этих двух или более битовых позиций.

При этом каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически декодирован с использованием контекста, общего для этих двух или более битовых позиций. Это сокращает количество контекстов по сравнению со случаем использования разного контекста для каждой битовой позиции, и тем самым может быть уменьшена требуемая емкость памяти.

Например, предопределенная максимальная длина может изменяться в соответствии с размером текущего блока.

При этом максимальная длина первого сигнала может быть различной в соответствии с размером текущего блока, который должен быть декодирован. Это позволяет должным образом установить максимальную длину первого сигнала, тем самым увеличивая эффективность кодирования.

Например, способ декодирования изображения может дополнительно содержать этап, на котором переключают процесс декодирования либо на первый процесс декодирования, совместимый с первым стандартом, либо на второй процесс декодирования, совместимый со вторым стандартом, в соответствии с идентификационной информации, которая добавлена к битовому потоку и указывает либо первый стандарт, либо второй стандарт, причем когда процесс декодирования переключен на первый процесс декодирования, первое декодирование и второе декодирование могут быть выполнены как первый процесс декодирования.

Это позволяет переключаться между первым процессом декодирования, совместимым с первым стандартом, и вторым процессом декодирования, совместимым со вторым стандартом.

Следует отметить, что эти общие и частные аспекты могут быть реализованы с использованием системы, устройства, интегральной схемы, компьютерной програ