Переносной диагностический комплекс

Иллюстрации

Показать всеПереносной диагностический комплекс содержит ПК, адаптер USB, интерфейс USB, микроконтроллер, оперативное запоминающее устройство, интерфейс JTAG, оперативно перепрограммируемый логический узел, две шины управления и две шины данных, программатор, две отдельные взаимно инвертированно-синфазные по отношению друг к другу электрические цепи, соединенные определенным образом. Обеспечивается начальная диагностика, контроль электрических связей, проверка печатных плат, программирование и считывание памяти, тестирование, программные испытания, проверка качества и общей работоспособности цифровых логических микросхем, электронных блоков, узлов и электрических соединений, проверка работоспособности сервисных программ аппаратуры, поддержка технологии граничного сканирования, осуществление мониторинга и отладка изделия, не нарушая его нормальной работы. 1 ил.

Реферат

Изобретение относится к цифровой вычислительной электронике и может использоваться для диагностики работоспособности других электронных устройств, в частности аппаратуры системы управления (СУ).

Из уровня техники известен аналог: переносной программно-диагностический комплекс (патент RU 2363975), который предназначен для диагностики и обнаружения неисправностей радиоэлектронных изделий (РЭИ), который включает: монитор (единое индикаторное устройство для отображения цифробуквенной и графической информации), управляющую ЭВМ, многоканальный генератор аналоговых сигналов с цифровым управлением, многоканальный генератор импульсно-кодовых сигналов с цифровым управлением, многоканальный цифровой преобразователь аналоговых сигналов с цифровым управлением, многоканальный логический анализатор с цифровым управлением, многоканальный диагностический модуль с цифровым управлением, адаптер для соединения с объектом диагностики.

Недостатком аналога является проверка тестируемых изделий посредством тестовых щупов, что допускает воздействие человеческого фактора на результат проверки, а также требует большого количество сигнальных линий для осуществления проверки изделий.

Прототип описан в статье «Разработка отладочного комплекса JTAG для проведения диагностики БЦВМ» (Основные направления и формы использования инновационных разработок при создании ракетно-космической техники. Сборник материалов. Научно-практический семинар молодых ученых и специалистов предприятий космической промышленности, г. Королев Московской области, 2007., ст. 85-98). В статье описывается устройство, в котором тестируемая плата с расположенными на ней БИС подключается через последовательный канал передачи данных (JTAG интерфейс) к некоторому ведущему устройству. Ведущее устройство решает задачи, связанные с диагностикой тестируемого устройства, локализацией неисправностей, загрузкой конфигураций PLD и т.п. Как правило, ведущим устройством является персональный компьютер, оснащенный соответствующим программным обеспечением. В статье приведена схема узлов и связей адаптера с персональным компьютером (ПК) и тестируемым изделием. Адаптер подключается к ПК через интерфейс USB 2.0, а к тестируемому изделию через интерфейс JTAG. ПК, связан через интерфейс USB 2.0, цепь питания которого подключена ко всем элементам адаптера, а шина данных связана с приемопередатчиком интерфейса USB 2.0, который связан двунаправленной шиной данных с микроконтроллером. В свою очередь микроконтроллер имеет однонаправленные связи с функциональными блоками логического узла и связан шиной управления с ОЗУ, при этом адаптер имеет общую шину, которая предоставляет двунаправленную связь между микроконтроллером, ОЗУ, логическим узлом, а также обеспечивает связь микроконтроллера с адресным расширителем, который в свою очередь связан с ОЗУ. Логический узел связан с интерфейсом JTAG через сигнальные линии последовательного синхронного 4-проводного интерфейса JTAG.

Недостатком прототипа является то, что в данной схеме отсутствует возможность оперативного перепрограммирования логического узла, а приведенная в статье схема низкой производительности, ввиду того, что обработка сигналов JTAG полностью возложена на микроконтроллер.

Задачей изобретения является создание мобильного переносного комплекса, позволяющего проводить диагностику, тестирование, программные испытания и настройку радиоэлектронных изделий.

Для решения поставленной задачи адаптер должен работать вместе с ПК и программатором, образуя переносной диагностический комплекс (ПДК). На ПК должно быть установлено программное обеспечение, которое позволяет проводить диагностику, тестирование, программные испытания и настройку РЭИ, а программатор должен применяться для перепрограммирования оперативно перепрограммируемого логического узла адаптера.

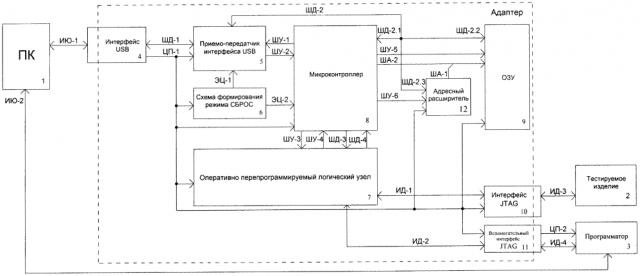

Разработанный ПДК включает в себя следующие элементы, представленные на фигуре:

1 - Персональный компьютер;

2 - Тестируемое изделие;

3 - Программатор;

4 - Интерфейс USB;

5 - Приемопередатчик интерфейса USB;

6 - Схема формирования сигнала СБРОС;

7 - Оперативно перепрограммируемый логический узел;

8 - Микроконтроллер;

9 - ОЗУ

10 - Интерфейс JTAG;

11 - Вспомогательный интерфейс JTAG;

12 - Адресный расширитель.

Элементы ПДК имеют следующие связи.

ПК (1), к которому посредством USB кабеля (ИЮ-1) подключается адаптер через интерфейс USB (4), цепь питания (ЦП-1) которого поступает на приемопередатчик интерфейса USB (5), схему формирования режима СБРОС (6), оперативно перепрограммируемый логический узел (ОПЛУ) (7), микроконтроллер (8), оперативное запоминающее устройство (ОЗУ) (9), интерфейс JTAG (10), вспомогательный интерфейс JTAG (11) и адресный расширитель (12). Информационная шина (ШД-1) интерфейса USB (4) связана с приемопередатчиком интерфейса USB (5). Общая шина данных 8 бит (ШД-2) адаптера подключается к приемопередатчику интерфейса USB (5), микроконтроллеру (8), ОЗУ (9) и адресному расширителю (12), чем обеспечивает: связь (ШД-2.1) приемопередатчика интерфейса USB (5) с микроконтроллером (8), связь (ШД-2.2.) микроконтроллера (8) с ОЗУ (9), связь (ШД-2.3) микроконтроллера (8) с адресным расширителем (12). Микроконтроллер (8) имеет однонаправленную связь шинами управления ШУ-5 и ШУ-6 с ОЗУ (9) и адресным расширителем (12) соответственно и связан взаимно двумя шинами управления (ШУ-1 и ШУ-2) с приемопередатчиком интерфейса USB (5). ОПЛУ (7) и микроконтроллер (8) взаимно связаны между собой двумя шинами управления (ШУ-3 и ШУ-4) и двумя шинами данных (ШД-3 и ШД-4). Схема формирования режима СБРОС (6) связана с приемопередатчиком интерфейса USB (5) и микроконтроллером (8) через отдельные сигнальные независимые электрические цепи (ЭЦ-1 и ЭЦ-2), которые взаимно инвертированно-синфазные по отношению друг к другу. Адресный расширитель (12) и микроконтроллер (8) имеют по одной однонаправленной шине адреса 8-бит (ША-1 и ША-2), вместе образующие одну шину адреса 16-бит, которая соединена с ОЗУ (9). Интерфейс JTAG (10) и вспомогательный интерфейс JTAG (11) подключены к ОПЛУ (7) через сигнальные линии последовательного синхронного 4-проводного интерфейса JTAG (ИД-1 и ИД-2). В интерфейс JTAG (10), с применением JTAG кабеля (ИД-3), подключается тестируемое изделие (2), а вспомогательный интерфейс JTAG (11) также имеет контакты цепи питания (ЦП-2), которая совместно с JTAG кабелем (ИД-4) подключается в программатор (3). Программатор (3) шиной данных, в качестве которой применяется USB кабель (ИЮ-2), связан с ПК (1).

ПДК работает следующим образом.

К адаптеру через интерфейс USB (4) подключается ПК (1), а через интерфейс JTAG (10) - тестируемое изделие (2). Через ПК (1) осуществляется управление адаптером и его питание, в том числе перепрограммирование. В адаптере используется интерфейс USB-2.0 или USB-3.0, при этом нормальная работа адаптера возможна при разных версиях интерфейса USB у адаптера и ПК, наличие интерфейса USB-3.0 у ПК и адаптера повышает быстродействие последнего. Общая шина данных 8-бит (ШД-2) позволяет применять в адаптере микроконтроллер с ограниченным количеством портов 8-бит, так как, используя один порт 8-бит микроконтроллера (8), соединяет его сразу с тремя элементами адаптера. Информация с ПК (1), через интерфейс USB (4), поступает на приемопередатчик интерфейса USB (5), который преобразует цифровой последовательный информационный поток в параллельный цифровой двунаправленный поток и передает его на общую шину данных 8-бит (ШД-2), а сигнал, поступающий по шине управления ШУ-2, обеспечивает его прием микроконтроллером (8) через связь ШД-2.1. Микроконтроллер (8) через шину управления ШУ-1 сообщает о готовности принять (передать) информацию с (на) ПК (1), таким образом приемопередатчик интерфейса USB (5) служит для организации приема и передачи информационного цифрового потока между ПК (1) и микроконтроллером (8), который является инициатором обмена. Также микроконтроллер (8) осуществляет работу с ОЗУ (9) в режимах «чтение» и «запись». Обмен данными между микроконтроллером (8) и ОЗУ (9) осуществляется через общую шину данных 8-бит (ШД-2) посредством связи ШД-2.2. Для чтения и записи информации используется шина адреса (ША-2), шина управления (ШУ-5). Работа микроконтроллера (8) с ОЗУ (9) имеет ряд особенностей, связанных с тем, что ОЗУ (9) является 16-разрядным, а микроконтроллер (8) – 8-разрядным. Если для работы достаточно 50% объема ОЗУ (9), то применяется только одна шина адреса (ША-1 или ША-2), которая выбирается микроконтроллером (8) автоматически на уровне микропрограммы, если для работы требуется более 50% объема ОЗУ (9), то микроконтроллер (8) работает совместно с адресным расширителем (12). Адресный расширитель (12) позволяет 8-разрядному микроконтроллеру (8) задействовать полный объем оперативной памяти 16-разрядного ОЗУ (9). Работа осуществляется следующим образом: микроконтроллер (8) отправляет на общую шину данных 8-бит (ШД-2), по связи ШД-2.3, биты информации [0…7], которые запоминаются адресным расширителем (12) на входе шины адреса (ША-1), после чего адресный расширитель задерживает любую поступающую по общей шине данных 8-бит (ШД-2) информацию, до поступления сигнала от микроконтроллера (8) по шине управления (ШУ-6). Далее микроконтроллер (8) отправляет на вход шины адреса (ША-2) биты информации [8…15], после чего ОЗУ (9), по команде поступающей по шине управления (ШУ-5), принимает объединенный 16-битный сигнал от двух шин адреса (ША-1 и ША-2). Микроконтроллер (8) осуществляет работу с ОПЛУ (7), который является отдельной частью логики, реализованной с применением ПЛИС, и содержит дешифратор, мультиплексор и синхронный двунаправленный сдвиговый регистр, которые формируют циклограмму стандартов JTAG, чем обеспечивают обмен информацией между микроконтроллером (8) и тестируемым изделием (2). Использование ПЛИС позволяет повысить быстродействие, а также точность при работе с данными по интерфейсу JTAG (10) посредством снижения вычислительной нагрузки на микроконтроллер (8) и увеличения доступного в нем объема свободной памяти. Интерфейс JTAG (10) связан с ОПЛУ (7), принимает обработанные микроконтроллером (8) и ОПЛУ (7) сигналы и передает их на подключенное к нему тестируемое изделие (2). Интерфейс JTAG (10) является активным и усиливает сигнал, поступающий на него с ОПЛУ (7), а также способен восстанавливать сигнал, принимаемый из тестируемого изделия (2). Для перепрограммирования ОПЛУ (7) применяется программатор (3), который подключается к ПК (1) и к вспомогательному интерфейсу JTAG (11). Через ПК (1) осуществляется управление программатором (3), а также его питание. Вспомогательный интерфейс JTAG (11) применяется только для перепрограммирования ОПЛУ (7) и помимо сигнальных линий последовательного синхронного 4-проводного интерфейса JTAG, предназначенных для подключения кабеля JTAG (ИД-4), содержит цепь питания (ЦП-2), которая применяется для запитывания входного буфера программатора (3). В адаптере также присутствует схема формирования сигнала сброс (6), которая дает возможность оператору ПК (1) выполнить принудительную перезагрузку микроконтроллера (8) и очистку данных FIFO приемопередатчика интерфейса USB (5).

По существу изобретение представляет собой.

Переносной диагностический комплекс, в котором к ПК (1) подключен адаптер через интерфейс USB (4), цепь питания (ЦП-1) которого подключается ко всем элементам адаптера, а информационная шина связана с приемопередатчиком интерфейса USB (5), который организует прием и передачу информационного цифрового потока между ПК (1) и микроконтроллером (8), который связан шиной управления (ШУ-5) с оперативным запоминающим устройством (9) и применяет адресный расширитель (12) для использования полного объема памяти ОЗУ (9), тестируемое изделие (2) подключено к адаптеру через интерфейс JTAG (10), который связан с логическим узлом, при этом в адаптере применен оперативно перепрограммируемый логический узел (7), который взаимно связан двумя шинами управления (ШУ-3 и ШУ-4) и двумя шинами данных (ШД-3 и ШД-4) с микроконтроллером (8) и вспомогательным интерфейсом JTAG (11), имеющим контакт цепи питания (ЦП-2), в который подключен программатор (3) связанный по цепи управления (ИЮ-2) с ПК (1), общая шина данных 8-бит (ШД-2) обеспечивает связь микроконтроллера (8) с ОЗУ (9), адресным расширителем (12) и приемопередатчиком интерфейса USB (5), с которым он также взаимно связан двумя шинами управления (ШУ-1 и ШУ-2), микроконтроллер (8) дополнительно связан с адресным расширителем (12) шиной управления (ШУ-6) и с ОЗУ (9) шиной адреса 16-бит, которая формируется из двух шин адреса 8-бит (ША-1 и ША-2), исходящих из микроконтроллера (8) и адресного расширителя (12), схема формирования режима СБРОС (6) связана с приемопередатчиком интерфейса USB (5) и микроконтроллером (8) через отдельные сигнальные независимые электрические цепи, которые взаимно инвертированно-синфазные по отношению друг к другу.

Техническим результатом изобретения является расширение функциональных возможностей, повышение быстродействия устройства и снижение его массогабаритных характеристик при использовании микроконтроллера с ограниченным количеством портов.

Переносной диагностический комплекс позволяет осуществлять следующие действия с тестируемым изделием:

1. начальную диагностику и настройку;

2. контроль электрических связей;

3. проверку печатных плат;

4. программирование и считывание памяти;

5. комплексные стендовые работы и программные испытания;

6. проверку качества и общей работоспособности цифровых логических микросхем, электронных блоков, узлов и электрических соединений (разъемных и неразъемных);

7. проверять работоспособность сервисных программ аппаратуры;

8. поддерживает технологию граничного сканирования;

9. вести работу в многогранном режиме.

При работе с тестируемым изделием диагностический комплекс может осуществлять мониторинг работы и отладку изделия, не нарушая его нормальной работы. При наличии у тестируемого изделия собственного микроконтроллера имеется возможность использовать его вычислительные ресурсы для проверки изделия.

Переносной диагностический комплекс, в котором к ПК подключен адаптер через интерфейс USB, цепь питания которого подключается ко всем элементам адаптера, а информационная шина связана с приемопередатчиком интерфейса USB, который организует прием и передачу информационного цифрового потока между ПК и микроконтроллером, который связан шиной управления с оперативным запоминающим устройством и применяет адресный расширитель для использования полного объема памяти ОЗУ, тестируемое изделие подключено к адаптеру через интерфейс JTAG, который связан с логическим узлом, отличающийся тем, что в адаптере применен оперативно перепрограммируемый логический узел, который взаимно связан двумя шинами управления и двумя шинами данных с микроконтроллером и вспомогательным интерфейсом JTAG, имеющим контакт цепи питания, в который подключен программатор, связанный по цепи управления с ПК, общая шина данных 8-бит обеспечивает связь микроконтроллера с ОЗУ, адресным расширителем и приемопередатчиком интерфейса USB, с которым он также взаимно связан двумя шинами управления, микроконтроллер дополнительно связан с адресным расширителем шиной управления и с ОЗУ шиной адреса 16-бит, которая формируется из двух шин адреса 8-бит, исходящих из микроконтроллера и адресного расширителя, схема формирования режима СБРОС связана с приемопередатчиком интерфейса USB и микроконтроллером через отдельные сигнальные независимые электрические цепи, которые взаимно инвертированно-синфазные по отношению друг к другу.