Процессоры, способы, системы и команды с предикацией элементов упакованных данных

Иллюстрации

Показать всеИзобретение относится к процессорам, которые способны обрабатывать упакованные данные. Технический результат заключается в повышении быстродействия и надежности хранения данных. Процессор включает в себя некоторый первый режим, в котором процессор не должен использовать маскирование операции над упакованными данными, и некоторый второй режим, в котором процессор должен использовать маскирование операции над упакованными данными. Декодирующий блок должен в первом режиме декодировать немаскированную команду обработки упакованных данных, предназначенную для некоторой данной операции над упакованными данными, а во втором режиме декодировать маскированную команду обработки упакованных данных, предназначенную для маскированного варианта данной операции над упакованными данными. Исполняющий блок должен, в ответ на декодирование декодирующим блоком, в первом режиме, немаскированной команды, выполнять данную операцию над упакованными данными. Исполняющий блок должен, в ответ на декодирование декодирующим блоком, во втором режиме, маскированной команды, выполнять маскированный вариант данной операции над упакованными данными. 3 н. и 20 з.п. ф-лы, 22 ил.

Реферат

Область техники, к которой относится изобретение

Описываемые здесь варианты воплощения изобретения, в общем, относятся к процессорам. В частности, описываемые здесь варианты воплощения изобретения, в общем, относятся к процессорам, которые способны обрабатывать упакованные данные.

Уровень техники

Многие процессоры имеют архитектуры с одним потоком команд и многими потоками данных (SIMD-архитектуры). В SIMD-архитектурах, вместо скалярной команды, оперирующей только одним элементом данных или парой элементов данных, команда обработки упакованных данных (данных в упакованном формате), векторная команда или SIMD-команда могут оперировать множественными элементами данных или множественными парами элементов данных одновременно (например, параллельно). Процессор может иметь аппаратное обеспечение для параллельного исполнения, отвечающее на команду обработки упакованных данных таким образом, что одновременно (например, параллельно) выполняет множественные операции над множественными элементами данных.

В SIMD-архитектурах множественные элементы данных могут быть упакованы в пределах одного регистра или ячейки памяти как упакованные данные или векторные данные. В упакованных данных разряды (здесь и далее имеются в виду двоичные разряды) регистра или другого места хранения информации могут быть логически разделены на последовательность множественных элементов данных. Каждый из элементов данных может представлять индивидуальную порцию данных, которая хранится в регистре или другом месте хранения информации вместе с другими элементами данных, обычно имеющих одинаковый размер. Например, регистр с разрядностью в 128 разрядов может иметь два элемента упакованных данных с разрядностью в 64 разряда, четыре элемента упакованных данных с разрядностью в 32 разрядов, восемь элементов упакованных данных с разрядностью в 16 разрядов или шестнадцать элементов упакованных данных с разрядностью в 8 разрядов. Каждый из элементов упакованных данных обычно представляет отдельную индивидуальную порцию данных (например, цвет пикселя, координату на графическом изображении и так далее), над которой можно выполнять операции отдельно от других.

Характерно, что один тип команды обработки упакованных данных, векторной команды, или SIMD-команды (например, команда сложения упакованных данных) может определять то, чтобы одна операция над упакованными данными (например, суммирование) выполнялась над всеми соответствующими парами элементов данных из двух исходных операндов с упакованными данными вертикальным образом для того, чтобы сгенерировать результирующие упакованные данные или упакованные данные-адресат. Исходные операнды с упакованными данными могут иметь один и тот же размер, могут содержать элементы данных одно и той же разрядности и, таким образом, могут каждый содержать одно и то же количество элементов данных. Исходные элементы данных в позициях одинаковых разрядов в двух исходных операндах с упакованными данными могут представлять пары соответствующих элементов данных. Операция над упакованными данными может быть выполнена отдельно или, по существу, независимо над каждой из этих пар соответствующих исходных элементов данных для того, чтобы сгенерировать соответствующее количество результирующих элементов данных, и, таким образом, каждая пара соответствующих исходных элементов данных может иметь соответствующий результирующий элемент данных. Как правило, результирующие элементы данных для такого рода команды располагаются в том же самом порядке, и они часто имеют тот же самый размер.

В дополнение к этому приводимому в качестве примера типу команды обработки упакованных данных, имеется многообразие других типов команд обработки упакованных данных. Например, имеются команды, которые имеют только один исходный операнд с упакованными данными. Например, команда сдвига упакованных данных может независимо сдвигать каждый элемент данных из единственных исходных упакованных данных для того, чтобы произвести результирующие упакованные данные. Другие команды обработки упакованных данных могут оперировать больше чем двумя исходными операндами упакованных данных. Помимо этого, другие команды обработки упакованных данных могут оперировать горизонтальным образом элементами данных в пределах одного и того же операнда с упакованными данными, а не вертикальным образом (например, соответствующими элементами данных между из двух исходных операндов упакованных данных). Кроме того, другие команды обработки упакованных данных могут генерировать результирующий операнд упакованных данных другого размера, имеющий элементы данных другого размера и/или имеющий другой порядок элементов данных.

Краткое описание чертежей

Изобретение можно лучше всего понять, обратившись к нижеследующему описанию и прилагаемым к нему чертежам, которые используются для того, чтобы проиллюстрировать варианты воплощения изобретения.

На чертежах:

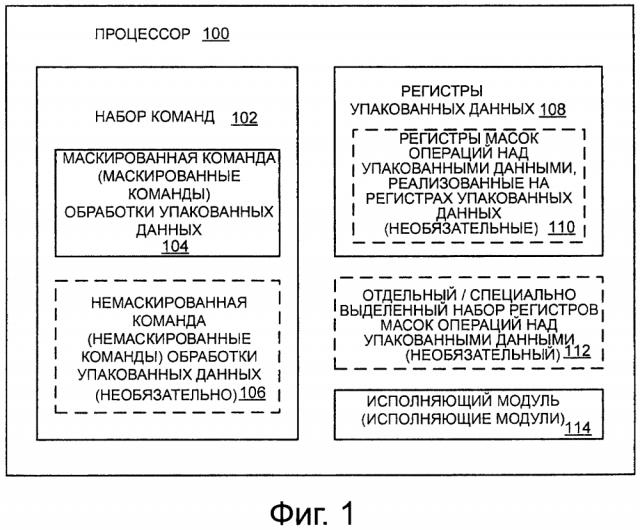

фиг. 1 представляет собой блок-схему одного варианта воплощения процессора;

фиг. 2 представляет собой блок-схему другого варианта воплощения процессора;

фиг. 3 представляет собой блок-схему приводимого в качестве примера варианта воплощения операции над упакованными данными, выполняемой со слиянием;

фиг. 4 представляет собой блок-схему приводимого в качестве примера варианта воплощения операции над упакованными данными, выполняемой с обнулением;

фиг. 5 представляет собой блок-схему алгоритма одного варианта воплощения способа обработки одного варианта воплощения команды обработки упакованных данных;

фиг. 6 представляет собой таблицу, на которой проиллюстрировано то, что количество разрядов маски операции над упакованными данными зависит от разрядности упакованных данных и разрядности элемента упакованных данных;

фиг. 7 представляет собой блок-схему приводимого в качестве примера варианта воплощения подходящего набора регистров маски операции над упакованными данными.

фиг. 8 представляет собой схему, на которой проиллюстрирован вариант воплощения регистра маски операции над упакованными данными и показано, что количество разрядов маски операции над упакованными данными зависит от разрядности упакованных данных и разрядности элемента данных;

фиг. 9 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором один и тот же физический регистр может логически рассматриваться и/или служить объектом доступа либо в качестве регистра упакованных данных, либо в качестве регистра маски операции над упакованными данными;

фиг. 10 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором один и тот же физический регистр может логически рассматриваться и/или служить объектом доступа либо в качестве регистра упакованных данных, либо в качестве регистра масок операций над упакованными данными, хранящего множественные маски операций над упакованными данными;

фиг. 11 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором разряды маски операции над упакованными данными распределены между элементами данных в упакованных данных;

фиг. 12 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров, имеющих разряды маски операции над упакованными данными, распределенные по элементам данных в упакованных данных, может рассматриваться или может служить объектом доступа, на различных представлениях, в качестве хранящего две или более малых масок или единственную большую маску;

фиг. 13А представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера конвейер без переупорядочения последовательности команд, так и приводимый в качестве примера конвейер с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, соответствующие вариантам воплощения изобретения;

фиг. 13В представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера вариант воплощения ядра, имеющего архитектуру без переупорядочения последовательности команд, так и приводимое в качестве примера ядро, имеющее архитектуру с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, подлежащие включению в состав процессора, соответствующего вариантам воплощения изобретения;

фиг. 14А представляет собой блок-схему одиночного ядра процессора наряду с его соединением с расположенной на кристалле сетью межсоединений и с его локальным подмножеством кэша уровня 2 (L 2), соответствующих вариантам воплощения изобретения;

фиг. 14В представляет собой расширенное представление части ядра процессора, показанного на фиг. 14А, соответствующего вариантам воплощения изобретения;

фиг. 15 представляет собой блок-схему процессора, который может иметь больше чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированные графические средства, соответствующего вариантам воплощения изобретения;

на фиг. 16 показана блок-схема системы в соответствии с одним вариантом воплощения настоящего изобретения;

на фиг. 17 показана блок-схема первой более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения;

на фиг. 18 показана блок-схема второй более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения;

на фиг. 19 показана блок-схема внутрикристальной системы (SoC) в соответствии с одним вариантом воплощения настоящего изобретения;

фиг. 20 представляет собой блок-схему, на которой сравнивается использование конвертора команд, реализованного программными средствами, для того, чтобы конвертировать двоичные команды в некотором исходном наборе команд в двоичные команды в некотором заданном наборе команд в соответствии с вариантами воплощения изобретения.

Подробное описание вариантов воплощения изобретения

Здесь раскрываются подходы к операциям с предикатами или масками, выполняемым над элементами упакованных данных. В нижеследующем описании, излагаются многочисленные конкретные подробности (например, конкретные способы реализации маски, конкретные длины масок, форматы данных, конфигурации процессора, микроархитектурные подробности, последовательности операций и так далее). Однако, варианты воплощения изобретения могут быть осуществлены на практике без этих конкретных подробностей. В других случаях, хорошо известные схемы, конструкции и технологии не показаны подробно во избежание затруднения понимания этого описания.

Фиг. 1 представляет собой блок-схему одного варианта воплощения процессора (100). Этот процессор представляет аппарат для обработки команд, который может быть приведен в действие для обработки команд. В некоторых вариантах воплощения изобретения, этот процессор может представлять собой универсальный процессор (например, универсальный микропроцессор, относящийся к типу, часто используемому в качестве центрального процессора (CPU) в настольном компьютере, переносном компьютере и подобных им компьютерах). В качестве альтернативы, этот процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя: сетевые процессоры, процессоры передачи данных, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровой обработки сигналов (DSP-процессоры) и контроллеры (например, микроконтроллеры), в качестве лишь нескольких примеров, но не ограничены ими. Процессор может представлять собой любой процессор из числа: разнообразных процессоров для вычислений со сложным набором команд (CISC-процессоров), разнообразных процессоров для вычислений с сокращенным набором команд (RISC-процессоров), разнообразных процессоров с командными словами сверхбольшой длины (VLIW-процессоров), разнообразных гибридов этих процессоров или других типов процессоров без каких бы то ни было исключений. В некоторых вариантах воплощения изобретения, процессор может представить RISC-процессор, который способен использовать предикацию или для операций над упакованными данными.

Процессор имеет набор (102) команд. Команды этого набора команд представляют макрокоманды, команды на языке ассемблера или команду машинного уровня, которые предоставляются процессору для исполнения, в противоположность микрокомандам, микрооперациям или другим командам и управляющим сигналам, декодируемым или конвертируемым из команд набора команд. В некоторых вариантах воплощения изобретения (например, как в случае некоторых RISC-процессоров), команды могут иметь, по существу, постоянную длину команды (например, все или, по меньшей мере, большинство команд могут иметь 32 разряда или некоторую другую длину), в противоположность случаю, когда они имеют переменную длину команды.

Как показано на фиг. 1, в некоторых вариантах воплощения изобретения, набор команд может, в качестве возможного варианта, включать в себя одну или более команд (106) обработки упакованных данных для одной или более заданных операций над упакованными данными. Как показано на фигуре, набор команд также включает в себя одну или более команд (104) обработки упакованных данных для одной или более заданных операций над упакованными данными. Несколько иллюстративных примеров соответствующих и команд/операций обработки упакованных данных включают в себя: и команды/операции сложения упакованных данных, и команды/операции вычитания упакованных данных, и команды/операции умножения упакованных данных, и команды/операции сдвига упакованных данных, и команды/операции циклического сдвига упакованных данных, и команды/операции сравнения упакованных данных, и команды/операции логического "ИЛИ" в отношении упакованных данных, и команды/операции логического "И" в отношении упакованных данных, и команды/операции нахождения обратной величины упакованных данных, и команды/операции усреднения упакованных данных и другие и арифметические и/или логические команды/операции обработки упакованных данных, известные в данной области техники, но не ограничиваются ими.

Процессор также включает в себя набор регистров (108) упакованных данных. Регистры упакованных данных, в общем, представляют находящиеся на процессоре и/или на кристалле места хранения информации, каждое из которых способно функционировать таким образом, чтобы хранит упакованные данные, векторные данные или данных для архитектуры с одним потоком команд и многими потоками данных (SIMD-данных). Регистры упакованных данных могут представлять регистры, которые являются видимыми для программного обеспечения и/или программиста, и/или регистры, которые специфицируются командами из набора команд для идентификации операндов (например, исходных операндов и операндов-адресатов (для занесения результата)). Регистры могут быть реализованы различными методами в различных микроархитектурах с использованием хорошо известных технологий и не ограничены никаким конкретным типом схемы. Примеры подходящих типов регистров включают в себя: специально выделенные физические регистры, динамически распределяемые физические регистры с использованием переименования регистров и их сочетания, но не ограничены этим.

В некоторых вариантах воплощения изобретения, процессор может, если требуется, иметь набор из одного или большего количества регистров (110) масок операций над упакованными данными, которые (регистры) реализованы на регистрах (108) упакованных данных, хотя это и не является обязательным требованием. В некоторых вариантах воплощения изобретения, процессор может, если требуется, иметь набор из одного или большего количества отдельных специально выделенных регистров (112) масок операций над упакованными данными, которые (регистры) являются отдельными от регистров (108) упакованных данных. Регистры (110) масок операций над упакованными данными и/или регистры (112) масок операций над упакованными данными могут быть использованы для хранения масок операций над упакованными данными. В качестве примера, команды обработки упакованных данных могут иметь один или более разрядов для того, чтобы специфицировать маску операции над упакованными данными, например, регистр (112) масок операций над упакованными данными или регистр (108) упакованных данных. Маски операций над упакованных данных могут также упоминаться в этом описании как предикатные маски или просто маски.

Процессор также включает в себя один или более исполняющих блоков (114). Эти один или более исполняющих блоков (114) способны функционировать таким образом, чтобы исполнять или обрабатывать команды из набора (102) команд (например, команды (104) обработки упакованных данных). В некоторых вариантах воплощения изобретения, исполняющие блоки могут включать в себя специальную логику (например, специальные интегральные схемы или другое аппаратное обеспечение, возможно, объединенное с микропрограммным обеспечением) для исполнения или обработки команд.

В некоторых вариантах воплощения изобретения, процессор может иметь различные режимы, в которых используется или не используется для команд/операций обработки упакованных данных, хотя это и не является обязательным требованием. Например, процессор может иметь некоторый первый режим, в котором процессор не должен использовать операции над упакованными данными, и некоторый второй режим, в котором процессор должен использовать операции над упакованными данными. В качестве примера, при пребывании в первом режиме, могут быть выбраны, декодированы и исполнены команды обработки упакованных данных для того, чтобы выполнять операции над упакованных данными, не используя при этом или маски операций над упакованными данными. В противоположность этому, при пребывании во втором режиме, могут быть выбраны, декодированы и исполнены команды обработки упакованных данных для того, чтобы выполнять операции над упакованных данными, используя маски и операций над упакованными данными. Первый и второй режимы могут быть указаны посредством одного или более разрядов в регистре процессора (например, управляющем регистре, регистре конфигурации и так далее). Такое использование различных режимов может привести к тому, что проявятся преимущества в RISC-процессорах (процессорах для вычислений с сокращенным набором команд), процессорах, которые используют, по существу, постоянную длину команды (например, от большинства до почти всех команд имеют одну и ту же длину команды, такую как 32 разряда), процессорах, которые имеют ограниченное пространство кода операции, и им подобных. Часто, количество имеющихся кодов операций в таких процессорах является недостаточным для того, чтобы поддерживать как , так и варианты некоторой данной операции над упакованными данными. Предоставив другой режим для операций над упакованными данными, можно ввести дополнительные команды для выполнения операций над упакованными данными без необходимости в обязательном порядке увеличивать длину кода операции. Другие варианты воплощения изобретения не ограничены использованием таких режимов.

Фиг. 2 представляет собой блок-схему другого варианта воплощения процессора (200). Как и прежде, этот процессор может представлять универсальный процессор или процессор специального назначения, и может относиться к любым разнообразным типам: RISC, CISC, VLIW, гибридному или другим типам процессоров. Любая из подробностей и необязательных подробностей, упомянутых выше в отношении процессора, показанного на фиг. 1, может, если требуется, также относиться к процессору, показанному на фиг. 2.

Процессор (200) может принимать команду (204) обработки упакованных данных. Например, эта команда может быть принята из блока выборки команд, очереди команд или тому подобного. команда обработки упакованных данных может представлять команду машинного кода, команду на языке ассемблера, макрокоманду или управляющий сигнал набора команд процессора. Подходящим является любой из вышеупомянутых типов команд обработки упакованных данных, так же как и других типы команд обработки упакованных данных.

Проиллюстрированный процессор включает в себя блок (216) декодирования команд. Блок декодирования команд может также упоминаться как декодирующий блок, декодер. Декодирующий блок может принимать и декодировать команды относительно более высокого уровня (например, макрокоманды, команды в машинном коде, команды на языке ассемблера и так далее), и выводить одну или более команд относительно более низкого уровня или управляющие сигналы (например, микрокоманды, микрооперации, точки входа в микрокод), которые отражают, представляют команды более высокого уровня и/или выведены из них. Эти одна или более команд более низкого уровня или управляющие сигналы могут реализовывать команду более высокого уровня посредством одной или более операций более низкого уровня (например, уровня схемы или уровня аппаратного обеспечения). Декодирующий блок может быть реализован с использованием всевозможных различных механизмов, включающих в себя: постоянные запоминающие устройства (ROM-устройства) для микрокода, таблицы поиска, аппаратные варианты реализации, программируемые логические матрицы (PLA-матрицы) и другие механизмы, используемые для реализации декодирующих блоков, известные в данной области техники, но не ограниченных этими механизмами.

В других вариантах воплощения изобретения, могут быть использованы эмулятор, транслятор, блок трансформации, интерпретатор команд или другая логика конвертирования команд. В данной области техники известны всевозможные различные типы логики конвертирования команд, и они могут быть реализованы в виде программного обеспечения, аппаратного обеспечения, микропрограммного обеспечения или их сочетания. Логика конвертирования команд может эмулировать, транслировать, трансформировать, интерпретировать, или иным образом конвертировать команду в одну или более соответствующих производных от нее команд или управляющие сигналы. В некоторых вариантах воплощения изобретения, могут быть использованы как логика конвертирования команд, так и декодирующий блок. Например, логика конвертирования команд может конвертировать команду в одну или больше промежуточных команд, а декодирующий блок может декодировать эти одну или больше промежуточных команд в одну или больше команд более низкого уровня или управляющие сигналы, исполняемые интегральными схемами процессора. Логика конвертирования команд может быть расположена вне процессора (например, на отдельном кристалле или в памяти), на процессоре, или в сочетании этих вариантов.

Процессор также включает в себя набор регистров (208) упакованных данных. Эти регистры упакованных данных могут быть аналогичны регистрам (108) упакованных данных, описанным выше. команда (204) обработки упакованных данных может явным образом специфицировать (например, посредством одного или более полей или набора разрядов), или иным образом указывать (например, указывать неявным образом), некоторые первые исходные упакованные данные (например, некоторый первый регистр (218) исходных упакованных данных). В зависимости от типа команды, команда (204) обработки упакованных данных может, если требуется, явным образом, специфицировать или иным образом указывать некоторые вторые исходные упакованные данных (например, некоторый второй регистр (220) исходных упакованных данных). В некоторых случаях упакованные данные могут, если требуется, специфицировать или иным образом указывать упакованные данные-адресат (например, регистр-адресат (222) упакованных данных). В других вариантах воплощения изобретения, один или более из этих операндов с упакованными данными может быть сохранен в ячейке памяти или другом месте хранения информации. Помимо этого, в других вариантах воплощения изобретения, одно из мест хранения исходных упакованных данных может быть повторно использована в качестве места хранения упакованных данных-адресата.

В некоторых вариантах воплощения изобретения, команда (204) обработки упакованных данных может также специфицировать или иным образом указывать маску (212) операции над исходными упакованными данными (например, регистр маски операции над исходными упакованными данными). В проиллюстрированном варианте воплощения изобретения, маска (212) операции над исходными упакованными данными может представлять регистр, который является отдельным от регистров (208) упакованных данных. В другом варианте воплощения изобретения, маска операции над исходными упакованными данными может быть реализована на регистрах (208) упакованных данных.

Вновь обратимся к фиг. 2, на которой исполняющий блок (214) сопряжен с декодирующим блоком (216), сопряжен с набором (208) регистров упакованных данных и сопряжен с маской (212) операции над исходными упакованными данными. В некоторых вариантах воплощения изобретения, это исполняющий блок может включать в себя: арифметическое устройство, арифметико-логическое устройство, логическое устройство, функциональный блок, блок для приема декодированных команд и выполнения операций или тому подобное. Исполняющий блок может быть способен функционировать в ответ на (204) команду обработки упакованных данных (например, в ответ на одну или более декодированных или иным образом конвертированных команд или управляющие сигналы, которые представляют команду (204) обработки упакованных данных и/или выведены из нее) и/или в результате этой команды таким образом, чтобы выполнять операцию над упакованными данными и сохранять результирующие упакованные данные в операнде или регистре-адресате (222) упакованных данных. Исполняющий блок и/или процессор могут включать в себя специальную или особую логику (например, интегральные схемы или другое аппаратное обеспечение, возможно, объединенное с микропрограммным обеспечением и/или программным обеспечением), которая реагирует на команду обработки упакованных данных таким образом, что выполняет эту операцию над упакованными данными.

В некоторых вариантах воплощения изобретения, процессор может, если требуется, также принимать команду (206) обработки упакованных данных. команда обработки упакованных данных может быть сходна с ранее описанной командой (204) обработки упакованных данных за исключением того, что она не должна специфицировать или иным образом указывать маску операции над упакованных данных, и за исключением того, что она не заставляет процессор использовать . Наоборот, в ответ на эту команду обработки упакованных данных выполняется операция над упакованными данными. Как было описано ранее, в некоторых вариантах воплощения изобретения, процессор может иметь различные режимы, в которых используется или не используется для команд/операций обработки упакованных данных, хотя это и не является обязательным требованием. Например, при пребывании в первом режиме может быть декодирована и исполнена команда (206) обработки упакованных данных для того, чтобы выполнять операцию над упакованными данными, не используя при этом или маску операции над упакованными данными. В противоположность этому, при пребывании во втором режиме может быть декодирована и исполнена команда (204) обработки упакованных данных для того, чтобы выполнять операцию над упакованными данными, маску (212) операции над упакованными данными. Характерно, что первый и второй режимы могут быть указаны посредством одного или более разрядов в регистре процессора (например, управляющем регистре, регистре конфигурации и так далее). Такое использование различных режимов может привести к тому, что проявятся преимущества в RISC-процессорах (процессорах для вычислений с сокращенным набором команд), процессорах, которые используют, по существу, постоянную длину команды (например, от большинства до почти всех команд имеют одну и ту же длину команды, такую как 32 разряда), процессорах, которые имеют ограниченное пространство кода операции, и им подобных. Часто, количество имеющихся кодов операций в таких процессорах является недостаточным для того, чтобы поддерживать как , так и варианты некоторой данной операции над упакованными данными. Предоставив другой режим для операций над упакованными данными, можно ввести дополнительные команды для выполнения операций над упакованными данными без необходимости в обязательном порядке увеличивать длину кода операции. Другие варианты воплощения изобретения не ограничены использованием таких режимов.

Маска операции над упакованными данными может представлять предикатный операнд или операнд условного управления или операнд управления условной векторной операцией. Маска операции над упакованными данными может также упоминаться здесь просто как маска. Эта маска может осуществлять предикацию, условное управление или в отношении того, должны ли быть выполнены операции, ассоциативно связанные с командой обработки упакованных данных, над исходными элементами данных, и/или должны ли результаты этих операций быть сохранены в результирующих упакованных данных. Маска может каждая включать в себя множественные элементы маски, предикатные элементы или элементы условного управления.

В некоторых вариантах воплощения изобретения, маска может быть способна функционировать таким образом, чтобы операции со степенью детализации, соответствующей результирующему элементу данных. В одном аспекте изобретения, элементы маски могут находиться во взаимно-однозначным соответствием с результирующими элементами данных (например, может иметься восемь результирующих элементов данных и восемь соответствующих элементов). Каждый отличный от других элемент маски может быть способен функционировать таким образом, чтобы отличную от других соответствующую операцию над упакованными данными, и/или хранение отличного от других соответствующего результатирующего элемента данных, отдельно и/или, по существу, независимо от других. Например, элемент маски может быть способен функционировать таким образом, чтобы устанавливать маску в отношении того, должна ли операция над упакованными данными быть выполнена над соответствующим элементом данных из исходных упакованных данных (или над парой соответствующих элементов данных, относящихся к двум исходным упакованным данным) и/или должен ли результат операции над упакованными данными быть сохранен в соответствующем результирующем элементе данных.

Обычно каждый элемент маски может представлять собой единственный разряд. Этот единственный разряд может позволить специфицировать любую из двух различных возможностей. В качестве одного примера, каждый разряд может специфицировать либо то, что операция подлежит выполнению, либо то, что она не подлежит выполнению. В качестве другого примера, каждый разряд может специфицировать сохранение результата операции в отличие от того, чтобы не сохранять результат операции. В соответствии с одним возможным соглашением, каждый разряд маски может иметь некоторое первое значение (например, установленное в двоичную "1") для того, чтобы позволять результату операции над упакованными данными быть сохраненным в соответствующем результирующем элементе данных, или может иметь некоторое второе значение (например, очищенное до двоичного "0") для того, чтобы не давать результату операции над упакованными данными быть сохраненным в соответствующем результирующем элементе данных. Возможно также и противоположное соглашение. В других случаях, каждый элемент маски может иметь два или больше разрядов (например, для того, чтобы специфицировать больше чем две различных возможности).