Устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ

Иллюстрации

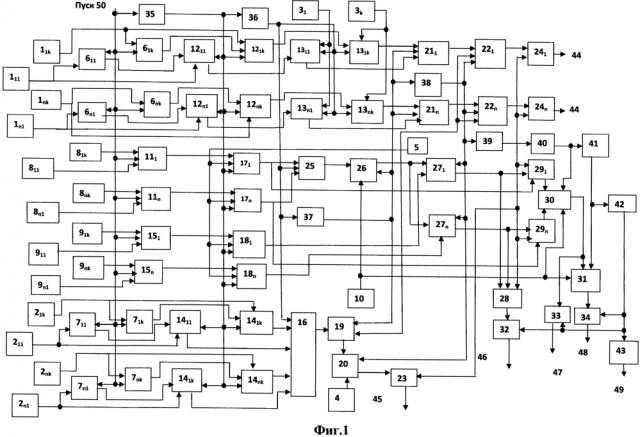

Показать всеИзобретение относится к области вычислительной техники. Техническим результатом является повышение надежности и быстродействия за счет сокращения аппаратных средств. Устройство содержит: первую 1ij и вторую 2ij (i=1, …, n; j=1, …, k) группу регистров, третью группу регистров 3j (j=1, …, k), четвертый регистр 4, пятый регистр 5, первую 6ij и вторую 7ij (i=1, …, n; j=1, …, k) группу логарифмирования, шестую 8ij и седьмую 9ij (i=1, …, n; j=1, …, k) группу регистров, восьмой регистр 10, группу первых 11i и вторых 15i (i=1, …, n) сумматоров, первую 12ij, вторую 13ij и третью 14ij (i=1, …, n; j=1, …, k) группу блоков умножения, третий сумматор 16, группу первых 17i и вторых 18i (i=1, …, n) блоков деления, третий 19 и четвертый 20 блоки деления, четвертые 21j (i=1, …, n) сумматоры, группу пятых 22i (i=1, …, n) блоков деления, девятый регистр 23, группу десятых 24i (i=1, …, n) регистров, пятый сумматор 25, шестой блок деления 26, группу четвертых 27i (i=1, …, n) блоков умножения, шестой сумматор 28, группу 29i (i=1, …, n) блоков вычитания, седьмой сумматор 30, седьмой блок деления 31, одиннадцатый 32, двенадцатый 33 и тринадцатый 34 регистры, первый 35 элемент задержки (ЭЗ), второй 36 ЭЗ, третий 37 ЭЗ, четвертый 38 ЭЗ, пятый 39 ЭЗ, шестой 40 33, седьмой 41 ЭЗ, восьмой 42 ЭЗ, девятый 43 ЭЗ, выходы 44, 45, 46, 47, 48, 49 устройства, вход 50. 1 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для технико-экономического оценивания выполнения научно-исследовательских и опытно-конструкторских работ (НИОКР) с целью объективной оценки выполнения работы в целом и по ее стадиям.

Наиболее близким по технической сущности является устройство [1], содержащее первую 1ij и вторую 2ij (i=1,…n; j=1,…k) группу регистров, третью группу регистров 3j (j=1,…k), четвертый регистр 4, пятый регистр 5, первую 6ij и вторую 7ij (i=1,…n; j=1,…k) группу логарифмирования, шестую 8ij и седьмую 9ij (i=1,…n; j=1,…k) группу регистров, восьмой регистр 10, группу первых 11i и вторых 15i (i=1,…n) сумматоров, первую 12ij, вторую 13ij и третью 14ij (i=1,…n; j=1,…k) группу блоков умножения, третий сумматор 16, группу первых 17i и вторых 18i (i=1,…n) блоков деления, третий 19 и четвертый 20 блоки деления, четвертые 21j (i=1,…n) сумматоры, группу пятых 22i (i=1,…n) блоков деления, девятый регистр 23, группу десятых 24i (i=1,…n) регистров, пятый сумматор 25, шестой блок деления 26, группу четвертых 27i (i=1,…n) блоков умножения, шестой сумматор 28, группу 29i (i=1,…n) блоков вычитания, седьмой сумматор 30, седьмой блок деления 31, одиннадцатый 32, двенадцатый 33 и тринадцатый 34 регистры, первый 35 элемент задержки (ЭЗ), второй 36 ЭЗ, третий 37 ЭЗ, четвертый 38 ЭЗ, пятый 39 ЭЗ, шестой 40 ЭЗ, седьмой 41 ЭЗ, восьмой 42 ЭЗ, девятый 43 ЭЗ вместе со связями.

Задача изобретения - создать устройство, обеспечивающее повышение надежности и быстродействия за счет существенного сокращения аппаратных затрат.

Это решение достигается тем, что в устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ, содержащее первую 1ij и вторую 2iJ (i=1,…n; j=1,…k) группу регистров, третью группу регистров 3j (j=1,…k), четвертый регистр 4, пятый регистр 5, первую 6ij и вторую 7ij (i=1,…n; j=1,…k) группу логарифмирования, шестую 8ij и седьмую 9ij (i=1,…n; j=1,…k) группу регистров, восьмой регистр 10, группу первых 11i и вторых 15i (i=1,…n) сумматоров, первую 12ij, вторую 13ij и третью 14ij (i=1,…n; j=1,…k) группу блоков умножения, третий сумматор 16, группу первых 17i и вторых 18i (i=1,…n) блоков деления, третий 19 и четвертый 20 блоки деления, четвертые 21j (i=1,…n) сумматоры, группу пятых 22i (i=1,…n) блоков деления, девятый регистр 23, группу десятых 24i (i=1,…n) регистров, пятый сумматор 25, шестой блок деления 26, группу четвертых 27i (i=1,…n) блоков умножения, шестой сумматор 28, группу 29i (i=1,…n) блоков вычитания, седьмой сумматор 30, седьмой блок деления 31, одиннадцатый 32, двенадцатый 33 и тринадцатый 34 регистры, первый 35 элемент задержки (ЭЗ), второй 36 ЭЗ, третий 37 ЭЗ, четвертый 38 ЭЗ, пятый 39 ЭЗ, шестой 40 ЭЗ, седьмой 41 ЭЗ, восьмой 42 ЭЗ, девятый 43 ЭЗ, выход первого 1ij (i=1,…n; j=1,…k) регистра подсоединен к первому входу первой 6ij группы логарифмирования, выход второго 2ij (i=1,…n; j=1,…k) регистра подсоединен к первому входу второй 7ij группы логарифмирования, выход шестого регистра 8ij (i=1,…n; j=1,…k) подсоединен к одноименному входу первого сумматора 11i (i=1,…n), выход которого подсоединен к первому входу первого блока деления 17i (i=1,…n), выход которого подсоединен к одноименному входу пятого сумматора 25, выход которого подсоединен к первому входу шестого блока деления 26, выход седьмого регистра 9ij (i=1,…n; j=1,…k) подсоединен к одноименному входу второго сумматора 15i (i=1,…n), выход которого подсоединен к первому входу второго блока деления 18i (i=1,…n), выход первого блока умножения 12ij (i=1,…n; j=1,…k) подсоединен к первому входу блока второго умножения 13ij (i=1,…n; j=1,…k), второй вход которого подсоединен к выходу одноименного третьего регистра 3j (j=1,…k), а выход - к одноименному входу четвертого сумматора 21i (i=1,…n), выход которого подсоединен к первому входу пятого блока деления 22i (i=1,…n), выход восьмого регистра 10 подсоединен ко второму входу шестого блока деления 26, выход которого подсоединен к первым входам четвертых блоков умножения 27i (i=1,…n), выход каждого из которых подсоединен к первым входам блоков вычитания 29i (i=1,…n) и к одоименным первым входам шестого сумматора 28, выход которого подсоединен к первому входу одиннадцатого регистра 32, выход которого является выходом 46 устройства, выходы блоков вычитания 29i (i=1,…n) подсоединены к одоименным первым входам седьмого сумматора 30, выход которого подсоединен к первому входу седьмого блока деления 31 и к первому входу двенадцатого регистра 33, выход которого является выходом 47 устройства, введены новые связи - пусковой сигнал с входа 50 подсоединен к входу первого ЭЗ 35, к управляющим входам первых сумматоров 11i (i=1,…n), к управляющим входам вторых сумматоров 15i (i=1,…n), к управляющим входам первой 6ij и второй 7ij (i=1,…n; j=1,…k) групп логарифмирования, выход первой 6ij (i=1,…n; j=1,…k) группы логарифмирования подсоединен к первому входу первого 12ij блока умножения, ко второму входу которого подсоединен выход первого 1ij регистра, выход второй 7ij (i=1,…n; j=1,…k) группы логарифмирования подсоединен к первому входу третьего 14ij блока умножения, ко второму входу которого подсоединен выход второго 2ij регистра, выход первого ЭЗ 35 подсоединен к входу второго ЭЗ 36 и к управляющим входам первых блоков умножения 12ij (i=1,…n; j=1,…k), к управляющему входу третьего блока умножения 14ij (i=1,…n; j=1,…k), к управляющему входу первого блока деления 17i (i=1,…n), к управляющим входам второго блока деления 18i (i=1,…n), выход пятого регистра 5 подсоединен к вторым входам первого блока деления 17i (i=1,…n), к второму входу второго блока деления 18i (i=1,…n), к первому входу третьего блока деления 19, к второму входу пятого блока деления 22i (i=1,…n), выход которого подсоединен к первому входу десятого регистра 24i (i=1,…n), выход которого является выходом 44i (i=1,…n) устройства, выход второго ЭЗ 36 подсоединен к входу третьего ЭЗ 37 и к управляющим входам вторых блоков умножения 13ij (i=1,…n; j=1,…k), к управляющему входу пятого сумматора 25, к управляющему входу третьего сумматора 16, входы которого подсоединены к одноименным выходам третьих блоков умножения 14ij (i=1,…n; j=1,…k), а выход подсоединен к второму входу третьего блока деления 19, выход которого подсоединен к первому входу четвертого блока деления 20, второй вход которого подсоединен к выходу четвертого регистра 4, а выход - к первому входу девятого регистра 23, выход которого является выходом 45 устройства, выход третьего ЭЗ 37 подсоединен к входу четвертого ЭЗ 38, к управляющему входу третьего блока деления 19, к управляющему входу четвертого сумматора 21i (i=1,…n), к управляющему входу шестого блока деления 26, выход четвертого ЭЗ 38 подсоединен к входу пятого ЭЗ 39, к управляющим входам пятых блоков деления 22i (i=1,…n), к управляющему входу четвертого блока деления 20, к управляющему входу четвертого блока умножения 27i (i=1,…n), вторые входы которого подсоединены к выходам вторых блоков деления 18i (i=1,…n), выход пятого ЭЗ 39 подсоединен к входу шестого ЭЗ 40, к управляющим входам десятых регистров 24i (i=1,…n), к управляющим входам блока вычитания 29i (i=1,…n), к управляющему входу шестого сумматора 28, к управляющему входу девятого регистра 23, второй вход блоков вычитания 29i (i=1,…n) подсоединен к выходам одноименных первых блоков деления 17i (i=1,…n), выход шестого ЭЗ 40 подсоединен к входу седьмого ЭЗ 41, к управляющему входу седьмого сумматора 30, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого ЭЗ 41 подсоединен к входу восьмого ЭЗ 42 и к управляющему входу седьмого блока деления 31, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого блока деления 31 подсоединен к первому входу тринадцатого регистра 34, выход которого является выходом 48 устройства, выход восьмого ЭЗ 42 подсоединен к управляющим входам одиннадцатого регистра 32, двенадцатого регистра 33, тринадцатого регистра 34 и к входу девятого ЭЗ 43, выход которого является выходом 49 устройства.

Сущность изобретения поясняется чертежом. На чертеже (фиг.1) представлена структурная схема предлагаемого устройства.

Устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ (НИОКР) содержит первую 1ij и вторую 2ij (i=1,…n; j=1,…k) группу регистров, третью группу регистров 3j (j=1,…k), четвертый регистр 4, пятый регистр 5, первую 6ij и вторую 7ij (i=1,…n; j=1,…k) группу логарифмирования, шестую 8ij и седьмую 9ij (i=1,…n; j=1,…k) группу регистров, восьмой регистр 10, группу первых 11i и вторых 15i (i=1,…n) сумматоров, первую 12ij, вторую 13ij и третью 14ij (i=1,…n; j=1,…k) группу блоков умножения, третий сумматор 16, группу первых 17i и вторых 18i (i=1,…n) блоков деления, третий 19 и четвертый 20 блоки деления, четвертые 21j (i=1,…n) сумматоры, группу пятых 22i (i=1,…n) блоков деления, девятый регистр 23, группу десятых 24i (i=1,…n) регистров, пятый сумматор 25, шестой блок деления 26, группу четвертых 27i (i=1,…n) блоков умножения, шестой сумматор 28, группу 29i (i=1,…n) блоков вычитания, седьмой сумматор 30, седьмой блок деления 31, одиннадцатый 32, двенадцатый 33 и тринадцатый 34 регистры, первый 35 элемент задержки (ЭЗ), второй 36 ЭЗ, третий 37 ЭЗ, четвертый 38 ЭЗ, пятый 39 ЭЗ, шестой 40 ЭЗ, седьмой 41 ЭЗ, восьмой 42 ЭЗ, девятый 43 ЭЗ.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от известных тем, что дополнительно пусковой сигнал с входа 50 подсоединен к входу первого ЭЗ 35, к управляющим входам первых сумматоров 11i (i=1,…n), к управляющим входам вторых сумматоров 15i (i=1,…n), к управляющим входам первой 6ij и второй 7ij (i=1,…n; j=1,…k) групп логарифмирования, выход первой 6ij (i=1,…n; j=1,…k) группы логарифмирования подсоединен к первому входу первого 12ij блока умножения, ко второму входу которого подсоединен выход первого 1ij регистра, выход второй 7ij (i=1,…n; j=1,…k) группы логарифмирования подсоединен к первому входу третьего 14ij блока умножения, ко второму входу которого подсоединен выход второго 2ij регистра, выход первого ЭЗ 35 подсоединен к входу второго ЭЗ 36 и к управляющим входам первых блоков умножения 12ij (i=1,…n; j=1,…k), к управляющему входу третьего блока умножения 14ij (i=1,…n; j=1,…k), к управляющему входу первого блока деления 17i (i=1,…n), к управляющим входам второго блока деления 18i (i=1,…n), выход пятого регистра 5 подсоединен к вторым входам первого блока деления 17i (i=1,…n), к второму входу второго блока деления 18i (i=1,…n), к первому входу третьего блока деления 19, к второму входу пятого блока деления 22i (i=1,…n), выход которого подсоединен к первому входу десятого регистра 24i (i=1,…n), выход которого является выходом 44i (i=1,…n) устройства, выход второго ЭЗ 36 подсоединен к входу третьего ЭЗ 37 и к управляющим входам вторых блоков умножения 13ij (i=1,…n; j=1,…k), к управляющему входу пятого сумматора 25, к управляющему входу третьего сумматора 16, входы которого подсоединены к одноименным выходам третьих блоков умножения 14ij (i=1,…n; j=1,…k), а выход подсоединен к второму входу третьего блока деления 19, выход которого подсоединен к первому входу четвертого блока деления 20, второй вход которого подсоединен к выходу четвертого регистра 4, а выход - к первому входу девятого регистра 23, выход которого является выходом 45 устройства, выход третьего ЭЗ 37 подсоединен к входу четвертого ЭЗ 38, к управляющему входу третьего блока деления 19, к управляющему входу четвертого сумматора 21i (i=1,…n), к управляющему входу шестого блока деления 26, выход четвертого ЭЗ 38 подсоединен к входу пятого ЭЗ 39, к управляющим входам пятых блоков деления 22i (i=1,…n), к управляющему входу четвертого блока деления 20, к управляющему входу четвертого блока умножения 27i (i=1,…n), вторые входы которого подсоединены к выходам вторых блоков деления 18i (i=1,…n), выход пятого ЭЗ 39 подсоединен к входу шестого ЭЗ 40, к управляющим входам десятых регистров 24i (i=1,…n), к управляющим входам блока вычитания 29i (i=1,…n), к управляющему входу шестого сумматора 28, к управляющему входу девятого регистра 23, второй вход блоков вычитания 29i (i=1,…n) подсоединен к выходам одноименных первых блоков деления 17i (i=1,…n), выход шестого ЭЗ 40 подсоединен к входу седьмого ЭЗ 41, к управляющему входу седьмого сумматора 30, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого ЭЗ 41 подсоединен к входу восьмого ЭЗ 42 и к управляющему входу седьмого блока деления 31, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого блока деления 31 подсоединен к первому входу тринадцатого регистра 34, выход которого является выходом 48 устройства, выход восьмого ЭЗ 42 подсоединен к управляющим входам одиннадцатого регистра 32, двенадцатого регистра 33, тринадцатого регистра 34 и к входу девятого ЭЗ 43, выход которого является выходом 49 устройства.

Устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ функционирует следующим образом.

На информационные входы каждого из регистров 1ij засылаются вероятности P¡j (i=1,…n; j=1,…k) реализуемости i-го параметра в процессе выполнения НИОКР по мнению j-го эксперта. На информационные входы каждого из регистров 2ij (i=1,…n; j=1,…k) засылаются вероятности Pij* влияния i-го параметра на выполнение НИОКР по мнению j-го эксперта. На информационные входы регистров 3j (j=1,…k) засылаются значения bj коэффициентов, учитывающих квалификацию (компетентность) j-го эксперта. На информационные входы регистров 4 и 5 засылаются соответственно количество n параметров, реализуемых в НИОКР, и число k экспертов.

На информационные входы регистров 8ij (i=1,…n; j=1,…k) засылаются значения Cij, характеризующие влияние i-го параметра как доли затрат на выполнение НИОКР по мнению j-го эксперта для базового варианта изделия (аналога или прототипа). На информационные входы регистров 9ij (i=1,…n; j=1,…k) засылаются значения Сij*, характеризующие влияние i-го параметра как доли затрат на выполнение по мнению j-го эксперта для вновь разрабатываемого изделия. На информационный вход регистра 10 засылается значение С, характеризующее стоимость разработки базового изделия.

С выходов регистров 8ij и 9ij (i=1,…n; j=1,…k) величины Сij и Сij* посылаются на входы соответствующих сумматоров 11i и 15i.

С выходов регистров 1ij и 2ij (i=1,…n; j=1,…k) величины Рij и Рij* посылаются на информационные входы соответствующих блоков логарифмирования 6ij и 7ij.

Работа устройства начинается после подачи на вход устройства сигнала ПУСК по входу 50, после чего он поступает на вход элемента задержки 35 и на управляющие входы блоков логарифмирования 6ij и 7ij (i=1,…n; j=1,…k), а также на управляющие входы сумматоров 11i и 15i (i=1,…n).

С выходов блоков логарифмирования 6ij и 7ij (i=1,…n; j=1,…k) значения (lnPij) и (lnPij*) поступают на первые входы каждого из соответствующих блоков умножения 12ij и 14ij соответственно, на вторые входы которых поступают значения Рij и Рij* с выходов одноименных регистров 1ij и 2ij (i=1,…n; j=1,…k).

Значения с выходов сумматоров 11i подаются на входы делимого блоков деления 17i, а значения с выходов сумматоров 15i подаются на входы делимого блоков деления 18i. На входы делителя этих групп засылается с выхода регистра 5 код количества экспертов k.

Элемент задержки 35 задерживает сигнал на время Т35=max{Tз6; Тз7; Тз11; Тз15}, где

Тз6 - время задержки сигнала блоком логарифмирования 6ij (i=1,…, n; j=1…,k);

Тз7 - время задержки сигнала блоком логарифмирования 7ij;

Тз11 - время задержки сигнала сумматором 11i;

Тз15 - время задержки сигнала сумматором 15i.

Сигнал с выхода элемента задержки 35 поступает на управляющие входы блоков умножения 12ij (i=1,…n; j=1,…k), блоков умножения 14ij, блоков деления 17i и блоков деления 18i, а также на вход элемента задержки 36.

С выходов блоков умножения 12ij (i=1,…n; j=1,…k) величины (Рij (lnPij)) засылаются на первые входы соответствующих блоков умножения 13ij (i=1,…n; j=1,…k). С выходов группы блоков умножения 14ij (i=1,…n; j=1,…k) величины (Pij*(lnPij*)) засылаются на одноименные входы сумматора 16.

С выходов группы блоков деления 17i (i=1,…n) результаты, определяемые по формуле (6), засылаются на одноименные входы сумматора 25 и первые входы блоков вычитания 29i (i=1,…n).

С выхода блока деления 18i (i=1,…n) результаты, определяемые по формуле (7), засылается на первые входы соответствующих блоков умножения 27i (i=1,…n).

Элемент задержки 36 задерживает сигнал на время Т36=max{Тз12; Тз14; Тз17; Тз18}, где

Тз12 - время задержки сигнала блоком умножения 12ij (i=1,…, n; j=1…,k);

Тз14 - время задержки сигнала блоком умножения 14ij;

Тз17 - время задержки сигнала блоком деления 17i;

Тз18 - время задержки сигнала блоком деления 18i.

Задержанный сигнал с выхода элемента ЭЗ 36 поступает на управляющие входы блоков умножения 13ij (i=1,…n; j=1,…k), сумматора 16, сумматора 25, а также на вход элемента задержки 37.

На вторые входы выходов блоков умножения 13ij (i=1,…,n; j=1…, k) подаются отрицательные значения (-bj) с обратных выходов регистров 3j. С выходов блоков умножения 13ij коды поступают на одноименные входы сумматоров 21i.

С выхода сумматора 16 величина HΣ, направляется на вход делимого блока 19, на вход делителя которого с выхода регистра 5 подается значение k.

С выхода блока сумматора 25 величина, определяемая по формуле (8), засылается на вход делителя блока деления 26.

Элемент задержки 37 задерживает сигнал на время Т37=max{Тз13; Тз16; Тз25}, где

Тз13 - время задержки сигнала блоком умножения 13ij (i=1,…n; j=1,…k);

Тз16 - время задержки сигнала сумматором 16;

Тз25 - время задержки сигнала сумматором 25.

Задержанный сигнал с выхода элемента 37 поступает на управляющие входы сумматоров 21i (i=1,…n;), блока деления 26 и блока деления 19, а также на вход элемента задержки 38.

На выходах сумматоров 21i (i=1,…n;) получаются коды величины Hi, определяемые по формуле (1). С выходов сумматоров 21i (i=1,…n;) величины (-Pij(lnPij)bj) направляются на входы делимого соответствующих блоков деления 22i, на входы делителя которых подается значение числа экспертов k с выхода регистра 5.

С выхода сумматора 25 значение , вычисляемое по формуле (8), подается на вход делителя блока деления 26, на вход делимого которого поступает с выхода регистра 10 величина С, характеризующая стоимость разработки базового изделия.

С выхода блока деления 19 код направляется на вход делимого блока деления 20. Значение количества параметров n, реализуемых в НИОКР, с выхода регистра 4 засылается на второй вход делителя блока 20.

Элемент задержки 38 задерживает сигнал на время Т38=max{Тз21; Тз19; Тз26;}, где

Тз21 - время задержки сигнала блоком умножения 21i (i=1,…n);

Тз26 - время задержки сигнала блоком деления 26;

Тз19 - время задержки сигнала блоком деления 19.

Задержанный сигнал с выхода элемента 38 поступает на управляющие входы блоков деления 22i, блока деления 20, блоков умножения 27i (i=1,…n), а также на вход элемента задержки 39.

С выхода блока деления 20 величина HΣ, вычисленная по формуле (5), подается на информационный вход регистра 23, с выхода которого этот код далее подается на выход 45 устройства.

С выходов каждого блока деления 22i значения Нi*, определенные по формуле (2), подаются на информационные входы соответствующих выходных регистров 24i, с выхода каждого регистра коды далее подаются на выходы 44i (i=1,…n) устройства.

С выхода блока деления 26 величина , определяемая по формуле (9), засылается на первые входы блоков умножения 27i, на вторые входы которого засылаются коды с выхода блока деления 18i. С выхода блока умножения 27i значение Ciут, вычисляемое по формуле (12*), подается на входы сумматора 28 и на входы соответствующих блоков вычитания 29i.

Элемент задержки 39 задерживает сигнал на время Т39=max{Тз22; Тз20; Тз27;}, где

Тз22 - время задержки сигнала блоком деления 22i (i=1,…n);

Тз20 - время задержки сигнала блоком деления 20;

Тз27 - время задержки сигнала блоком умножения 27i.

Задержанный сигнал с выхода элемента 39 поступает на управляющие входы регистров 24i (i=1,…n), регистра 23, сумматора 28, блоков вычитания 29i, а также на вход элемента задержки 40.

С выхода регистра 23 код поступает на выход 43 устройства.

С выходов регистров 24i коды поступают на выходы 44i (i=1,…n) устройства.

С выхода сумматора 28 код поступает на вход регистра 32 и далее на выход 46 устройства.

С выходов блоков умножения 27i (i=1,…n) величины , определяемые по формуле (12*), засылаются на входы уменьшаемого блоков вычитания 29i, на входы вычитаемого которой направляются величины с выхода блока 17i (i=1,…n).

Элемент задержки 40 задерживает сигнал на время Т40=max{Тз24; Тз23; Т28; Тз29;}, где

Тз24 - время задержки сигнала регистром 24i (i=1,…n);

Тз23 - время задержки сигнала регистром 23;

Тз28 - время задержки сигнала сумматором 28;

Тз29 - время задержки сигнала блоком вычитания 29i (i=1,…n).

Задержанный сигнал с выхода элемента 40 поступает на управляющий вход сумматора 30, а также на вход элемента задержки 41.

На входы сумматора 30 поступают коды с выходов блоков вычитания 29i (i=1,…n) и код с выхода регистра 10. С выхода сумматора 30 код, полученный по зависимости (16), поступает на первый вход блока деления 31 и на вход регистра 33.

Элемент задержки 41 задерживает сигнал на время Т41=max{Тз30; Тз31},

где Тз30; - время надежного срабатывания сумматора 30;

Тз31 - время надежного срабатывания блока деления 31.

Задержанный сигнал с выхода элемента ЭЗ 41 поступает на управляющий вход делимого блока деления 31, а также на вход элемента задержки 42.

С выхода блока деления 31 значение ΔC, определяемое по формуле (17), подается на информационный вход выходного регистра 34.

Элемент задержки 42 задерживает сигнал на время Тз31 - время надежного срабатывания блока деления 31.

Задержанный сигнал с выхода 42 поступает на управляющие входы выходных регистров 32, 33, 34, а также на вход элемента задержки 43.

Коды с выходов регистров 32, 33, 34 поступают на выходы 46, 47, 48 устройства.

Элемент задержки 43 задерживает сигнал на время Тз34 - время надежного срабатывания регистра 34, после чего на его выходе 49 появляется сигнал окончания работы устройства.

Оценку выполнения НИОКР с помощью этого устройства можно осуществить следующим образом [1].

Определяется величина энтропии Hi выполнения НИОКР относительно i-го параметра:

где Pij - вероятность реализуемости i-го параметра в процессе выполнения НИОКР по мнению j-го эксперта (эти величины назначаются (выдаются) экспертами в условиях заранее установленных времени выполнения НИОКР и затрат на ее выполнение);

bj - нормированный коэффициент, учитывающий квалификацию (компетентность) j-го эксперта, 0<bj<1;

k - число экспертов;

n - количество параметров, реализуемых в НИОКР. Далее определяется усредненная величина энтропии Нi* выполнения НИОКР относительно i-го параметра по следующей формуле:

Определяется величина энтропии Hi∑ влияния i-го параметра на выполнение НИОКР по следующей зависимости:

где Рij* - вероятность влияния i-го параметра на выполнение НИОКР по мнению j-го эксперта (эти величины задают эксперты, которые учитывают заранее установленные время (сроки) выполнения НИОКР и затраты на ее выполнение).

В дальнейшем оценивается усредненная величина энтропии НiΣ* влияния i-го параметра на выполнение НИОКР:

В заключение определяется величина НΣ энтропии выполнения НИОКР по формуле:

Выходными параметрами будут являться значения Нi* и НΣ. Значения Нi* характеризуют неопределенность выполнения НИОКР относительно i-го параметра и могут быть использованы заказчиками и исполнителями НИОКР.

Величина НΣ позволяет выбрать «оптимальный» (рациональный) вариант выполнения НИОКР в плане объема финансирования, сроков проведения и количества реализуемых параметров.

В качестве исходных положений алгоритма технико-экономической оценки выполнения НИОКР принимается ранее выполненная работа (базовый вариант изделия), стоимость разработки которого известна - С. Объем затрат как для базового варианта изделия, так и для вновь разрабатываемого (оцениваемого) определяем экспертным путем. При этом влияние i-го параметра (характеристики) как доли затрат на выполнение НИОКР (парциальные затраты) оцениваются j-ми экспертами: - Сij (i=1,…, n; j=1…, k;) для базового варианта изделия (аналога или прототипа) и Сij* - для вновь разрабатываемого (Сij и Сij* - безразмерные величины). Значения Сij и Сij* должны быть в пределах от 0 до 1.

Усредненные величины по i-му параметру по оценкам j-x экспертов равны:

для базового варианта (аналога или прототипа) -

i=1,…, n; j=1…, k; n - число параметров; k - количество экспертов;

для вновь разрабатываемого варианта изделия

Суммы этих величин по всем i-м параметрам будут определяться следующим образом: для базового варианта изделия

Определяется величина объема затрат на разработку базового варианта изделия, приходящаяся на единицу СΣ, по следующей формуле:

Затем для каждого i-го параметра уточняется абсолютное значение затрат при разработке базового варианта изделия:

Коэффициентом KСi определяется увеличение затрат по i-м параметрам для вновь разрабатываемого изделия по отношению к базовому:

Абсолютные значения по i-м параметрам соответственно будут:

Подставляя в выражение (12) значения, полученные по зависимостям (7) и (9), получается следующее выражение:

По всем параметрам (в целом по разрабатываемому изделию) значение С* составит:

где n - количество параметров (характеристик).

Разница между затратами на разработку вновь создаваемого изделия и базового составит:

для i-го параметра

для новой НИОКР

Затраты на вновь создаваемое изделие составят:

Относительное увеличение затрат на вновь разрабатываемое изделие по отношению к затратам по созданию базового изделия будет:

Таким образом, технический результат заявленного изобретения достигается при помощи технических средств (блоков и элементов), упомянутых в описании работы устройства.

Описанное устройство позволяет повысить надежность и быстродействие устройства при оценке стоимости выполнения НИОКР. Это позволяет дать технико-экономическую (комплексную) оценку выполнимости новых НИОКР (вновь разрабатываемых изделий), а ЛПР более объективно принять решение.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в разных областях (отраслях) производства при выборе рационального варианта НИОКР и оценке ее выполнения.

Литература

1. RU 2470365, 2014 г.

Устройство для технико-экономической оценки выполнения научно-исследовательских и опытно-конструкторских работ, содержащее первую 1ij и вторую 2ij (i=1, …, n; j=1, …, k) группу регистров, третью группу регистров 3j (j=1, …, k), четвертый регистр 4, пятый регистр 5, первую 6ij и вторую 7ij (i=1, …, n; j=1, …, k) группу логарифмирования, шестую 8ij и седьмую 9ij (i=1, …, n; j=1, …, k) группу регистров, восьмой регистр 10, группу первых 11i и вторых 15i (i=1, …, n) сумматоров, первую 12ij, вторую 13ij и третью 14ij (i=1, …, n; j=1, …, k) группу блоков умножения, третий сумматор 16, группу первых 17i и вторых 18i (i=1, …, n) блоков деления, третий 19 и четвертый 20 блоки деления, четвертые 21j (i=1, …, n) сумматоры, группу пятых 22i (i=1, …, n) блоков деления, девятый регистр 23, группу десятых 24i (i=1, …, n) регистров, пятый сумматор 25, шестой блок деления 26, группу четвертых 27i (i=1, …, n) блоков умножения, шестой сумматор 28, группу 29i (i=1, …, n) блоков вычитания, седьмой сумматор 30, седьмой блок деления 31, одиннадцатый 32, двенадцатый 33 и тринадцатый 34 регистры, первый 35 элемент задержки (ЭЗ), второй 36 ЭЗ, третий 37 ЭЗ, четвертый 38 ЭЗ, пятый 39 ЭЗ, шестой 40 ЭЗ, седьмой 41 ЭЗ, восьмой 42 ЭЗ, девятый 43 ЭЗ, выход первого 1ij (i=1, …, n; j=1, …, k) регистра подсоединен к первому входу первой 6ij группы логарифмирования, выход второго 2ij (i=1,…n; j=1,…k) регистра подсоединен к первому входу второй 7ij группы логарифмирования, выход шестого регистра 8ij (i=1, …, n; j=1, …, k) подсоединен к одноименному входу первого сумматора 11i (i=1, …, n), выход которого подсоединен к первому входу первого блока деления 17i (i=1, …, n), выход которого подсоединен к одноименному входу пятого сумматора 25, выход которого подсоединен к первому входу шестого блока деления 26, выход седьмого регистра 9ij (i=1, …, n; j=1, …, k) подсоединен к одноименному входу второго сумматора 15i (i=1, …, n), выход которого подсоединен к первому входу второго блока деления 18i (i=1, …, n), выход первого блока умножения 12ij (i=1, …, n; j=1, …, k) подсоединен к первому входу блока второго умножения 13ij (i=1, …, n; j=1, …, k), второй вход которого подсоединен к выходу одноименного третьего регистра 3j (j=1, …, k), а выход - к одноименному входу четвертого сумматора 21i (i=1, …, n), выход которого подсоединен к первому входу пятого блока деления 22i (i=1, …, n), выход восьмого регистра 10 подсоединен ко второму входу шестого блока деления 26, выход которого подсоединен к первым входам четвертых блоков умножения 27i (i=1, …, n), выход каждого из которых подсоединен к первым входам блоков вычитания 29i (i=1, …, n) и к одноименным первым входам шестого сумматора 28, выход которого подсоединен к первому входу одиннадцатого регистра 32, выход которого является выходом 46 устройства, выходы блоков вычитания 29i (i=1, …, n) подсоединены к одноименным первым входам седьмого сумматора 30, выход которого подсоединен к первому входу седьмого блока деления 31 и к первому входу двенадцатого регистра 33, выход которого является выходом 47 устройства, отличающееся тем, что пусковой сигнал с входа 50 подсоединен к входу первого ЭЗ 35, к управляющим входам первых сумматоров 11i (i=1, …, n), к управляющим входам вторых сумматоров 15i (i=1, …, n), к управляющим входам первой 6ij и второй 7ij (i=1, …, n; j=1, …, k) групп логарифмирования, выход первой 6ij (i=1, …, n; j=1, …, k) группы логарифмирования подсоединен к первому входу первого 12ij блока умножения, ко второму входу которого подсоединен выход первого 1ij регистра, выход второй 7ij (i=1, …, n; j=1, …, k) группы логарифмирования подсоединен к первому входу третьего 14ij блока умножения, ко второму входу которого подсоединен выход второго 2ij регистра, выход первого ЭЗ 35 подсоединен к входу второго ЭЗ 36 и к управляющим входам первых блоков умножения 12ij (i=1, …, n; j=1, …, k), к управляющему входу третьего блока умножения 14ij (i=1, …, n; j=1, …, k), к управляющему входу первого блока деления 17i (i=1, …, n), к управляющим входам второго блока деления 18i (i=1, …, n), выход пятого регистра 5 подсоединен к вторым входам первого блока деления 17i (i=1, …, n), к второму входу второго блока деления 18i (i=1, …, n), к первому входу третьего блока деления 19, к второму входу пятого блока деления 22i (i=1, …, n), выход которого подсоединен к первому входу десятого регистра 24i (i=1, …, n), выход которого является выходом 44i (i=1, …, n) устройства, выход второго ЭЗ 36 подсоединен к входу третьего ЭЗ 37 и к управляющим входам вторых блоков умножения 13ij (i=1, …, n; j=1, …, k), к управляющему входу пятого сумматора 25, к управляющему входу третьего сумматора 16, входы которого подсоединены к одноименным выходам третьих блоков умножения 14ij (i=1, …, n; j=1, …, k), а выход подсоединен к второму входу третьего блока деления 19, выход которого подсоединен к первому входу четвертого блока деления 20, второй вход которого подсоединен к выходу четвертого регистра 4, а выход - к первому входу девятого регистра 23, выход которого является выходом 45 устройства, выход третьего ЭЗ 37 подсоединен к входу четвертого ЭЗ 38, к управляющему входу третьего блока деления 19, к управляющему входу четвертого сумматора 21i (i=1, …, n), к управляющему входу шестого блока деления 26, выход четвертого ЭЗ 38 подсоединен к входу пятого ЭЗ 39, к управляющим входам пятых блоков деления 22i (i=1, …, n), к управляющему входу четвертого блока деления 20, к управляющему входу четвертого блока умножения 27i (i=1, …, n), вторые входы которого подсоединены к выходам вторых блоков деления 18i (i=1, …, n), выход пятого ЭЗ 39 подсоединен к входу шестого ЭЗ 40, к управляющим входам десятых регистров 24i (i=1, …, n), к управляющим входам блока вычитания 29i (i=1, …, n), к управляющему входу шестого сумматора 28, к управляющему входу девятого регистра 23, второй вход блоков вычитания 29i (i=1, …, n) подсоединен к выходам одноименных первых блоков деления 17i (i=1, …, n), выход шестого ЭЗ 40 подсоединен к входу седьмого ЭЗ 41, к управляющему входу седьмого сумматора 30, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого ЭЗ 41 подсоединен к входу восьмого ЭЗ 42 и к управляющему входу седьмого блока деления 31, второй вход которого подсоединен к выходу восьмого регистра 10, выход седьмого блока деления 31 подсоединен к первому входу тринадцатого регистра 34, выход которого является выходом 48 устройства, выход восьмого ЭЗ 42 подсоединен к управляющим входам одиннадцатого регистра 32, двенадцатого регистра 33, тринадцатого регистра 34 и к входу девятого ЭЗ 43, выход которого является выходом 49 устройства.