Вычислитель радиальной скорости движущегося объекта

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и предназначено для вычисления на основе корреляционного принципа радиальной скорости движущегося объекта; может использоваться в автоматизированных системах управления воздушным движением для обнаружения и измерения скорости летательных аппаратов. Достигаемый технический результат - повышение точности измерения скорости за счет меньшего числа функциональных преобразований и расширение диапазона однозначно измеряемой радиальной скорости при сохранении однозначного измерения дальности. Указанный результат достигается за счет того, что вычислитель радиальной скорости движущегося объекта содержит блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения, блок вычисления фазы, блок коррекции пределов измерения, умножитель, ключ, блок вычисления модуля, первый блок памяти, блок управления, пороговый блок, второй блок памяти, синхрогенератор, первый и второй двухканальные ключи, дополнительный блок усреднения, дополнительный блок задержки, дополнительный блок комплексного сопряжения и дополнительный блок комплексного умножения, соединенные определенным образом и осуществляющие межпериодную корреляционную обработку исходных отсчетов. 11 ил.

Реферат

Изобретение относится к вычислительной технике и предназначено для вычисления на основе корреляционного принципа радиальной скорости движущегося объекта; может использоваться в автоматизированных системах управления воздушным движением для обнаружения и измерения скорости летательных аппаратов.

Известен многоканальный неследящий фильтровой измеритель [1], каждый канал которого содержит последовательно соединенные согласованный фильтр и детектор, выходы каналов объединены решающим устройством. Однако данное устройство обладает невысокой точностью измерения.

Известно также устройство обработки сигнала движущейся цели [2], содержащее последовательно включенные блоки задержки, умножитель комплексных чисел и вычитатель. Однако это устройство обладает низкой точностью и неоднозначностью измерения.

Наиболее близким к изобретению является измеритель доплеровских сигналов [3], выбранный в качестве прототипа, содержащий блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения, блок вычисления фазы, умножитель, ключ, блок вычисления модуля, первый блок памяти, блок управления, пороговый блок, второй блок памяти и синхрогенератор. Однако данное устройство обладает неоднозначностью и невысокой точностью измерения за счет наличия большого числа функциональных преобразований.

Задачей, решаемой в изобретении, является расширение диапазона однозначно измеряемой радиальной скорости и повышение точности измерения за счет меньшего числа функциональных преобразований при применении совместной обработки неэквидистантных импульсных радиосигналов.

Для решения поставленной задачи в вычислитель радиальной скорости движущегося объекта, содержащий блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения, блок вычисления фазы, блок коррекции пределов измерения, умножитель, ключ, первый блок памяти, блок вычисления модуля, блок управления, пороговый блок, второй блок памяти и синхрогенератор, введены первый и второй двухканальные ключи, дополнительный блок усреднения, дополнительный блок задержки, дополнительный блок комплексного сопряжения и дополнительный блок комплексного умножения.

Дополнительные блоки, введенные в предлагаемый вычислитель, являются известными. Так, соединенные вместе блок задержки, блок комплексного сопряжения и блок комплексного умножения позволяют выделить доплеровский набег фазы за интервал между соседними импульсами. Однако неизвестно совместное применение блока задержки, блока комплексного сопряжения, блока комплексного умножения, первого и второго двухканальных ключей, блока управления, дополнительного блока задержки, дополнительного блока комплексного сопряжения и дополнительного блока комплексного умножения. Новыми являются связи первого и второго двухканальных ключей с блоком комплексного умножения и блоком управления, блока усреднения с первым двухканальным ключом и дополнительным блоком задержки, дополнительного блока усреднения со вторым двухканальным ключом и дополнительным блоком комплексного сопряжения, дополнительного блока комплексного умножения с дополнительным блоком задержки и дополнительным блоком комплексного сопряжения, дополнительного блока комплексного умножения с блоком вычисления фазы, блоком коррекции пределов измерения и блоком вычисления модуля, что обеспечивает расширение диапазона однозначно измеряемой радиальной скорости и повышение точности измерения за счет меньшего числа функциональных преобразований при применении совместной обработки радиоимпульсных сигналов. Связи между синхрогенератором и всеми блоками вычислителя радиальной скорости движущегося объекта обеспечивают согласованную обработку неэквидистантной последовательности радиосигналов.

Сравнение с техническими характеристиками, известными из опубликованных источников информации, показывает, что заявляемое решение обладает новизной и имеет изобретательский уровень.

Заявляемое решение носит технический характер, осуществимо, воспроизводимо и, следовательно, является промышленно применимым.

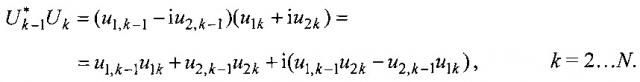

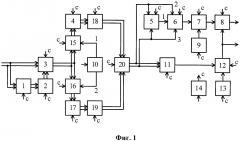

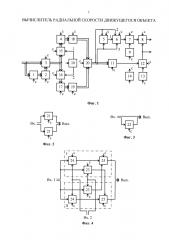

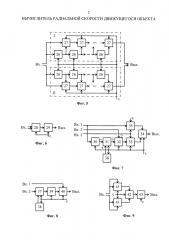

На фиг. 1 представлена структурная электрическая схема вычислителя радиальной скорости движущегося объекта; на фиг. 2 - блока задержки; на фиг. 3 - блока комплексного сопряжения; на фиг. 4 - блока комплексного умножения; на фиг. 5 - блока усреднения; на фиг. 6 - блока вычисления фазы; на фиг. 7 - блока коррекции пределов измерения; на фиг. 8 - блока присвоения знака; на фиг. 9 - блока вычисления модуля, на фиг. 10 - двухканального ключа; на фиг. 11 - блока управления.

Вычислитель радиальной скорости движущегося объекта (фиг. 1) содержит блок 1 задержки, блок 2 комплексного сопряжения, блок 3 комплексного умножения, блок 4 усреднения, блок 5 вычисления фазы, блок 6 коррекции пределов измерения, умножитель 7, ключ 8, первый блок 9 памяти, блок 10 управления, блок 11 вычисления модуля, пороговый блок 12, второй блок 13 памяти, синхрогенератор 14, первый двухканальный ключ 15, второй двухканальный ключ 16, дополнительный блок 17 усреднения, дополнительный блок 18 задержки, дополнительный блок 19 комплексного сопряжения и дополнительный блок 20 комплексного умножения, при этом выходы блока 1 задержки соединены с входами блока 2 комплексного сопряжения, выходы которого соединены с первыми входами блока 3 комплексного умножения, вторые входы которого объединены с входами блока 1 задержки, выход первого блока 9 памяти соединен с первым входом умножителя 7, выход которого соединен с входом ключа 8, выход порогового блока 12 соединен с управляющим входом ключа 8, первый вход порогового блока 12 соединен с выходом второго блока 13 памяти, выходы блока 3 комплексного умножения соединены с объединенными входами первого 15 и второго 16 двухканальных ключей, управляющие входы которых соединены соответственно с первым и вторым выходами блока 10 управления, выходы первого двухканального ключа 15 соединены с входами блока 4 усреднения, выходы которого соединены с входами дополнительного блока 18 задержки, выходы второго двухканального ключа 16 соединены с входами дополнительного блока 17 усреднения, выходы которого соединены с входами дополнительного блока 19 комплексного сопряжения, выходы дополнительного блока 18 задержки соединены с первыми входами дополнительного блока 20 комплексного умножения, вторые входы которого соединены с выходами дополнительного блока 19 комплексного сопряжения, выходы блока 20 комплексного умножения соединены с объединенными входами блока 5 вычисления фазы, вторым и третьим входами блока 6 коррекции пределов измерения и блока 11 вычисления модуля, выход блока 11 вычисления модуля соединен со вторым входом порогового блока 12, выход блока 6 коррекции пределов измерения соединен со вторым входом умножителя 7, выход синхрогенератора 14 соединен с синхровходами блока 1 задержки, блока 2 комплексного сопряжения, блока 3 комплексного умножения, блока 4 усреднения, блока 5 вычисления фазы, блока 6 коррекции пределов измерения, умножителя 7, ключа 8, первого блока 9 памяти, блока 11 вычисления модуля, порогового блока 12, второго блока 13 памяти, первого 15 и второго 16 двухканальных ключей, дополнительного блока 17 усреднения, дополнительного блока 18 задержки, дополнительного блока 19 комплексного сопряжения и дополнительного блока 20 комплексного умножения, причем входами вычислителя радиальной скорости движущегося объекта являются входы блока 1 задержки, а первым и вторым выходами - соответственно выход ключа 8 и выход порогового блока 12.

Блок 1 задержки и дополнительный блок 18 задержки (фиг. 2) содержат две цифровые линии задержки 21, входами блоков задержки являются входы цифровых линий задержки 21, выходы которых являются выходами блоков задержки.

Блок 2 комплексного сопряжения и дополнительный блок 19 комплексного сопряжения (фиг. 3) содержат инвертор 22, первый вход блока комплексного сопряжения является его первым выходом, вторым входом является вход инвертора, выход которого является вторым выходом блока комплексного сопряжения.

Блок 3 комплексного умножения и дополнительный блок 20 комплексного умножения (фиг. 4) содержат два канала (I, II), каждый из которых включает первый перемножитель 23, последовательно включенные второй перемножитель 24 и сумматор 25, выход первого перемножителя 23 одного канала соединен со вторым входом сумматора 25 другого канала, а первыми и вторыми входами блока комплексного умножения соответственно являются объединенные между собой первые входы первого и второго перемножителей 23, 24 каждого из каналов, объединенные вторые входы первых перемножителей 23 и объединенные вторые входы вторых перемножителей 24, а выходами блока комплексного умножения являются выходы сумматоров 25 каждого из каналов.

Блок 4 усреднения и дополнительный блок 17 усреднения (фиг. 5) содержат два канала (I, II), каждый из которых состоит из (N-3)/2 последовательно включенных цифровых линий задержки 26 и (N-3)/2 последовательно включенных сумматоров 27, входами блока усреднения являются объединенные входы первой линии задержки 26 и первого сумматора 27 каждого канала (I, II), а выход k-й [k=1 … (N-3)/2] линии задержки 26 соединен со вторым входом k-го [k=1 … (N-3)/2)] сумматора 27 каждого канала (I, II), выходами блока усреднения служат выходы [(N-3)/2]-x сумматоров 27.

Блок 5 вычисления фазы (фиг. 6) содержит последовательно соединенные делитель 28 и функциональный преобразователь 29, входами блока вычисления фазы являются входы делителя 28, а выходом блока вычисления фазы является выход функционального преобразователя 29.

Блок 6 коррекции пределов измерения (фиг. 7) содержит последовательно включенные модульный блок 30, сумматор 31, блок 32 присвоения знака, первый ключ 33 и сумматор 34, при этом первый вход блока 6 коррекции пределов измерения через второй ключ 35 соединен со вторым входом сумматора 34, выход блока 36 памяти соединен со вторым входом сумматора 31, второй вход блока коррекции пределов измерения соединен с управляющими входами первого 33 и второго 35 ключей, второй вход блока 32 присвоения знака является третьим входом блока коррекции пределов измерения, выход сумматора 34 является его выходом.

Блок 32 присвоения знака (фиг. 8) содержит блоки 37, 40 умножения, блок 38 памяти и ограничитель 39, причем второй вход блока присвоения знака является первым входом блока 37 умножения, второй вход которого соединен с выходом блока 38 памяти, выход блока 37 умножения соединен с входом ограничителя 39, выход которого соединен с первым входом блока 40 умножения, второй вход которого является первым входом блока присвоения знака, выходом блока присвоения знака служит выход блока 40 умножения.

Блок 11 вычисления модуля (фиг. 9) содержат два блока 41 умножения, сумматор 42 и блок 43 извлечения квадратного корня, входами блока вычисления модуля являются входы блоков 41 умножения, выходы которых соединены с первым и вторым входами сумматора 42, выход которого соединен с входом блока 43 извлечения квадратного корня, выход которого является выходом блока вычисления модуля.

Первый 15 и второй 16 двухканальные ключи (фиг. 10) содержат два ключа 44, входами двухканальных ключей являются входы ключей 44, выходы которых являются выходами двухканальных ключей.

Блок 10 управления (фиг. 11) содержит триггер 45 и элемент НЕ 46, входом блока управления является вход триггера 45, выход которого соединен с входом элемента НЕ 46, первым выходом блока 10 управления является выход триггера 45, а вторым выходом - выход элемента НЕ 46.

Вычислитель радиальной скорости движущегося объекта работает следующим образом.

В заявляемом вычислителе обрабатывается неэквидистантная когерентно-импульсная последовательность N радиосигналов с чередующимися периодами повторения T1 и Т2, причем Τ1-Τ2=ΔT. При отражении радиосигналов от движущейся цели их несущие частоты в соответствующих периодах приобретают доплеровские сдвиги фазы

, , ,

где - доплеровская частота, νr - радиальная скорость цели, - несущая частота радиосигналов, с - скорость распространения радиоволн.

Отраженные от цели радиосигналы поступают на вход приемника, в котором усиливаются, в квадратурных фазовых детекторах переносятся на видеочастоту, а затем подвергаются аналого-цифровому преобразованию (соответствующие блоки на фиг. 1 не показаны). На вход вычислителя в одном элементе разрешения по дальности поступают цифровые отсчеты комплексной огибающей

, k=1 … N,

где u1k, u2k - цифровые коды действительной и мнимой частей отсчетов Uk.

Входные отсчеты Uk вычислителя (фиг. 1) в блоке 1 задержки (фиг. 2) под управлением синхронизирующих импульсов, вырабатываемых синхрогенератором 14, поочередно задерживаются на интервалы T1 и T2, что обеспечивает синхронность последующего комплексного умножения отсчетов по дальности. Синхрогенератор 14 управляется импульсами синхронизатора радиолокатора (на фиг. 1 не показан), следующими поочередно с интервалами T1 и Т2. В блоке 2 комплексного сопряжения (фиг. 3) осуществляется комплексное сопряжение задержанного отсчета (). Далее в блоке 3 комплексного умножения (фиг. 4) реализуется попарное умножение отсчетов в соответствии с алгоритмом

Попарные произведения (корреляции) раздельно для каждого интервала T1 и Т2 соответственно через первый 15 и второй 16 двухканальные ключи раздельно поступают в блок 4 усреднения и в дополнительный блок 17 усреднения (фиг. 5). Поочередная коммутация первого 15 и второго 16 двухканального ключей осуществляется импульсами соответственно с первого и второго выходов блока 10 управления, синхронизируемого также импульсами синхронизатора радиолокатора.

В блоке 4 усреднения (фиг. 5) с помощью линий задержки 26 на интервал T1+Т2 и сумматоров 27 в каждом элементе разрешения по дальности осуществляется скользящее вдоль азимута когерентное суммирование (накопление) соответствующих интервалу T1 попарных произведений (корреляций). В результате на выходе блока 4 усреднения при нечетном N образуется пропорциональная корреляционному моменту отсчетов, соответствующих интервалу T1, величина

В дополнительном блоке 17 усреднения (фиг. 5) осуществляется аналогичное суммирование соответствующих интервалу Т2 попарных корреляций, что приводит к образованию на его выходе пропорциональной корреляционному моменту отсчетов, соответствующих интервалу Т2, величины

:

Величина Y1 на выходе блока 4 усреднения (фиг. 5) по времени предшествует величине Y2 на интервал Т2, что компенсируется соответствующей данному интервалу задержкой Y1 в дополнительном блоке 18 задержки (фиг. 2). В дополнительном блоке 19 комплексного сопряжения (фиг. 3) инвертируется знак мнимой части величины Y2.

Величины Y1 и одновременно поступают соответственно на первые и вторые входы дополнительного блока 20 комплексного умножения (фиг. 4), на выходе которого вычисляется величина

Величины ν1 и ν2 поступают на соответствующие входы блока 5 вычисления фазы (фиг. 6), где на основе блока 28 деления и арктангенсного функционального преобразователя 29 вычисляется оценка

.

Последующие преобразования оценки происходят в блоке 6 коррекции пределов измерения (фиг. 7) и зависят от знака ν1. При ν1>0 открыт второй ключ 35, и оценка через сумматор 34 непосредственно поступает на выход блока коррекции пределов измерения. При ν1<0 открыт первый ключ 33, а второй ключ 35 закрыт. При этом в модульном блоке 30 образуется , вычитаемый в блоке 31 из величины π, поступающей от блока 36 памяти. Полученной разности в блоке 32 присваивается знак величины ν2.

Блок 32 присвоения знака (фиг. 8) работает следующим образом. На второй вход блока присвоения знака поступает величина ν2 [соотношение (1)], где в блоке 37 умножения производится ее умножение на постоянный множитель из блока 38 памяти с целью масштабирования и дальнейшего ограничения в ограничителе 39 по уровню ±1. Таким образом, после ограничения величина на выходе ограничителя 39 имеет смысл знака величины ν2, который, поступая на первый вход блока 40 умножения, присваивается разности , поступающей с выхода блока 31 на первый вход блока 32 присвоения знака, т.е. на второй вход блока 40 умножения.

Рассмотренные операции позволяют в блоке 5 вычисления фазы сначала найти оценку доплеровского сдвига фазы, находящуюся в интервале [-π/2, π/2], а затем при помощи блока 6 коррекции пределов измерения расширить пределы ее однозначного измерения до интервала [-π, π] в соответствии с алгоритмом

Умножитель 7 (фиг. 1) осуществляет умножение найденной оценки сдвига фазы на весовой коэффициент а, хранящийся в первом блоке 9 памяти, что позволяет найти однозначную оценку радиальной скорости в соответствии с выражением

где - весовой коэффициент.

Для уменьшения вероятности работы вычислителя по шумам в нем исключается выдача полученной оценки на выход в отсутствие отраженного от цели сигнала. В блоке 11 вычисления модуля (фиг. 9) вычисляется величина

которая поступает на второй вход порогового блока 12, в котором сравнивается с пороговым уровнем z0, записанным во втором блоке 13 памяти. Если происходит превышение порогового уровня z0, то с выхода порогового блока 12 поступает сигнал разрешения на прохождение результата вычисления с выхода блока 7 умножения через ключ 8 на первый выход вычислителя радиальной скорости движущегося объекта. В противном случае ключ 8 разомкнут. Кроме того, сигнал с выхода порогового блока 12, являющегося вторым выходом вычислителя радиальной скорости движущегося объекта, может быть использован для отсчета других координат цели, например дальности.

Синхронизация вычислителя радиальной скорости движущегося объекта осуществляется подачей на все блоки заявляемого вычислителя последовательности синхронизирующих импульсов, вырабатываемых синхронизатором 14 (фиг. 1) с периодом повторения tк, определяемым из условия требуемой разрешающей способности по дальности.

Достижение технического результата объясняется следующим образом. В известном устройстве (прототипе) исходные доплеровские сдвиги фазы ϕ1 и ϕ2, по которым вычисляется величина Δϕ=ϕ1-ϕ2, имеют интервал однозначного измерения [-π, π], что соответствует интервалу однозначного измерения доплеровской частоты [-1/2T1], 1/2T1]] (по величине большего периода Т1). В предложенном устройстве величина Δϕ измеряется непосредственно, что соответствует интервалу однозначности доплеровских частот [-1/2ΔT, 1/2ΔT]. При этом интервал однозначного измерения доплеровской частоты и, следовательно, радиальной скорости расширяется в T1/ΔT раз, что соответствует решению поставленной задачи изобретения. Если в соответствии с условием и с учетом для максимально возможной скорости движущегося объекта νr max выбрать интервал , то во всем диапазоне реальных скоростей движущегося объекта может быть осуществлено их однозначное измерение. При этом сохраняется однозначность измерения дальности, которая обеспечивается соответствующим выбором меньшего периода повторения импульсов Т2.

Обусловленные функциональными преобразованиями погрешности раздельного вычисления величин ϕ1 и ϕ2 являются статистически независимыми. В результате погрешность (дисперсия) разности ϕ1-ϕ2=Δϕ удваивается. В предложенном вычислителе при непосредственном вычислении величины Δϕ такое удвоение отсутствует, что соответствует повышению точности измерения.

Таким образом, вычислитель радиальной скорости движущегося объекта позволяет расширить диапазон однозначно измеряемой радиальной скорости и повысить точность измерения за счет меньшего числа функциональных преобразований при применении предлагаемой совместной обработки неэквидистантных когерентно-импульсных радиосигналов.

Библиография

1. Ширман Я.Д. и Манжос В.Н. Теория и техника обработки радиолокационной информации на фоне помех. - М.: Радио и связь. - 1981. - С. 204. - Рис. 14.2.

2. Патент №63-49193 (Япония), МПК G01S 13/52. Радиолокационное устройство для обнаружения движущейся цели / К.К. Тосиба. Опубл. 03.10.1988. - Изобретения стран мира. - 1989. - Выпуск 109. - №15. - С. 52.

3. Патент №2017167 (Россия), МПК G01S 13/58. Обнаружитель-измеритель доплеровских сигналов / Д.И. Попов, C.B. Герасимов и Е.Н. Матаев. Опубл. 30.07.1994. - Изобретения. - 1994. - №14. - С. 121.

Вычислитель радиальной скорости движущегося объекта, содержащий блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения, блок вычисления фазы, блок коррекции пределов измерения, умножитель, ключ, первый блок памяти, блок управления, блок вычисления модуля, пороговый блок, второй блок памяти и синхрогенератор, при этом выходы блока задержки соединены с входами блока комплексного сопряжения, выходы которого соединены с первыми входами блока комплексного умножения, вторые входы которого объединены с входами блока задержки, выход первого блока памяти соединен с первым входом умножителя, выход которого соединен с входом ключа, выход порогового блока соединен с управляющим входом ключа, первый вход порогового блока соединен с выходом второго блока памяти, выход синхрогенератора соединен с синхровходами блока задержки, блока комплексного сопряжения, блока комплексного умножения, блока усреднения, блока вычисления фазы, умножителя, ключа, блока вычисления модуля, первого и второго блоков памяти, блока коррекции пределов измерения и порогового блока, отличающийся тем, что введены первый и второй двухканальные ключи, дополнительный блок усреднения, дополнительный блок задержки, дополнительный блок комплексного сопряжения и дополнительный блок комплексного умножения, при этом выходы блока комплексного умножения соединены с объединенными входами первого и второго двухканальных ключей, управляющие входы которых соединены соответственно с первым и вторым выходами блока управления, выходы первого двухканального ключа соединены с входами блока усреднения, выходы которого соединены с входами дополнительного блока задержки, выходы второго двухканального ключа соединены с входами дополнительного блока усреднения, выходы которого соединены с входами дополнительного блока комплексного сопряжения, выходы дополнительного блока задержки соединены с первыми входами дополнительного блока комплексного умножения, вторые входы которого соединены с выходами дополнительного блока комплексного сопряжения, выходы дополнительного блока комплексного умножения соединены с входами блока вычисления фазы, блока вычисления модуля, вторым и третьим входами блока коррекции пределов измерения, выход которого соединен со вторым входом умножителя, выход блока вычисления модуля соединен со вторым входом порогового блока, выход синхрогенератора соединен с синхровходами первого и второго двухканальных ключей, дополнительного блока усреднения, дополнительного блока задержки, дополнительного блока комплексного сопряжения и дополнительного блока комплексного умножения, причем входами вычислителя радиальной скорости движущегося объекта являются входы блока задержки, а первым и вторым выходами - соответственно выходы ключа и порогового блока.